4 4

00

00 0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программируемой задержки информации | 1986 |

|

SU1394213A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Устройство для обмена информацией между объектом контроля и электронной вычислительной машиной | 1983 |

|

SU1156078A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| УСТРОЙСТВО ПОИСКА ПРОИЗВОЛЬНЫХ ВХОЖДЕНИЙ | 2001 |

|

RU2202823C2 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Устройство предварительной выборки команд | 1987 |

|

SU1561073A1 |

W

и.

Изобретение относится к вычислительной технике и может быть применено для подготовки данных в устройствах цифровой обработки сигналов в реальном масштабе времени.

Целью изобретения является увелу- чение быстродействия.

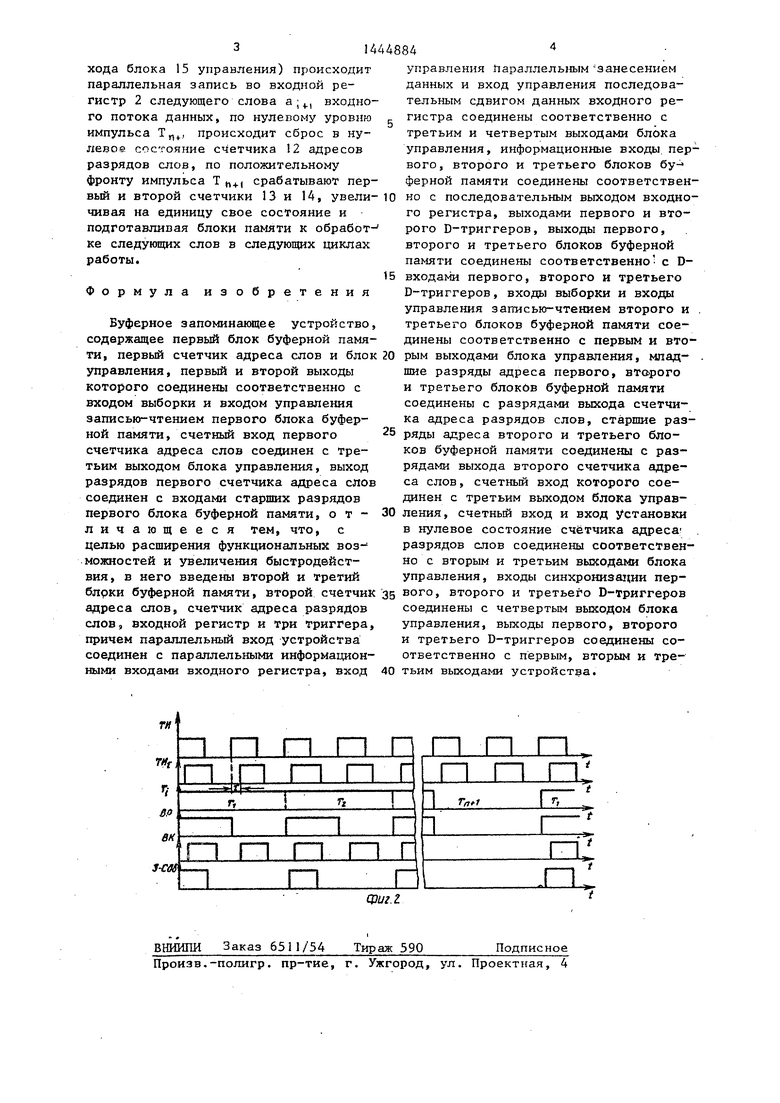

На фиг.1 приведена функциональная схема устройства; на фиг.2 - временная диаграмма работы блока управления.

Устройство содержит параллельный вход 1, входной регистр 2, первые блок 3 буферной памяти и D-триггер 4, вторые блок 5 буферной памяти и &- триггер 6, третьи блок 7 буферной памяти и D-триггеров 8, три последовательных выхода 9-П, счетчик 12 адресов разрядов слов, два сче гчика ад- 20 из двух полутактов.

30

ресов слов 13, 14 и блок 15 управления. Блок 15, состоит из генератора 16 тактовых импульсов, элемента 17 задержки б для формирования задержанных тактовых импульсов ТИ, счетчика 25 18 на 2 (п+1), дешифратора 19 (п-И)Го такта Т , и трех элементов И 20, формируняцих управляющие сигналь : ВК (выбор кристалла), ВР (выбор режима) и 3-Сдв (запись в D-триггеры и сдвиг

во входном регистре 2).

I

Устройство работает следуннцим образом.

Блоки 3, 5 и 7 памяти магазинного типа реализованы на запоминающих устройствах с произвольной выборкой и предназначены для записи в последовательном коде текущих величин п-раз- рядных слов а; входного потока данных и вьщачи на выход устройства в последовательном коде величин трех задержанных и сдвинутых относительно друг друга слов а- , , .

35

40

В первом полутакте первого такта цикла по положительному фронту ynpaia ляющего импульса 3-Сдв (с. четвертого выхода блока 15 управления) происхо дит сдвиг информации во входном регистре 2 с вьщачей на его последовательной выход первого разряда слова а|, по единичному уровню импульса ВР (с второго выхода блока 15 управления) и импульсу ВК (с первого выхода блока 15 управления), считывание и далее запись первых разрядов слов

i+k .Vk4.«« по отрицатель-, ному перепаду импульса 3-Сдв соответ- ственно в первьй 4, второй б и третий 8 выходные D-триггеры и выдача их с выходов D-триггеров на выходы - 9, JO и 11 устройства.

Во втором полутакте первого такта 1Щ,кла по нулевому уровню импульса ВР и импульсу ВК происходит запись с последовательного выхода входного регистра 2 и с вЬгходов первого 4 и второго 6 выходных D-триггеров первых

Объем второго и третьего блоков памя- разрядов соответственно слов aj, ,,

ги 5, 7 составляет по 1 п-разрядных слов, т.е. по 1 к п одноразрядных ячеек. Первый блок 3 памяти объ- емом k X г одноразрядных ячеек предназначен дпя выравнивания во времени выходной информации нескольких параллельных и синхронных потоков данных при использовании такого же числа предлагаемых устройств. Принцип работы блоков 3,5 и 7 буферной памяти основан на циклическом выполнении считывания одного разряда соответственно слов (, , а J4.U+2.C и записи в освободившиеся

50

5

освободившиеся в первом полутакте ячейки соответственно первого, второго и третьего блоков памяти 3, 5 и 7, по положительному фронту импульса ВР срабатывает счетчик 12 разрядов слов, увеличивая на единицу адрес ячеек всех трех блоков памяти Второй и цоследугзщие до п-го включительно такты цикла выполняются аналогично первому тактуS при этом обрабатываются соответстзекнг со второго по п-й разряды тех же слов

В (п+1)-м такте по отрицательному фронту импульса Т,.) (с третьего выячейки того же разряда соответственно слов а. , в) , .

Адрес первого блока 3 памяти формируется двумя циклически работающими счетчиками: счетчиком 12 адресов разрядов слов (младшая часть адреса-, определякщая разряды слов) и первым счетчиком 13 адресов слов (старшая часть адреса, определяющая непосредственно слова). Адреса второго и третьего блоков 4 и 5 памяти формц руются также двумя циклически работающими счетчиками; счетчиком 12 ад

ресов разрядов слов (младшая часть адреса) и вторым счетчиком 14 адресов слов (старшая часть адреса). Цикл записи-считывания слов состоит из п+1 тактов. Каждый такт состоит

0

5

5

0

В первом полутакте первого такта цикла по положительному фронту ynpaia ляющего импульса 3-Сдв (с. четвертого выхода блока 15 управления) происхо дит сдвиг информации во входном регистре 2 с вьщачей на его последовательной выход первого разряда слова а|, по единичному уровню импульса ВР (с второго выхода блока 15 управления) и импульсу ВК (с первого выхода блока 15 управления), считывание и далее запись первых разрядов слов

i+k .Vk4.«« по отрицатель-, ному перепаду импульса 3-Сдв соответ- ственно в первьй 4, второй б и третий 8 выходные D-триггеры и выдача их с выходов D-триггеров на выходы - 9, JO и 11 устройства.

Во втором полутакте первого такта 1Щ,кла по нулевому уровню импульса ВР и импульсу ВК происходит запись с последовательного выхода входного регистра 2 и с вЬгходов первого 4 и второго 6 выходных D-триггеров первых

0

5

освободившиеся в первом полутакте ячейки соответственно первого, второго и третьего блоков памяти 3, 5 и 7, по положительному фронту импульса ВР срабатывает счетчик 12 разрядов слов, увеличивая на единицу адрес ячеек всех трех блоков памяти Второй и цоследугзщие до п-го включительно такты цикла выполняются аналогично первому тактуS при этом обрабатываются соответстзекнг со второго по п-й разряды тех же слов

В (п+1)-м такте по отрицательному фронту импульса Т,.) (с третьего выхода блока 15 управления) происходит параллельная запись во входной регистр 2 следующего слова а;., входного потока данных, по нулевому уровню импульса Т„, происходит сброс в нулевое состояние счетчика 2 адресов разрядов слов, по положительному фронту импульса Т срабатывают перуправлення Параллельным занесением данных и вход управления последовательным сдвигом данных входного регистра соединены соответственно с третьим и четвертым выходами блока управления, информационные входы, первого, второго и третьего блоков бу- ферной памяти соединены соответственвый и второй счетчики 13 и 14, увели- 10 но с последовательным выходом входно чивая на единицу свое состояние и го регистра, выходами первого и вто- подготавливая блоки памяти к обработрого D-триггеров, выходы первого, второго и третьего блоков буферной памяти соединены соответственно с D- 15 входами первого, второго и третьего D-триггеров, входы выборки и входы управления записью-чтением второго и

Буферное запоминакнцее устройство, третьего блоков буферной памяти сое- содержащее первый блок буферной памя- динены соответственно с первым и вто- ти, первый счетчик адреса слов и блок 20 рым выходами блока управления, мпадке следующих слов в следующих циклах работы.

Формула изобретения

управления, первый и второй выходы которого соединены соответственно с входом выборки и входом управления записью-чтением первого блока буферной памяти, счетный вход первого счетчика адреса слов соединен с третьим выходом блока управления, выход разрядов первого счетчика адреса слов соединен с входами старших разрядов первого блока буферной памяти, отличающееся тем, что, с целью расширения функциональных воз- можностей и увеличения быстродействия, в него введены второй и третий

шие разряды адреса первого, второго и третьего блокбв буферной памяти соединены с разрядами выхода счетчика адреса разрядов слов, старшие раз25 ряды адреса второго и третьего блоков буферной памяти соединены с разрядами выхода второго счетчика адреса слов, счетный вход которого соединен с третьим выходом блока управ30 ления, счетный вход и вход Установки в нулевое состояние счётчика адреса разрядов слов соединены соответственно с вторым и третьим выходами блока

управления, входы синхронизации пер- блрки буферной памяти, второй счетчик 35 вого, второго и третьего D-триггеров адреса слов, счетчик адреса разрядов соединены с четвертым выходом блока слов, входной регистр и три триггера, управления, выходы первого, второго причем параллельный вход устройства и третьего D-триггеров соединены со- соединен с параллельными информацион- ответственно с первым, вторым и тре- ными входами входного регистра, вход 40 тьим выходами устройства.

ВНИИПИ Заказ 6511/54 Тираж 590

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

управлення Параллельным занесением данных и вход управления последовательным сдвигом данных входного регистра соединены соответственно с третьим и четвертым выходами блока управления, информационные входы, первого, второго и третьего блоков бу- ферной памяти соединены соответственно с последовательным выходом входно го регистра, выходами первого и вто-

шие разряды адреса первого, второго и третьего блокбв буферной памяти соединены с разрядами выхода счетчика адреса разрядов слов, старшие раз25 ряды адреса второго и третьего блоков буферной памяти соединены с разрядами выхода второго счетчика адреса слов, счетный вход которого соединен с третьим выходом блока управ30 ления, счетный вход и вход Установки в нулевое состояние счётчика адреса разрядов слов соединены соответственно с вторым и третьим выходами блока

Подписное

Авторы

Даты

1988-12-15—Публикация

1987-07-08—Подача