4;;

4: 4i

00

(puZ,i.

15 1

Изобретение отрюсится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств (ВЗУ) системы сбора и обработки измерительной информации.

Цель изобретения - расширение области применения устройства за счет управления скоростью считывания данных из накопителя.

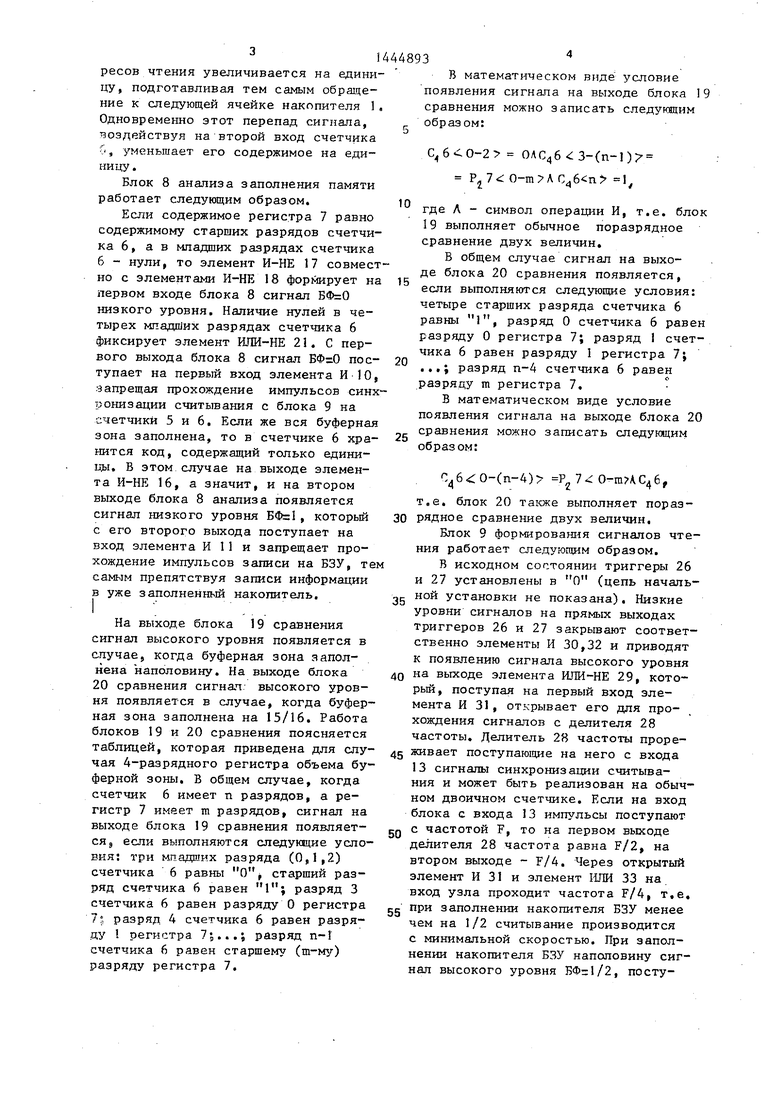

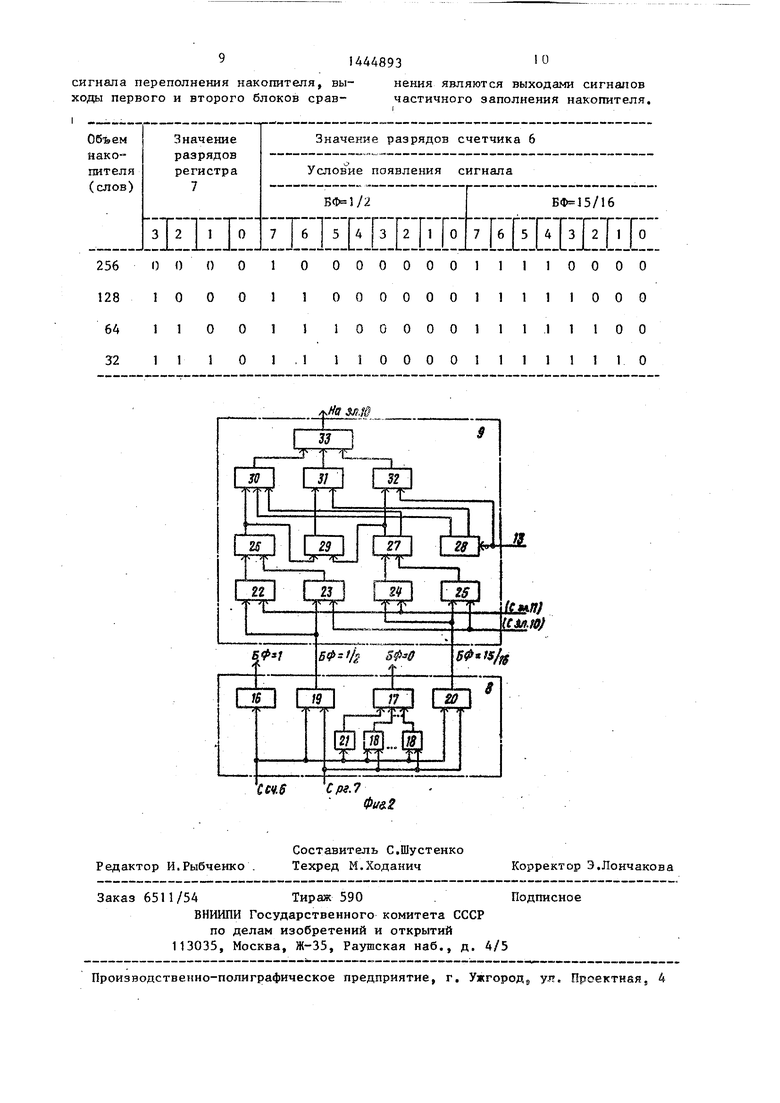

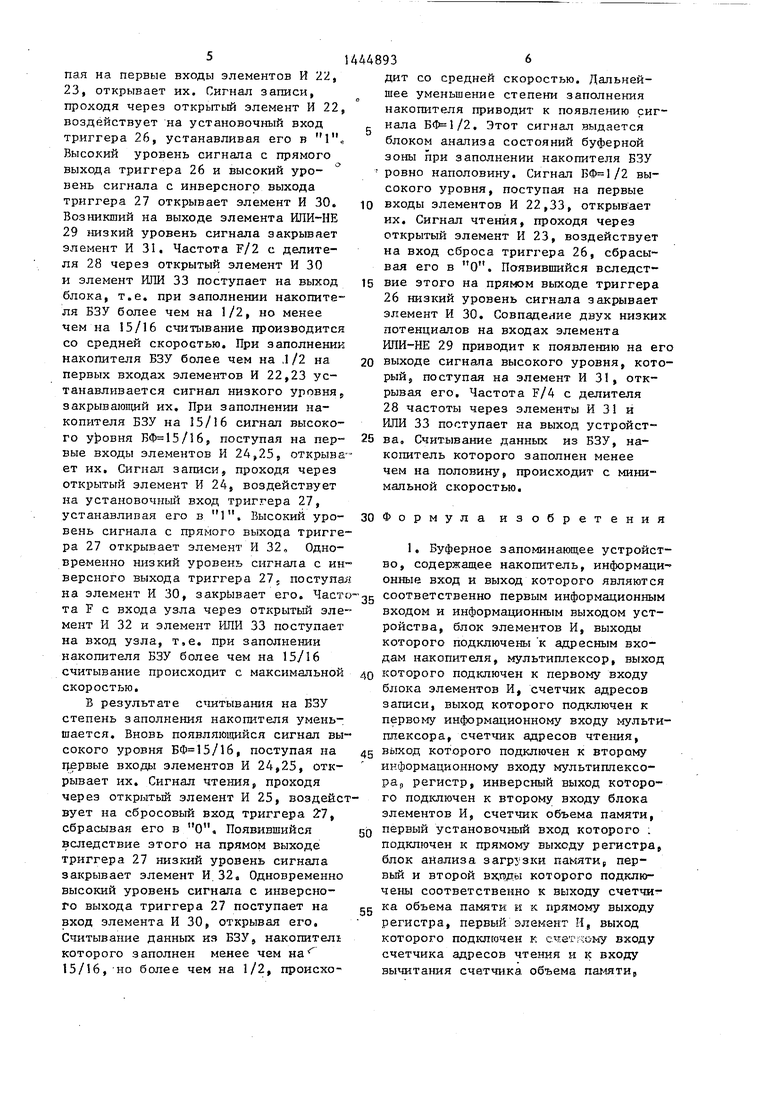

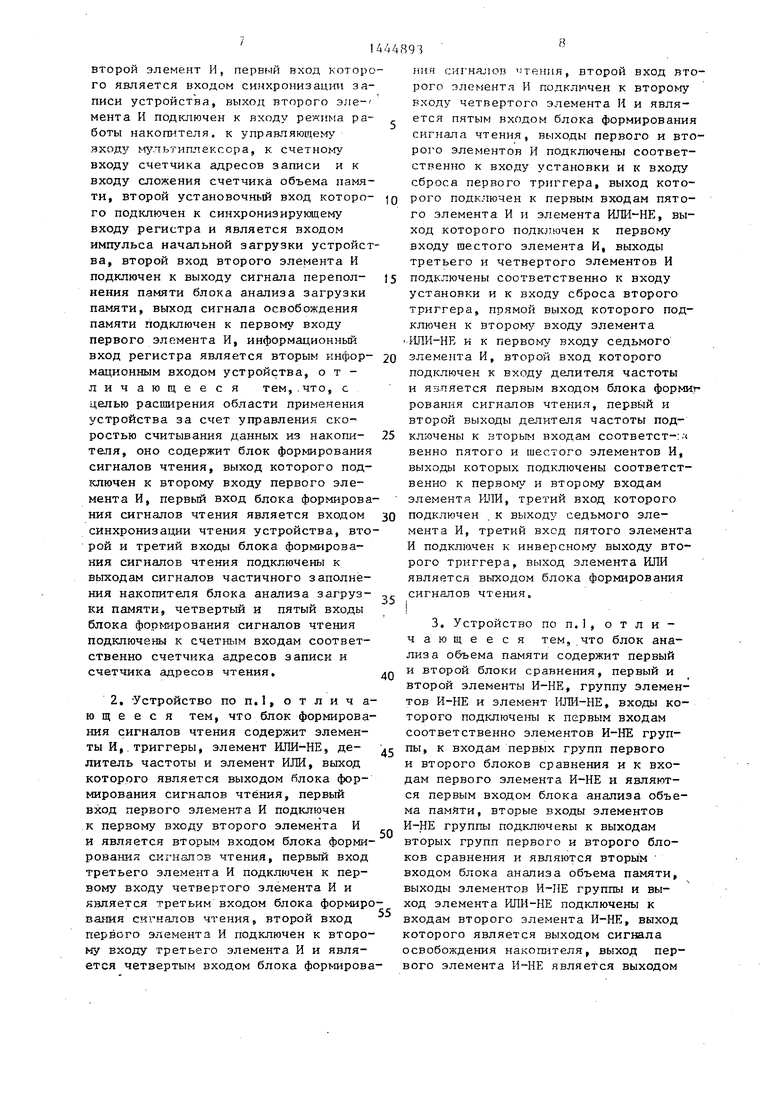

На фиг.1 представлена структурная схема предлагаемого БЗУ; на фиг,2 - блок-схемы блока формирования сигналов чтения и блока анализа загрузки памяти.

Устройство содержит накопитель 1, блок 2 элементов И, мультиппексор 3, счетчик 4 адресов записи, счетчик 5 адресов чтения, счетчик 6 объема памяти, регистр 7, блок 8 анализа загрузки памяти, блок 9 формирования сигналов чтения, элементы И 10 и И, вход.12 синхронизации записи, вход 13 синхронизации чтения, информационный вход 14 и вход 15 начальной загрузки.

Блок 8 анализа загрузки памяти содержит элементы И-НЕ 1&, 17 и 18, блоки 19 и 20 сравнения и элемент Щ1И-НЕ 21, Блок 9 формирования сигналов чтения содержит элементы И 22- 25, триггеры 26 и 27, делитель 28 частоты, элемент ИЛИ-НЕ 29, элементы И 30-32 и элемент ИЛИ 33.

Устройство работает следующим образом.

Перед началом работы счетчики 4, 5,6 и триггеры блока 9 сбрасываются в О, Цепь начальной установки не показана. В регистр 7 записывается двоичный код объема буферной зоны Код поступает на вход 14 и записывается импульсом, подаваемым на вход 15, Код в регистре 7 объема буферной зоны представляет собой последовательность единиц, начиная со старшего разряда, причем если число единиц равно К, то объем буферной зоны равен , где п - разрядность счетчиков 4-6, Очевидно, что разрядность регистра 7 должна быть несколько меньше разрядности счетчика 6, Примем, что в системе сбора и обработки измерительной информации минимальный объем БЗУ равен 16, поэтому счетчики 4-6 имеют разрядность на 4 разряда ,больше, чем регистр 7, По заднему фронту импульса на входе 15

код из регистра 7 объема буферной зоны переписывается в старшие разряды счетчика 6, а младшие четыре - разряда счетчика 6 заносятся нули. Код с инверсных выходов регистра 7 поступает на вторые входы блока 2 элементов И, маскируя те разряды счетчика 4 адреса записи или счетчи0 ка 5 адреса чтения, которым в одноименных разрядах регистра 7 буферной зоны соответствует единицы.

В режиме записи информации на шине 12 синхронизации записи устанав5 ливается сигнал высокого уровня. Проходя через открытый при неполностью заполненном накопителе элемент И 11, этот сигнал воздействует на управляняций вход накопителя 1 , пере0 водя его в режим записи. Одновременно этот же сигнал воздействует на третий вход мультиплексора 3, подключая к первым входам блока 2 элементов И промаскированный код адре5 са, который поступая на входы накопителя 1, выбирает для записи соответствующую ячейку. По окончании записи сигнал на шине 12 синхрони- зации записи сбрасывается. Возникший перепад сигнала на выходе зле0

5

0

5

0

5

мента И 11, воздействуя на вход счетчика 4 адреса записи, увеличивает его содержимое на единицу. Одновременно этот перепад сигнала, воздействуя на третий вход счетчика 6 объема буферной зоны, увеличивает его содер кимое на единицу.

В режиме чтения информации сигнал низкого уровня на шике 12 запирает элемент И 11, что приводит к формированию сигнала низкого уровня на его выходе, который, воздействуя на управляющий вход накопителя 1, переводит его в режим чтения. Одновременно этот сигнал воздействует на третий вход мультиплексора 3, : подключая к первым входам блока 2 элементов И выходы счетчика 5 адреса чтения, С выходов блока 2 элементов И промаскированньй код адреса поступает,на адресате входы накопителя 1, выбирая для чтегшя соответствующую ячейку. На выходкь х шинах на- копителя появляется информация из выбранной ячейки. Сигнал высокого уровня на шине 13 скнхрошгзации чтения проходит через блок S и открытый элемент И 10, По задне1гу фронту этого сигнала содержимое счетчика 5 ад3U44893

ресов чтения увеличивается на единицу, подготавливая тем самым обращение к следующей ячейке накопителя 1 Одновременно этот перепад сигнала, воздействуя на второй вход счетчика Г , уменьшает его содержимое на единицу.

Блок 8 анализа заполнения памяти работает следующим образом.

Если содержимое регистра 7 равно содержимому старших разрядов счетчика 6, а в младших разрядах счетчика б - нули, то элемент И-НЕ 17 совмест но с элементами И-НЕ 18 формирует н первом входе блока 8 сигнал низкого уровня. Наличие нулей в четырех младших разрядах счетчика 6 фиксирует элемент ИЛИ-НЕ 21. С первого выхода блока 8 сигнал поступает на первый вход элемента И 10 .-запрещая прохождение импульсов синх ионизации считывания с блока 9 на счетчики 5 и 6. Если же вся буферная зона заполнена, то в счетчике 6 хранится код, содержащий только единицу. В этом случае на выходе элемента И-НЕ 16, а значит, и на втором выходе блока 8 анализа появляется сигнал низкого уровня Bfcl, которьш с его второго выхода поступает на вход элемента И 11 и запрещает прохождение импульсов записи на БЗУ, те самым препятствуя записи информации в уже заполненный накопитель.

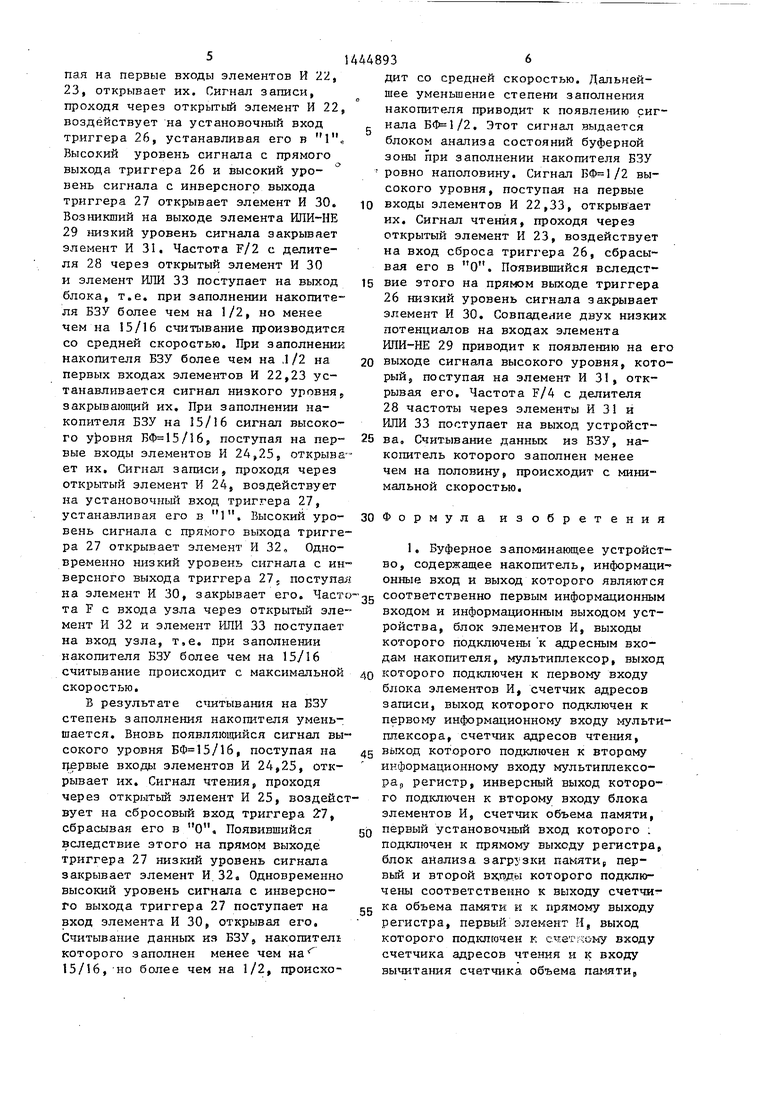

На выходе блока 19 сравнения сигнал высокого уровня появляется в случае, когда буферная зона заполнена наполовину. На выходе блока 20 сравнения сигнач высокого уровня появляется в случае, когда буферная зона заполнена на 15/16. Работа блоков 19 и 20 сравнения поясняется таблицей, которая приведена для случая 4-разрядного регистра объема буферной зоны, В общем случае, когда счетчик 6 имеет п разрядов, а регистр 7 имеет m разрядов, сигнал на выходе блока 19 сравнения появляется если выполняются следумцие условия три мпадших разряда (0,1,2) счетчика 6 равны 0 старший разряд счетчика 6 равен разряд 3 счетчика 6 равен разряду О регистра 75 разряд 4 счетчика 6 равен разряду регистра ...; разряд п-1 счетчика 6 равен старшему (т-му) разряду регистра 7.

В математическом виде условие появления сигнала на выходе блока 19 сравнения можно записать следукщим образом:

ОЛС4б :3-(п-1) PJ, 1

5

0

5

0

5

0

0

где Л - символ операции И, т.е. блок I9 выполняет обычное поразрядное сравнение двух величин.

В общем случае сигнал на выходе блока 20 сравнения появляется, если выполняются следующие условия: четыре старших разряда счетчика 6 равны 1, разряд О счетчика 6 равен разряду О регистра 7; разряд 1 счетчика 6 равен разряду I регистра 7; ...; разряд п-4 счетчика 6 равен разряду m регистра 7.

В математическом виде условие появления сигнала на выходе блока 20 сравнения можно записать следующим образом:

(п-4) Р27 0-тМС4б,

т.е. блок 20 также выполняет поразрядное сравнение двух величин.

Блок 9 формирования сигналов чтения работает следующим образом.

В исходном состоянии триггеры 26 и 27 установлены в О (цепь начальной установки не показана). Низкие уровни сигналов на прямых выходах триггеров 26 и 27 закрывают соответственно элементы И 30,32 и приводят к появлению сигнала высокого уровня на выходе элемента ИЛИ-НЕ 29, который, поступая на первый вход элемента И 31, открывает его для прохождения сигналов с делителя 28 частоты. Делитель 28 частоты проре5 живает поступающие на него с входа 13 сигналы синхронизации считывания и может быть реализован на обычном двоичном счетчике. Если на вход блока с входа 13 импульсы поступают с частотой F, то на первом выходе делителя 28 частота равна F/2, на втором выходе - F/4. Через открытый элемент И 31 и элемент ИЛИ 33 на вход узла проходит частота F/4, т.е.

С при заполнении накопителя БЗУ менее чем на 1/2 считывание производится с минимальной скоростью. При заполнении накопителя БЗУ наполовину сигнал высокого уровня , посту0

пая на первые входы элементов И 2.2 23, открывает их. Сигнал записи, проходя через открьп ый элемент И 22, воздействует на установочный вход триггера 26, устанавливая его в « Высокий уровень сигнала с прямого выхода триггера 26 и высокий уро- вень сигнала с инверсного выхода триггера 27 открывает элемент И 30. Возникший на выходе элемента ИПИ-НЕ 29 низкий уровень сигнала закрывает элемент И 31, Частота F/2 с делителя 28 через открытый элемент И 30 и элемент ИЛИ 33 поступает на выход блока, т.е. при заполнении накопителя БЗУ более чем на 1/2, но менее чем на 15/16 считывание производится со средней скоростью. При заполнении накопителя БЗУ более чем на .1 /2 на первых входах элементов И 22,23 устанавливается сигнал низкого уровня закрывающий их. При заполнении накопителя БЗУ на 15/16 сигнал высоко- го у эовня БФ 15/16, поступая на пер вые входы элементов И 24,25, открывает их. Сигнал записи, проходя через открытый элемент И 24, воздействует на установочный вход триггера 27, устанавливая его в 1, Высокий уро- вень сигнала с прямого выхода триггера 27 открывает элемент И 32, Одновременно низкий уровень сигнала с инверсного выхода триггера 27; поступая на элемент И 30, закрывает его. Част та F с входа узла через открытый элемент И 32 и элемент ИЛИ 33 поступает на вход узла, т.е. при заполнении накопителя БЗУ более чем на 15/16 считывание происходит с максимальной скоростью.

В результате считывания на БЗУ степень заполнения накопителя уменьшается. Вновь появляющийся сигнал высокого уровня БФ 15/16, поступая на цврвые входы элементов И 24,25, открывает их. Сигнал чтения, проходя через открытьй элемент И 25, воздейсвует на сбросовый вход триггера 27, сбрасывая его в О, Появивщийся

вследствие этого на прямом выходе триггера 27 низкий уровень сигнала закрывает элемент И.32« Одновременно высокий уровень сигнала с инверсного выхода триггера 27 поступает на вход элемента И 30, открывая его. Считывание данных из БЗУ, накопител которого заполнен менее чем на 15/16, но более чем на 1/2, происходит со средней скоростью, Дальней- щее уменьшение степени заполне тая накопителя приводит к появлению сигнала . Этот сигнал выдается блоком анализа состояний буферной зоны при заполнении накопителя БЗУ ровно наполови гу. Сигнал высокого уровня, поступая на первые входы элементов И 22,33, открывает их. Сигнал чтения, проходя через открытый элемент И 23, воздействует на вход сброса триггера 26, сбрасывая его в О, Появившийся вследствие этого на пряьюм выходе триггера 26 низкий уровень сигнала закрывает элемент И 30. Совпадение двух низких потенциалов на входах элемента ШИ-НЕ 29 приводит к появлению на ег выходе сигнала высокого уровня, который, поступая на элемент И 31, открывая его. Частота F/4 с делителя 28 частоты через элементы И 31 и ИЛИ 33 поступает на выход устройства. Считывание данных из БЗУ, накопитель которого заполнен менее чем на половину, происходит с минимальной скоростью.

Формула изобретения

1. Буферное запоминающее устройство, содержащее накопитель, информаци онные вход и выход которого являются соответственно первым информационным входом и информационным выходом устройства, блок элементов И, выходы которого подключены к адресным входам накопителя, мультиплексор, выход которого подключен к первому входу блока элементов И, счетчик адресов записи, выход которого подключен к первому информационному входу мультиплексора, счетчик адресов чте1шя, выход которого подключен к второму информационному входу мультиплексора р регистр, инверсный выход которого подключен к второму входу блока элементов И, счетчик объема памяти, первый установочный вход которого : подключен к прямому выходу регистра, блок анализа загрузки памяти пер- вьш и второй вх,вды которого подключены соответственно к выходу счетчика объема памятрг и к прямому выходу регистра, первый элемент И, выход которого подключен к сче грчому входу счетчика адресов чтения и к входу вычитания счетчика объема памяти.

14.44893

элемент И, первый вход которояется входом синхроиизацт застройства, выход второго эле- И подключен к входу режима раакопителя, к управляющему мультиплексора, к счетному счетчика адресов записи и к сложения счетчика объема памяорой установочный вход котороключен к синхронизируклцему регистра и является входом са начальной загрузки устройсторой вход второго элемента И чен к выходу сигнала переполпамяти блока анализа загрузки

10

5

ни ро вх ет си ро ст сб ро го хо вх тр по ус тр кл ИЛ эл по и ро вт кл ве вы ве эл по ме И ро яв си

памяти, выход сигнала освобождения памяти подключен к первому входу первого элемента И, информационный вход регистра является вторым информационным входом устройства, о т - лич ающе е с я тем,.что, с целью расширения области применения устройства за счет управления скоростью считывания данных из накопителя, оно содержит блок формирования сигналов чтения, выход которого подключен к второму входу первого элемента И, первый вход блока формирования сигналов чтения является входом синхронизации чтения устройства, второй и третий входы блока формирования сигналов чтения подключены к выходам сигналов частичного заполнения накопителя блока анализа загрузки памяти, четвертый и пятый входы блока фop иpoвaния сигналов чтения подключены к счетным входам соответственно счетчика адресов записи и счетчика адресов чтения,

2, -Устройство по П.1, о т л и ч а- ю щ 8 е с я тем, что блок формирования сигналов чтения содержит элементы И, . триггеры, элемент ИЛИ-НЕ, делитель частоты и элемент ИЛИ, выход которого является выходом блока формирования сигналов чтения, первый вход первого элемента И подключен к первому входу второго элемента И и является вторым входом блока форми- poBai-шл сигналов чтения, первый вход третьего элемента И подключен к первому входу четвертого элемента И и является третьим входом блока формирования сигналов чтения, второй вход первого элемента И подключен к второму входу третьего элемента И и является четвертым входом блока формирова

0

5

0

5

О Q

ния сигналов 15тен11я, второй вход второго элементя И подключен к второму входу четвертого элемента И и является пятым входом блока формирования сигнала чтения, выходы первого и второго элементов И подключены соответственно к входу установки и к входу сброса первого триггера, выход которого подключен к первым входам пятого элемента И и элемента ИЛИ-НЕ, выход которого подключен к первому входу шестого элемента И, выходы третьего и четвертого элементов И подключены соответственно к входу установки и к входу сброса второго триггера, прямой выход которого подключен к BTOpoMS входу элемента ИЛИ-НЕ и к первому входу седьмого элемента И, второй вход которого подключен к входу делителя частоты и является первым входом блока формиг- рования сигналов чтения, первый и второй выходы делителя частоты подключены к вторьм входам соответст-:- венно пятого и шестого элементов И, выходы которых подключены соответственно к первому и второму входам элементя ИЛИ, третий вход которого подключен к выходу седьмого элемента И, третий вход пятого элемента И подклгачен к инверсному выходу второго триггера, в 51ход элемента ИЛИ является выходом блока формирования сигналов чтения.

3. Устройство по п.1, отличающееся тем,.что блок анализа объема памяти содержит первый и второй блоки сравнения, первый и второй элементы И-НЕ, группу элементов И-НЕ и элемент 1ШИ-НЕ, входы которого подключены к первым входам соответственно элементов И-НЕ груп- 5 пы, к входам nepBbix групп первого и второго блоков сравнения и к входам первого элемента И-НЕ и являются первым входом блока анализа объема памяти, вторые входы элементов И-НЕ группы подключекы к выходам вторых групп первого и второго блоков сравнения и являются вторым входом блока анализа объема памяти, выходы элементов И-ИЕ группы и выход элемента ИЛИ-НЕ подключены к входам второго элемента И-НЕ, выход которого является выходом сигнала освобождения накопителя, выход первого элемента И-НЕ является выходом

5

0

сигнала переполнения накопителя, выходы первого и второго блоков сравнения являются выходами сигналов частичного заполнения накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278981A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств системы сбора и обработки измерительной информации. Цель изобретения - расширение области применения устройства ,а счет управления скоростью считывания данных из накопителя. Устройство содержит накопитель 1, блок 2 элементов И, мультиплексор 3, счетчик 4 адресов записи, счетчик 5 адресов чтения, счетчик 6 объема памяти, регистр 7, блок 8 анализа загрузки памяти, блок 9 формирования сигналов чтения, элементы И 10, 11, Использование изобретения в системах сбора и обработки измерительной информации за счет управления скоростью считывания данных из накопителя позволяет резко снизить объем буфера приемных устройств обработки. 2 з.п..ф-лы, 2 ил. , 1 т абл. i (Л

Авторы

Даты

1988-12-15—Публикация

1987-04-27—Подача