Изобретение относится к вычислительной технике и может быть использовано для имитации информационных сигналов на входах цифровых устройств при их автономной настройке, проверке работоспособности и диагностировании неисправностей.

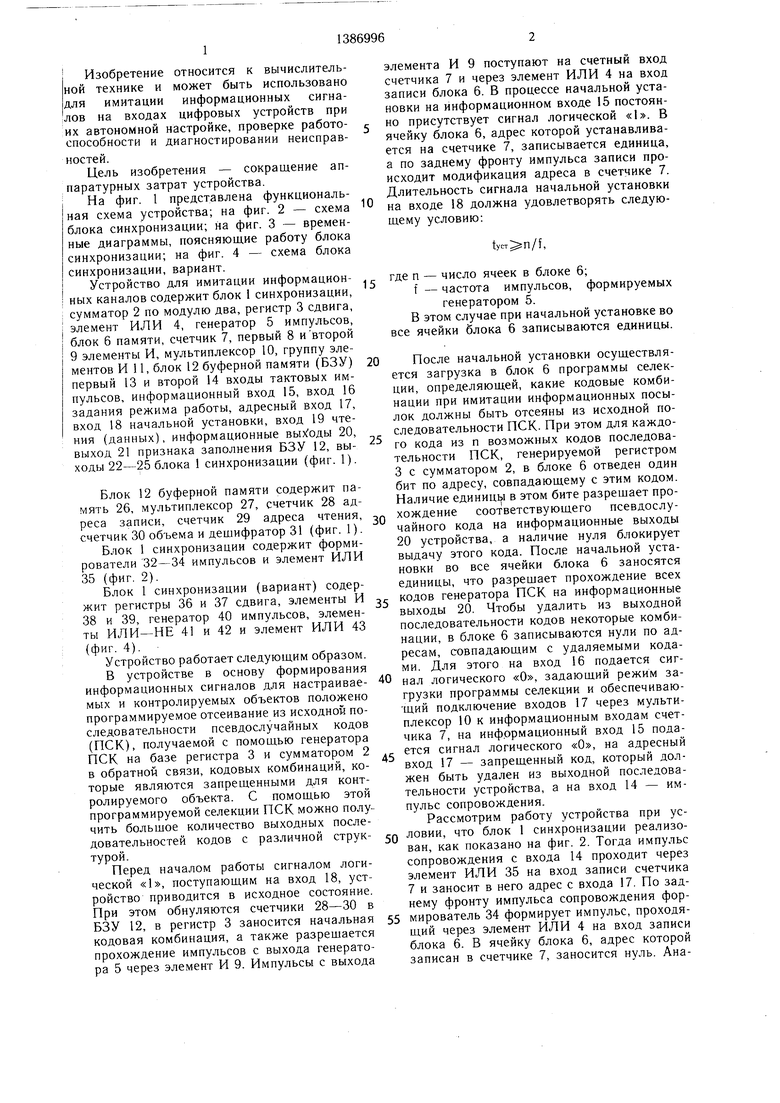

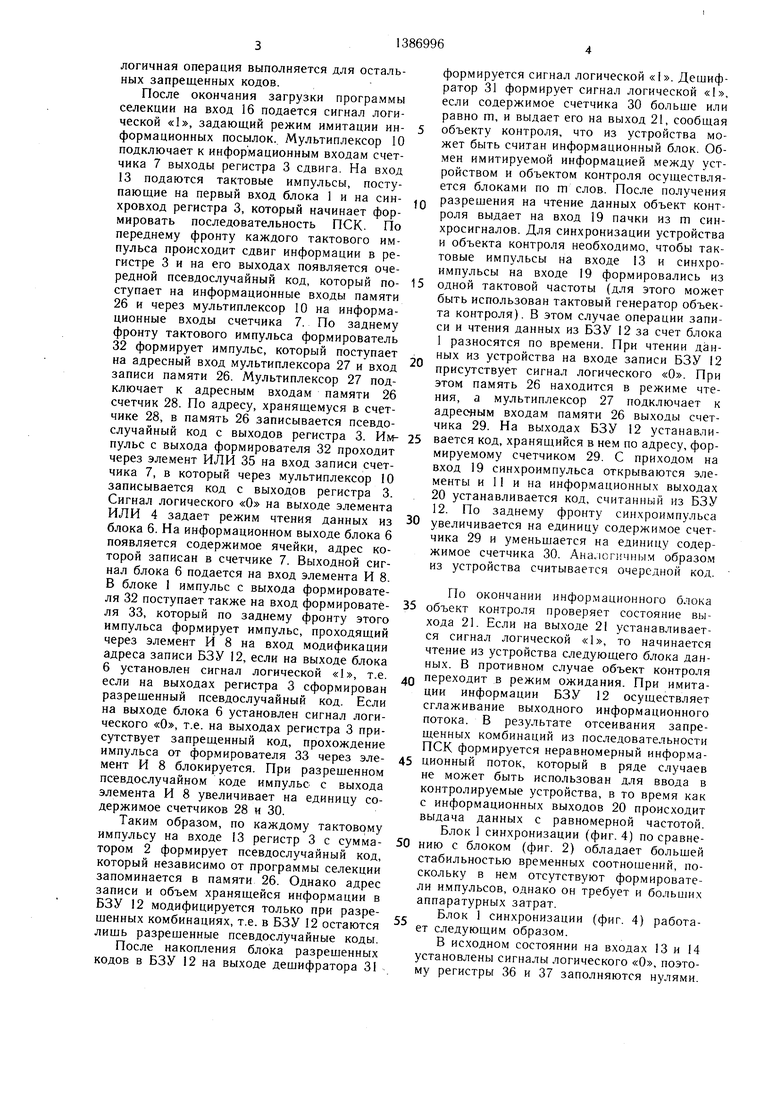

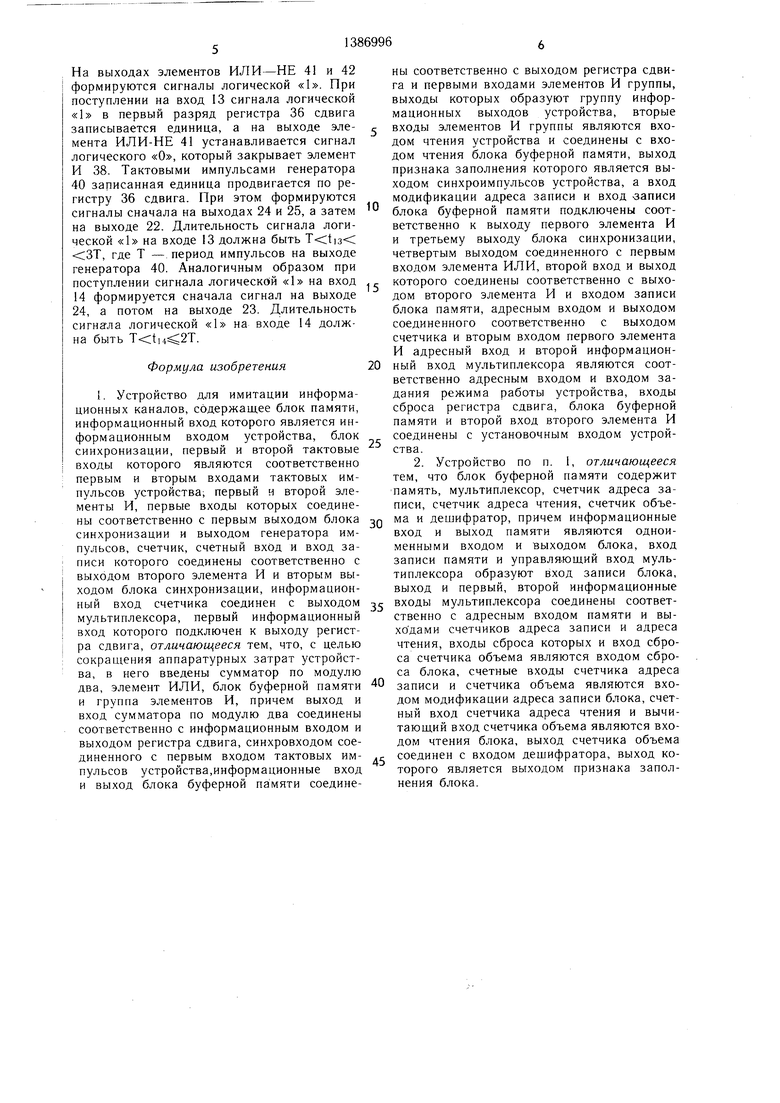

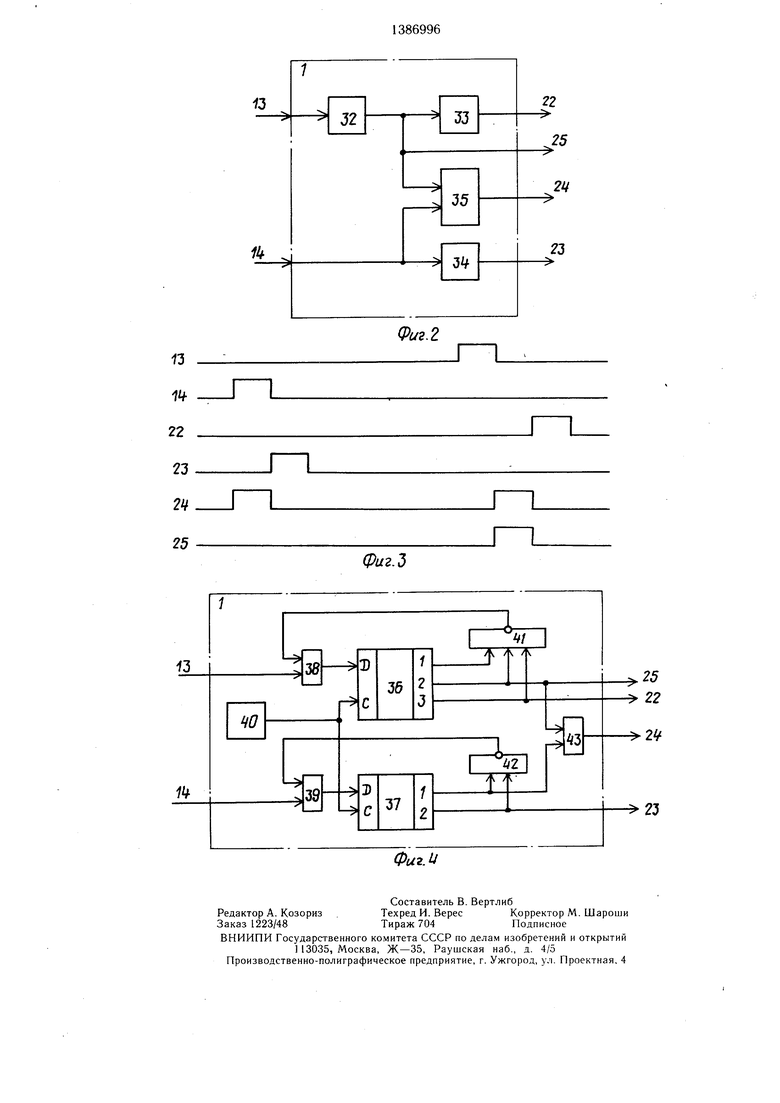

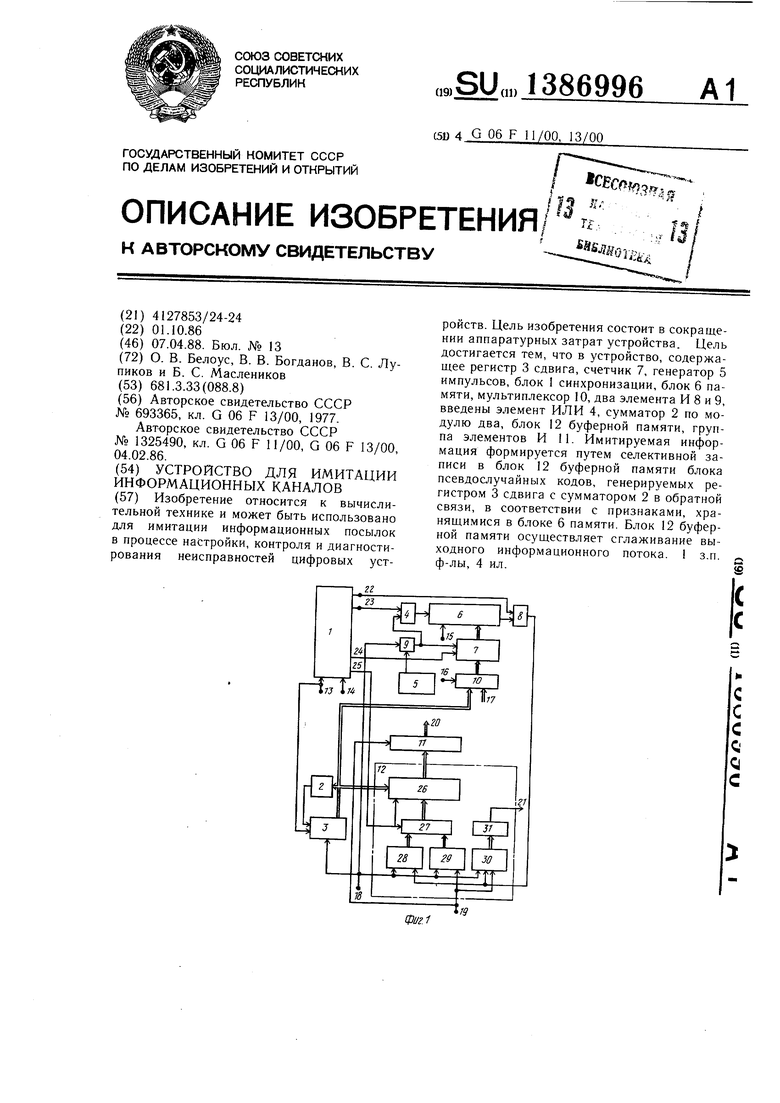

Цель изобретения - сокращение аппаратурных затрат устройства. На фиг. 1 представлена функциональ- ная схема устройства; на фиг. 2 - схема блока синхронизации; на фиг. 3 - временные диаграммы, поясняющие работу блока инхронизации; на фиг. 4 - схема блока синхронизации, вариант.

Устройство для имитации информационных каналов содержит блок 1 синхронизации, сумматор 2 по модулю два, регистр 3 сдвига, элемент ИЛИ 4, генератор 5 импульсов, лок 6 памяти, счетчик 7, первый 8 и второй элементы И, мультиплексор 10, группу элеентов И 11, блок 12 буферной памяти (БЗУ) первый 13 и второй 14 входы тактовых импульсов, информационный вход 15, вход 16 адания режима работы, адресный вход 17, вход 18 начальной установки, вход 19 чтения (данных), информационные вы)оды 20, выход 21 признака заполнения БЗУ 12, выходы 22-25 блока 1 синхронизации (фиг. 1).

Блок 12 буферной памяти содержит память 26, мультиплексор 27, счетчик 28 адреса записи, счетчик 29 адреса чтения, счетчик 30 объема и дещифратор 31 (фиг. 1).

Блок 1 синхронизации содержит формирователи 32-34 импульсов и элемент ИЛИ 35 (фиг. 2).

Блок 1 синхронизации (вариант) содержит регистры 36 и 37 сдвига, элементы И 38 и 39, генератор 40 импульсов, элементы ИЛИ-НЕ 41 и 42 и элемент ИЛИ 43 (фиг. 4).

Устройство работает следующим образом.

В устройстве в основу формирования информационных сигналов для настраиваемых и контролируемых объектов положено программируемое отсеивание из исходной последовательности псевдослучайных кодов (ПСК), получаемой с помощью генератора пек на базе регистра 3 и сумматором 2 в обратной связи, кодовых комбинаций, которые являются запрещенными для контролируемого объекта. С помощью этой программируемой селекции ПСК можно получить больщое количество выходных последовательностей кодов с различной структурой.

Перед началом работы сигналом логической «1, поступающим на вход 18, устройство приводится в исходное состояние. При этом обнуляются счетчики 28-30 в БЗУ 12, в регистр 3 заносится начальная кодовая комбинация, а также разрещается прохождение импульсов с выхода генератора 5 через элемент И 9. Импульсы с выхода

элемента И 9 поступают на счетный вход счетчика 7 и через элемент ИЛИ 4 на вход записи блока 6. В процессе начальной установки на информационном входе 15 постоян- но присутствует сигнал логической «1. В ячейку блока 6, адрес которой устанавливается на счетчике 7, записывается единица, а по заднему фронту импульса записи происходит модификация адреса в счетчике 7. Длительность сигнала начальной установки на входе 18 должна удовлетворять следующему условию:

,

где п - число ячеек в блоке 6;

f - частота импульсов, формируемых генератором 5.

В этом случае при начальной установке во все ячейки блока 6 записываются единицы.

5

После начальной установки осуществляется загрузка в блок 6 программы селекции, определяющей, какие кодовые комбинации при имитации информационных посылок должны быть отсеяны из исходной последовательности ПСК. При этом для каждого кода из п возможных кодов последовательности ПСК, генерируемой регистром 3 с сумматором 2, в блоке 6 отведен один бит по адресу, совпадающему с этим кодом. Наличие единиць в этом бите разрещает прол хождение соответствующего псевдослучайного кода на информационные выходы 20 устройства, а наличие нуля блокирует выдачу этого кода. После начальной установки во все ячейки блока 6 заносятся единицы, что разрещает прохождение всех

с кодов генератора ПСК на информационные выходы 20. Чтобы удалить из выходной последовательности кодов некоторые комбинации, в блоке 6 записываются нули по адресам, совпадающим с удаляемыми кодами. Для этого на вход 16 подается сиг0 нал логического «О, задающий режим загрузки программы селекции и обеспечиваю- щий подключение входов 17 через мультиплексор 10 к информационным входам счетчика 7, на информационный вход 15 пода5

ется сигнал логического «О, на адресный

вход 17 - запрещенный код, который должен быть удален из выходной последовательности устройства, а на вход 14 - импульс сопровождения.

Рассмотрим работу устройства при ус0 ловии, что блок 1 синхронизации реализован, как показано на фиг. 2. Тогда импульс сопровождения с входа 14 проходит через элемент ИЛИ 35 на вход записи счетчика 7 и заносит в него адрес с входа 17. По заднему фронту импульса сопровождения фор5 мирователь 34 формирует импульс, проходящий через элемент ИЛИ 4 на вход записи блока 6. В ячейку блока 6, адрес которой записан в счетчике 7, заносится нуль. Аналогичная операция выполняется для остальных запрещенных кодов.

После окончания загрузки программы селекции на вход 16 подается сигнал логической «1, задающий режим имитации информационных посылок.. Мультиплексор 10 подключает к информационным входам счетчика 7 выходы регистра 3 сдвига. На вход 13 подаются тактовые импульсы, поступающие на первый вход блока 1 и на син- хровход регистра 3, который начинает формировать последовательность ПСК. По переднему фронту каждого тактового импульса происходит сдвиг информации в регистре 3 и на его выходах появляется очередной псевдослучайный код, который поступает на информационные входы памяти 26 и через мультиплексор 10 на информационные входы счетчика 7. По заднему фронту тактового импульса формирователь 32 формирует импульс, который поступает на адресный вход мультиплексора 27 и вход записи памяти 26. Мультиплексор 27 подключает к адресным входам памяти 26 счетчик 28. По адресу, хранящемуся в счетчике 28, в память 26 записывается псевдослучайный код с выходов регистра 3. Импульс с выхода формирователя 32 проходит через элемент ИЛИ 35 на вход записи счетчика 7, в который через мультиплексор 10 записывается код с выходов регистра 3. Сигнал логического «О на выходе элемента ИЛИ 4 задает режим чтения данных из блока 6. На информационном выходе блока 6 появляется содержимое ячейки, адрес которой записан в счетчике 7. Выходной сигнал блока 6 подается на вход элемента И 8. В блоке 1 импульс с выхода формирователя 32 поступает также на вход формирователя 33, который по заднему фронту этого импульса формирует импульс, проходящий через элемент И 8 на вход модификации адреса записи БЗУ 12, если на выходе блока 6 установлен сигнал логической «1, т.е. если на выходах регистра 3 сформирован разрешенный псевдослучайный код. Если на выходе блока 6 установлен сигнал логического «О, т.е. на выходах регистра 3 присутствует запрещенный код, прохождение импульса от формирователя 33 через элемент И 8 блокируется. При разрешенном псевдослучайном коде импульс с выхода элемента И 8 увеличивает на единицу содержимое счетчиков 28 и 30.

Таким образом, по каждому тактовому импульсу на входе 13 регистр 3 с сумматором 2 формирует псевдослучайный код, который независимо от программы селекции запоминается в памяти 26. Однако адрес записи и объем хранящейся информации в БЗУ 12 модифицируется только при разрешенных комбинациях, т.е. в БЗУ 12 остаются лишь разрешенные псевдослучайные коды.

После накопления блока разрешенных кодов в БЗУ 12 на выходе дешифратора 31

формируется сигнал логической «I. Дешифратор 31 формирует сигнал логической «1, если содержимое счетчика 30 больше или равно т, и выдает его на выход 21, сообшая

объекту контроля, что из устройства может быть считан информационный блок. Обмен имитируемой информацией между устройством и объектом контроля осуществляется блоками по m слов. После получения

Q разрешения на чтение данных объект контроля выдает на вход 19 пачки из m синхросигналов. Для синхронизации устройства и объекта контроля необходимо, чтобы тактовые импульсы на входе 13 и синхроимпульсы на входе 19 формировались из

5 одной тактовой частоты (для этого может быть использован тактовый генератор объекта контроля). В этом случае операции записи и чтения данных из БЗУ 12 за счет блока 1 разносятся по времени. При чтении данных из устройства на входе записи БЗУ 12 присутствует сигнал логического «О. При этом память 26 находится в режиме чтения, а мультиплексор 27 подключает к адресным входам памяти 26 выходы счетчика 29. На выходах БЗУ 12 устанавли5 вается код, хранящийся в нем по адресу, формируемому счетчиком 29. С приходом на вход 19 синхроимпульса открываются элементы и 11 и на информационных выходах 20 устанавливается код, считанный из БЗУ 12. По заднему фронту синхроимпульса

0 увеличивается на единицу содержимое счетчика 29 и уменьшается на единицу содержимое счетчика 30. Ана.юг.ичиым образом из устройства считывается очередной код.

По окончании информационного блока

5 объект контроля проверяет состояние выхода 21. Если на выходе 21 устанавливается сигнал логической «1, то начинается чтение из устройства следующего блока данных. В противном случае объект контроля

Q переходит в режим ожидания. При имитации информации БЗУ 12 осушествляет сглаживание выходного информационного потока. В результате отсеивания запрещенных комбинаций из последовательности ПСК формируется неравномерный информа5 ционный поток, который в ряде случаев не может быть использован для ввода в контролируемые устройства, в то время как с информационных выходов 20 происходит выдача данных с равномерной частотой. Блок 1 синхронизации (фиг. 4) по сравне0 нию с блоком (фиг. 2) обладает большей стабильностью временных соотношений, поскольку в нем отсутствуют формирователи импульсов, однако он требует и больших аппаратурных затрат.

Блок 1 синхронизации (фиг. 4) работает следующим образом.

В исходном состоянии на входах 13 и 14 установлены сигналы логического «О, поэтому регистры 36 и 37 заполняются нулями.

На выходах элементов ИЛИ-НЕ 4 и 42 формируются сигналы логической «1. При поступлении на вход 13 сигнала логической «1 в первый разряд регистра 36 сдвига записывается единица, а на выходе эле- с мента ИЛИ-НЕ 41 устанавливается сигнал логического «О, который закрывает элемент И 38. Тактовыми импульсами генератора 40 записанная единица продвигается по регистру 36 сдвига. При этом формируются сигналы сначала на выходах 24 и 25, а затем на выходе 22. Длительность сигнала логической «1 на входе 13 должна быть ;ЗТ, где Т - период импульсов на выходе генератора 40. Аналогичным образом при поступлении сигнала логической «1 на вход , 14 формируется сначала сигнал на выходе 24, а потом на выходе 23. Длительность сигна-ла логической «1 на входе 14 должна быть .

Формула изобретения

25

1. Устройство для имитации информационных каналов, содержащее блок памяти, информационный вход которого является информационным входом устройства, блок синхронизации, первый и второй тактовые входы которого являются соответственно первым и вторым входами тактовых импульсов устройства, первый и второй элементы И, первые входы которых соединены соответственно с первым выходом блока синхронизации и выходом генератора импульсов, счетчик, счетный вход и вход за- писи которого соединены соответственно с выходом второго элемента И и вторым вы- ходом блока синхронизации, информацион- ный вход счетчика соединен с выходом мультиплексора, первый информационный вход которого подключен к выходу регист- ра сдвига, отличающееся тем, что, с целью сокращения аппаратурных затрат устройства, в него введены сумматор по модулю два, элемент ИЛИ, блок буферной памяти 40 и группа элементов И, причем выход и вход сумматора по модулю два соединены соответственно с информационным входом и выходом регистра сдвига, синхровходом соединенного с первым входом тактовых им- .г пульсов устройства,информационные вход и выход блока буферной памяти соединес

0

5

40 .г

ны соответственно с выходом регистра сдвига и первыми входами элементов И группы, выходы которых образуют группу информационных выходов устройства, вторые входы элементов И группы являются входом чтения устройства и соединены с входом чтения блока буферной памяти, выход признака заполнения которого является выходом синхроимпульсов устройства, а вход модификации адреса записи и вход -записи блока буферной памяти подключены соответственно к выходу первого элемента И и третьему выходу блока синхронизации, четвертым выходом соединенного с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго элемента И и входом записи блока памяти, адресным входом и выходом соединенного соответственно с выходом счетчика и вторым входом первого элемента И адресный вход и второй информационный вход мультиплексора являются соответственно адресным входом и входом задания режима работы устройства, входы сброса регистра сдвига, блока буферной памяти и второй вход второго элемента И соединены с установочным входом устройства.

2. Устройство по п. 1, отличающееся тем, что блок буферной памяти содержит память, мультиплексор, счетчик адреса записи, счетчик адреса чтения, счетчик объема и дешифратор, причем информационные вход и выход памяти являются одноименными входом и выходом блока, вход записи памяти и управля.ющий вход мультиплексора образуют вход записи блока, выход и первый, второй информационные входы мультиплексора соединены соответственно с адресным входом памяти и выходами счетчиков адреса записи и адреса чтения, входы сброса которых и вход сброса счетчика объема являются входом сброса блока, счетные входы счетчика адреса записи и счетчика объема являются входом модификации адреса записи блока, счетный вход счетчика адреса чтения и вычитающий вход счетчика объема являются входом чтения блока, выход счетчика объема соединен с входом дещифратора, выход которого является выходом признака заполнения блока.

Фи2.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Устройство для контроля цифровых устройств | 1988 |

|

SU1509901A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278981A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1571679A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249583A1 |

Изобретение относится к вычислительной технике и может быть использовано для имитации информационных посылок Б процессе настройки, контроля и диагностирования неисправностей цифровых устройств. Цель изобретения состоит в сокращении аппаратурных затрат устройства. Цель достигается тем, что в устройство, содержащее регистр 3 сдвига, счетчик 7, генератор 5 импульсов, блок I синхронизации, блок 6 памяти, мультиплексор 10, два элемента И 8 и 9, введены элемент ИЛИ 4, сумматор 2 по модулю два, блок 12 буферной памяти, группа элементов И 11. Имитируемая информация формируется путем селективной записи в блок 12 буферной памяти блока псевдослучайных кодов, генерируемых регистром 3 сдвига с сумматором 2 в обратной связи, в соответствии с признаками, хранящимися в блоке 6 памяти. Блок 12 буферной памяти осуществляет сглаживание выходного информационного потока. 1 з.п. ф-лы, 4 ил. 9 фиг.1

13 1if 22 23 2 25

Редактор А. Козориз Заказ 1223/48

Составитель В. Вертлиб

Техред И. ВересКорректор М. Шароши

Тираж 704Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(Д/г.З

.//

| Имитатор абонентов | 1977 |

|

SU693365A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-07—Публикация

1986-10-01—Подача