t

Х

СО Ч

10

Изобретение относится к запоминающим устройствам и может быть примене- но в цифровых вычислительных устройствах, где требуется обеспечение сох- ранности информации при кратковременном отключении и выходах за допуст1ф- мые значения питающих напряжений.

Цель изобретения - повышение надежности устройства.

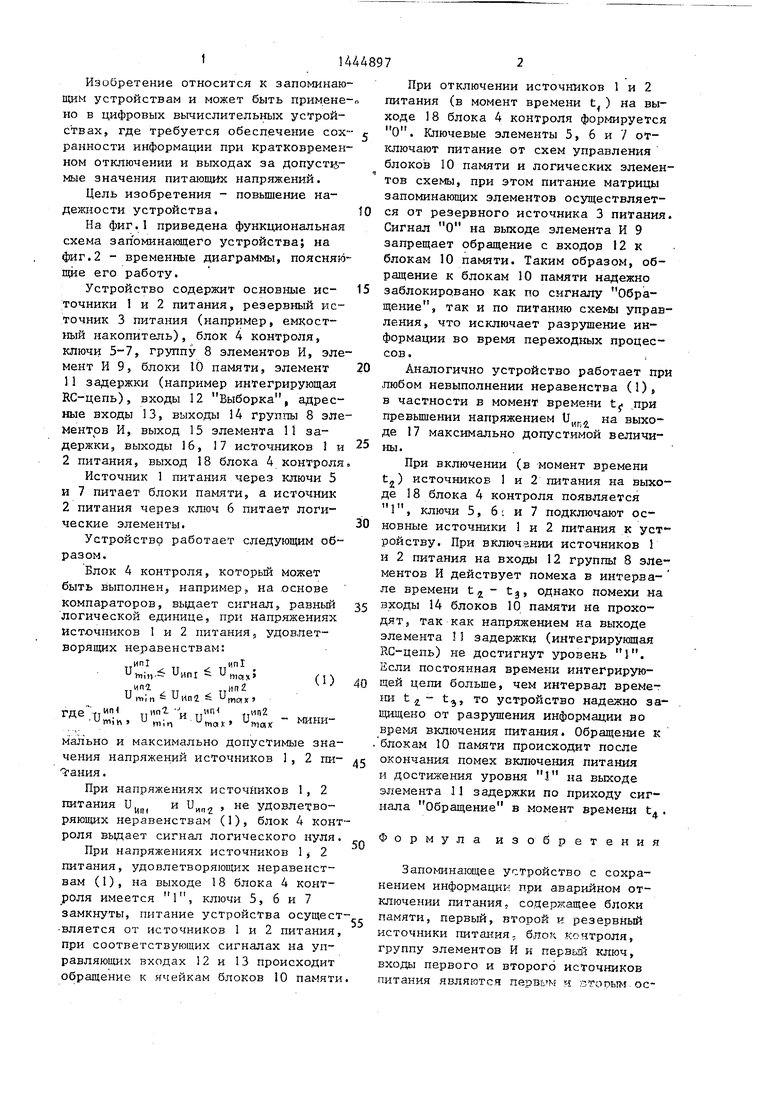

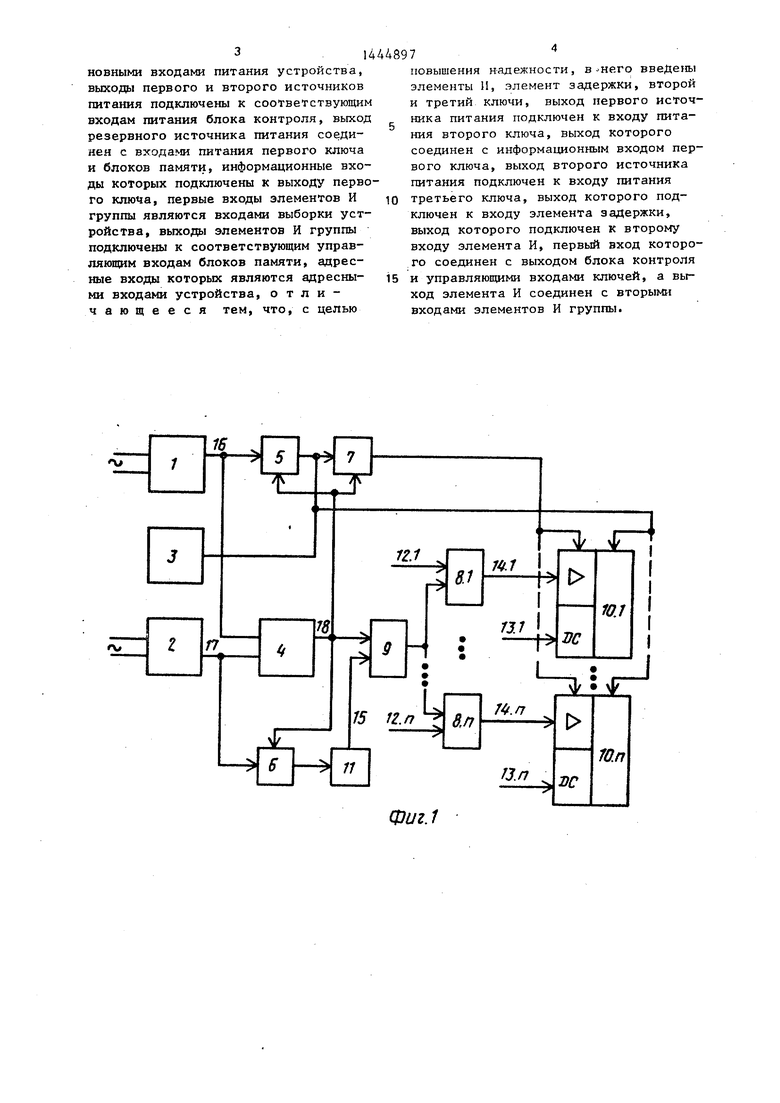

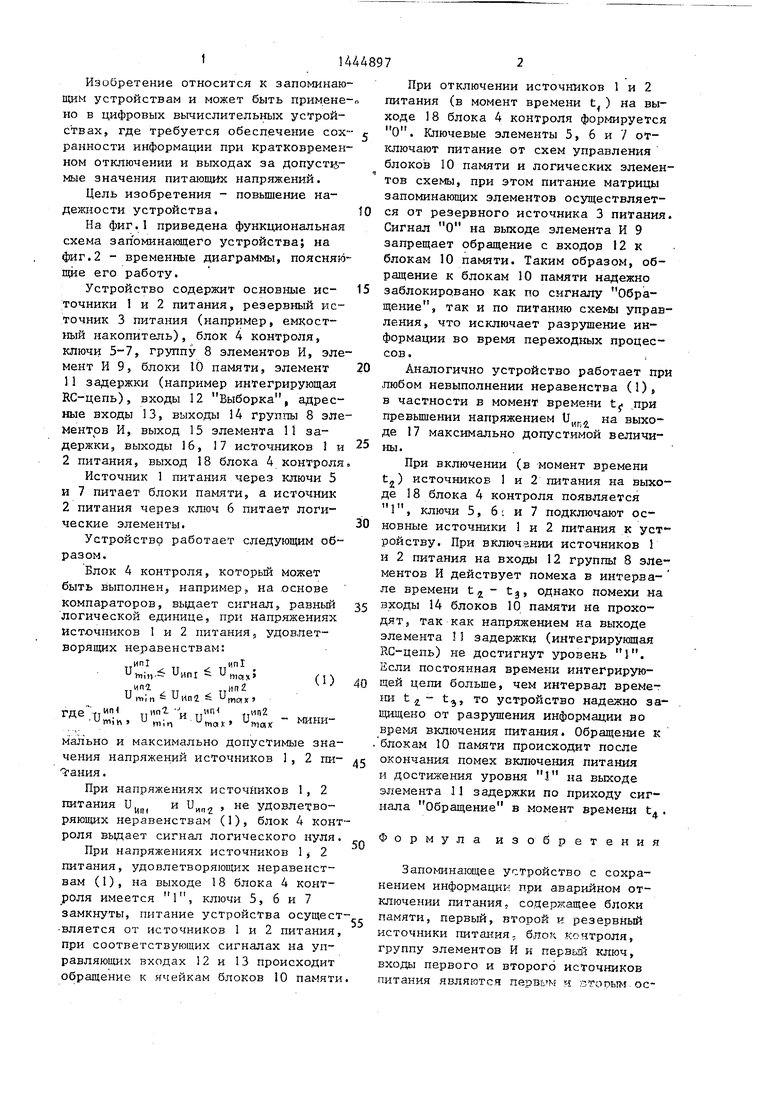

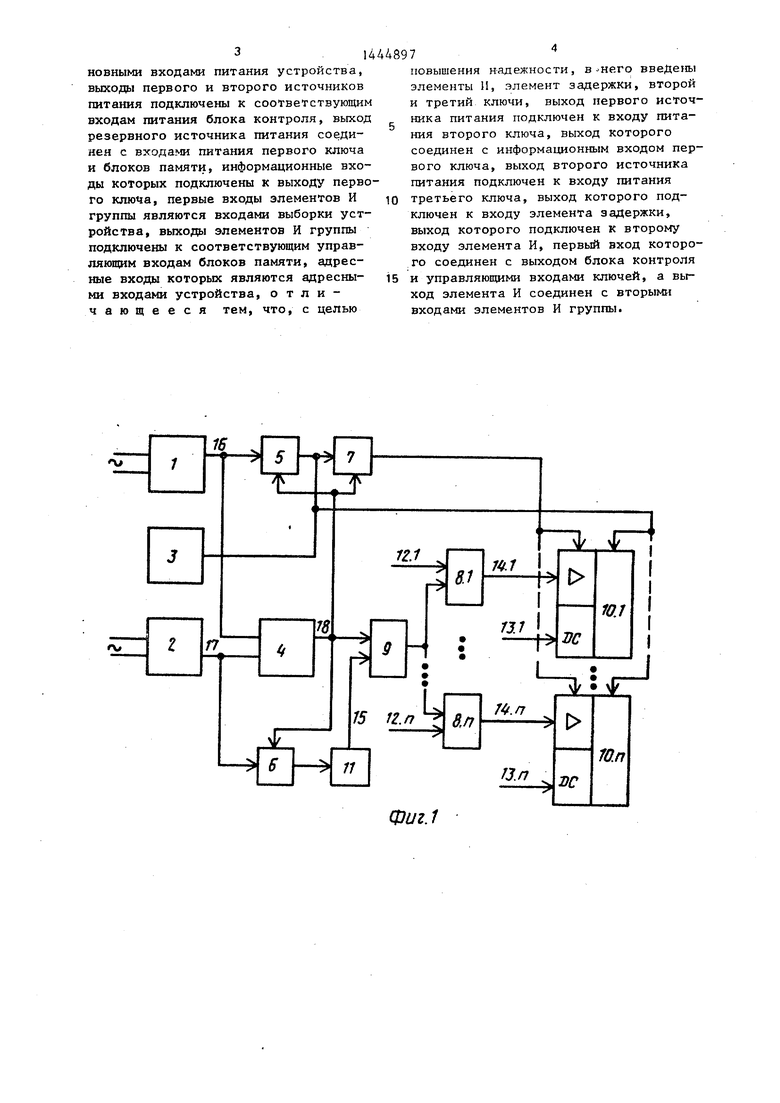

На фиг.1 приведена функциональная схема запоминающего устройства; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство содержит основные источники 1 и 2 питания, резервный источник 3 питания (например, емкостный накопитель), блок 4 контроля, ключи 5-7, группу 8 элементов И, эле мент И 9, блоки 10 памяти, элемент 20 11 задержки (например интегрирующая КС-цепь), входы 12 Выборка, адресные входы 13, выходы 14 группы 8 элементов И, выход 15 элемента 11 задержки, выходы 16, 17 источников и 25 2 питания, выход 18 блока 4 контроля

Источник 1 питания через ключи 5 и 7 питает блоки памяти, а источник 2 питания через ключ 6 питает логические элементы.

Устройство работает следующим образом.

Блок 4 контроля, которьш может быть выполнен, например, на .основе компараторов, выдает сигнал, равный логической единице, при напряжениях источников 1 и 2 питания, удовлет- ворящих неравенствам:

ип1

mq X

,11п2

4448972

При отключении источников 1 и 2 питания (в момент времени t) на выходе 18 блока 4 контроля формируется о. Ключевые элементы 5, 6 и 7 отключают питание от схем управления блоков 10 памяти и логических элементов схемы, при этом питание матрицы запоминающих элементов осуществляется от резервного источника 3 питания. Сигнал О на выходе элемента И 9 запрещает обращение с входор 12 к блокам 10 памяти. Таким образом, обращение к блокам 10 памяти надежно 15 заблокировано как по сигналу Обращение, так и по питанию схемы управления, что исключает разрушение информации во время переходных процессов,i

Аналогично устройство работает при любом невыполнении неравенства (1),

30

Ип1

,п. и,,п1

и

НПО.

(О 40

итГ„би„п2Й и

, ип1

где гтГ и и -Umitt и mln

mot к

1152

m o, и««в частности в момент времени t ,при превьшении напряжением tJ,,., на выходе 17 максимально допустимой величины.

При включении (в момент времени tg) источников 1 и 2 питания на выходе 18 блока 4 контроля появляется 1, ключи 5, 6; и 7 подключают основные источники 1 и 2 питания к устройству. При включении источников 1 н 2 питания на входы 12 группы В элементов И действует помеха в интерва- ле времени t tj, однако помехи на 35 входы 14 блоков 10 памяти на проходят, так как напряжением на выходе элемента 1 задержки (интегрирующая КС-цепь) не достигнут уровень 1. Если постоянная времени интегрирующей цепи больше, чем интервал време- 1ш t 2 - tj, то устройство надежно защищено от разрушения информации во время включения питания. Обращение к ,блокам 10 памяти происходит после окончания помех включения питания и достижения уровня 1 на выходе элемента Л задержки по приходу сигнала Обращение в момент времени t..

мально и максимально допустимые значения напряжений источников 1, 2 пи- .

При напряжениях источников 1, 2

питания и

hni

и и

ип 2

не удовлетворяющих неравенствам (1), блок 4 контроля выдает сигнал логического нуля

При напряжениях источников 1 2 питания, удовлетворяющих неравенствам (1), на выходе 18 блока 4 контроля имеется 1, ключи 5, б и 7 замкнуты, питание устройства осущест вляется от источников 1 и 2 питания, при соответствующих сигналах на управляющих входах 12 и 13 происходит обращение к ячейкам блоков 10 памяти

в частности в момент времени t ,при превьшении напряжением tJ,,., на выходе 17 максимально допустимой величины.

При включении (в момент времени tg) источников 1 и 2 питания на выходе 18 блока 4 контроля появляется 1, ключи 5, 6; и 7 подключают основные источники 1 и 2 питания к устройству. При включении источников 1 н 2 питания на входы 12 группы В элементов И действует помеха в интерва- ле времени t tj, однако помехи на входы 14 блоков 10 памяти на проходят, так как напряжением на выходе элемента 1 задержки (интегрирующая КС-цепь) не достигнут уровень 1. Если постоянная времени интегрирующей цепи больше, чем интервал време- 1ш t 2 - tj, то устройство надежно защищено от разрушения информации во время включения питания. Обращение к блокам 10 памяти происходит после окончания помех включения питания и достижения уровня 1 на выходе элемента Л задержки по приходу сигнала Обращение в момент времени t..

Формула изобретения

Запоминающее устройство с сохранением информации при аварийном отключении питания, содержащее блоки памяти, первый, второй и резервный источники пнтаи:иЯ; блок контроля, группу элементов И и первьй ключ, входы первого и второго источников питания являЕотся перВЕ М ч зторым основными входами питания устройства, выходы первого и второго источников питания подключены к соответствующим входам питания блока контроля, выход резервного источника питания соединен с входами питания первого ключа и блоков памяти, информационные входы которых подключены к выходу первого ключа, первые входы элементов И группы являются входами выборки устройства, выходы элементов И группы подключены к соответствующим управляющим входам блоков памяти, адресные входы которых являются адресными входами устройства, отличающееся тем, что, с целью

4897

повышения надежности, в-него введены элементы И, элемент задержки, второй и третий ключи, выход первого источника питания подключен к входу пита НИН второго ключа, выход которого соединен с информационным входом первого ключа, выход второго источника питания подключен к входу питания

10 третьего ключа, выход которого подключен к входу элемента задержки, выход которого подключен к второму входу элемента И, первый вход которого соединен с выходом блока контроля

15 и управляющими входами ключей, а выход элемента И соединен с вторыми входами элементов И группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля данных электронной вычислительной машины при прерываниях питания | 1983 |

|

SU1129615A1 |

| Электронный коммутатор сети переменного тока | 1987 |

|

SU1465989A1 |

| Усредняющее устройство | 1985 |

|

SU1285489A1 |

| Полупостоянное запоминающее устройство | 1985 |

|

SU1314387A1 |

| Устройство для счета ионов | 1984 |

|

SU1165968A2 |

| Устройство для автоматического ввода резервного питания | 1983 |

|

SU1136255A1 |

| Вторичный регулятор топливоподачи дизель-генератора переменного тока | 1985 |

|

SU1267356A2 |

| Устройство для сортировки кусков губчатого титана | 1987 |

|

SU1443981A1 |

| Устройство для контроля и управления технологическими процессами испытаний и тренировки фотоэлектронных умножителей | 1988 |

|

SU1517041A1 |

| Устройство для защиты информации в блоке памяти | 1982 |

|

SU1084904A1 |

Изобретение может быть использовано в цифровых вычислительных устройствах, где требуется обеспечение сохранности информации при кратковременных отключениях и выходах за допустимые значения питающих напряжений. Цель изобретения - повышение надежности устройства. В устройство,содержащее блоки памяти, основные и резервный источники питания, блок контроля, группу элементов И и ключ, введены элемент задержки, два ключа и элемент И с соответствующими связями, которые позволяют повысить надежность защиты информации от разрушения, т.к. нет необходимости для дублирования записанной информации дополнительным блоком памяти. 2 ил.

Фиг.1

фиг. 2

| Устройство для сохранения информации в памяти при отключении питания | 1977 |

|

SU736178A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с защитой информации от разрушения | 1983 |

|

SU1176386A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-12-15—Публикация

1987-03-11—Подача