Изобретение относится к автоматике и вычислительной технике и может быть применено в автоматизированных системах контроля и управления технологическими процессами, информационных измерительных системах высокой надежности, системах числового программного управления.

Цель изобретения - расширение области применения устройства за счет обработки группы однотипных аналоговых сигналов.

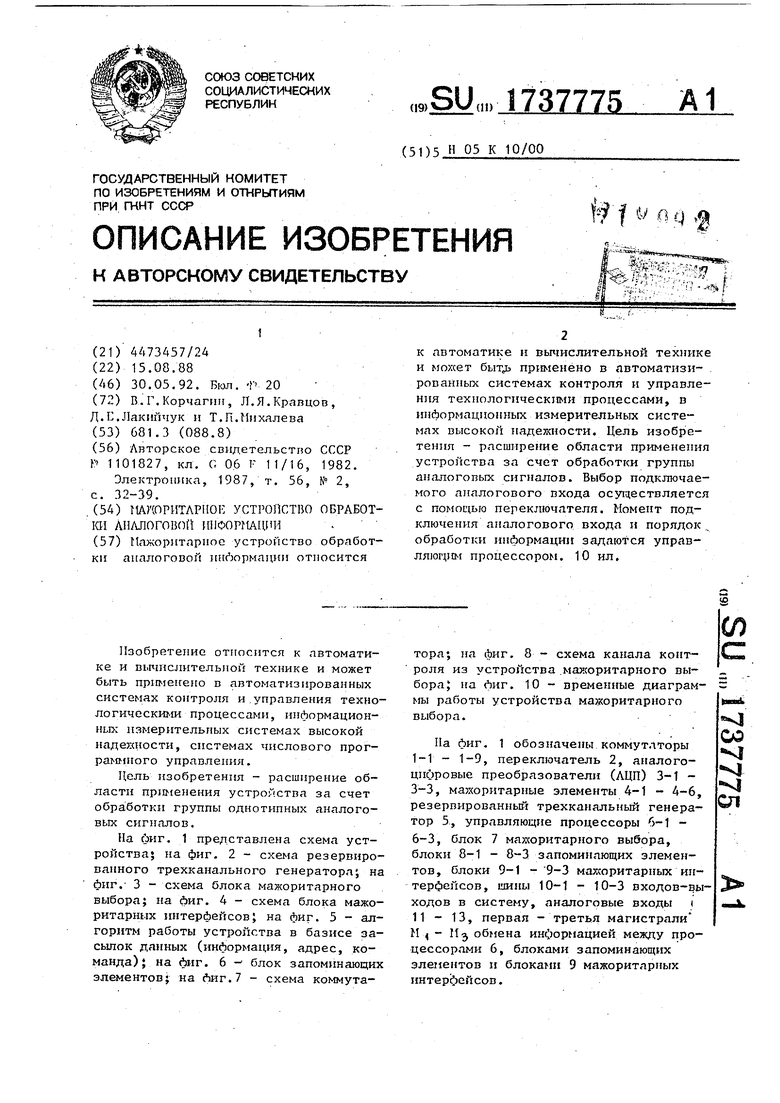

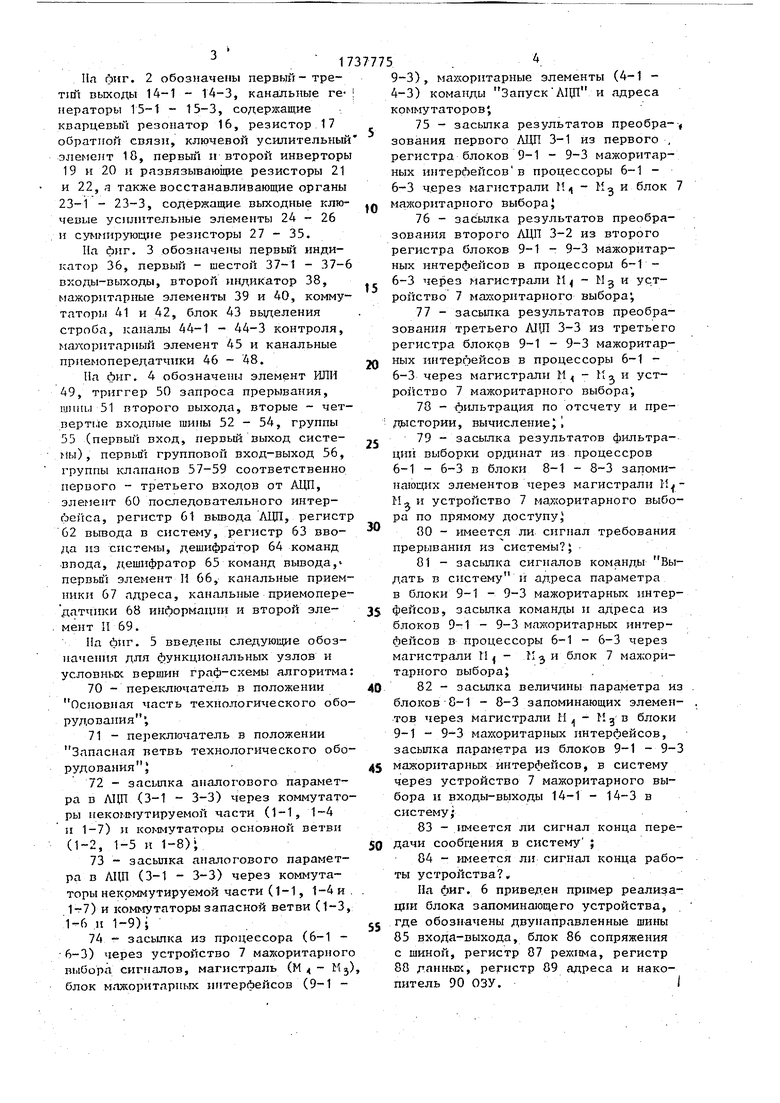

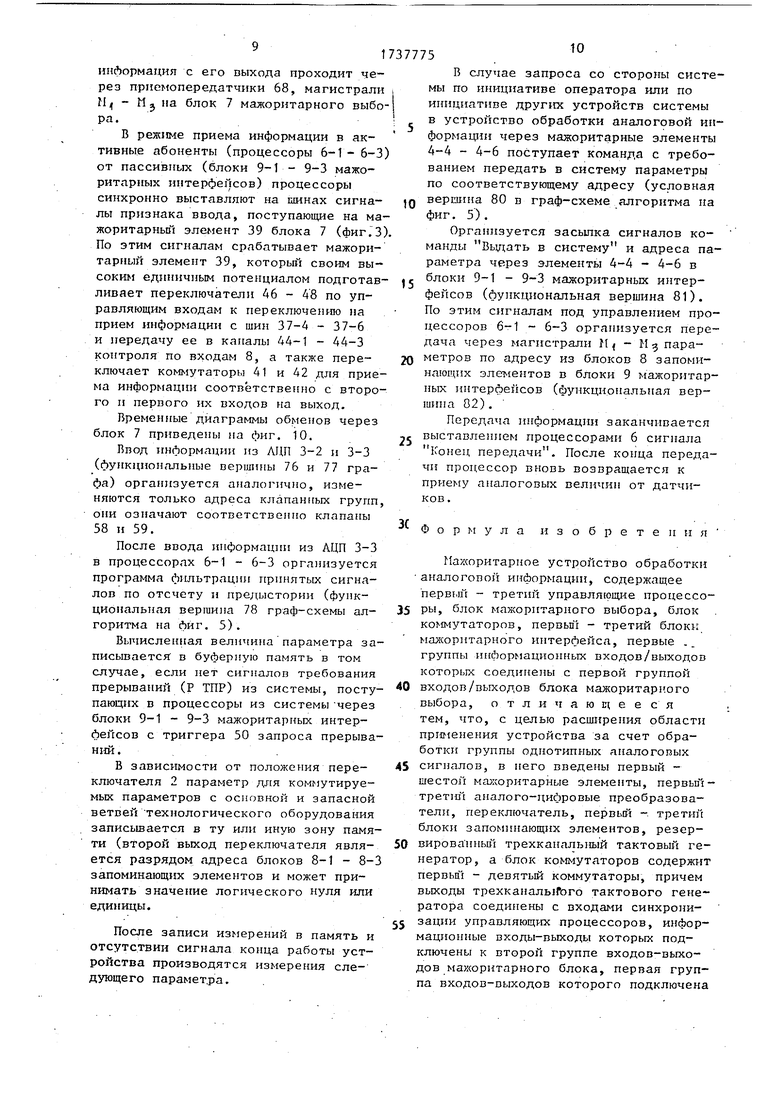

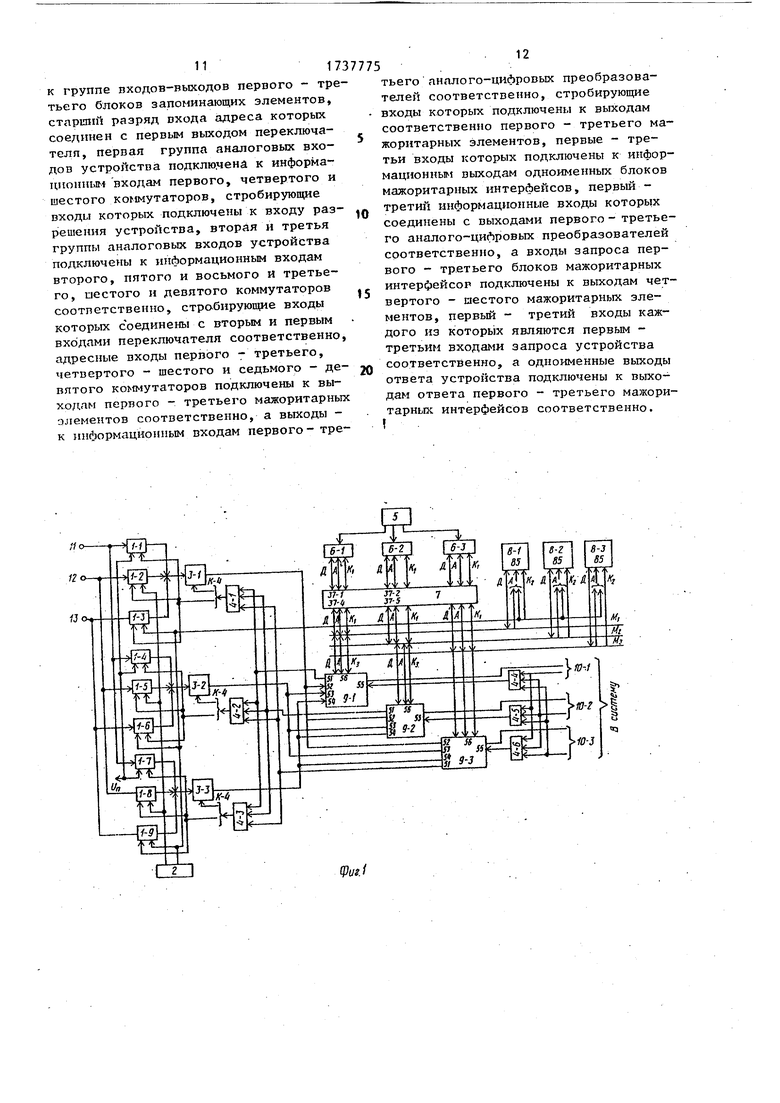

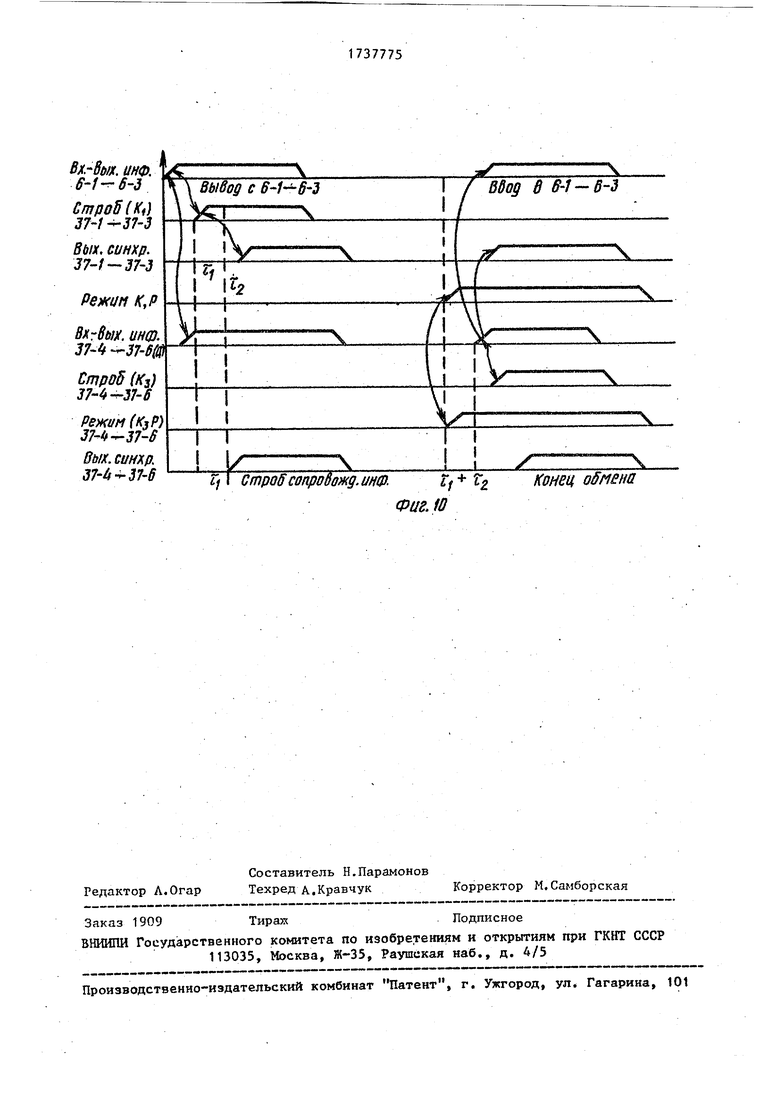

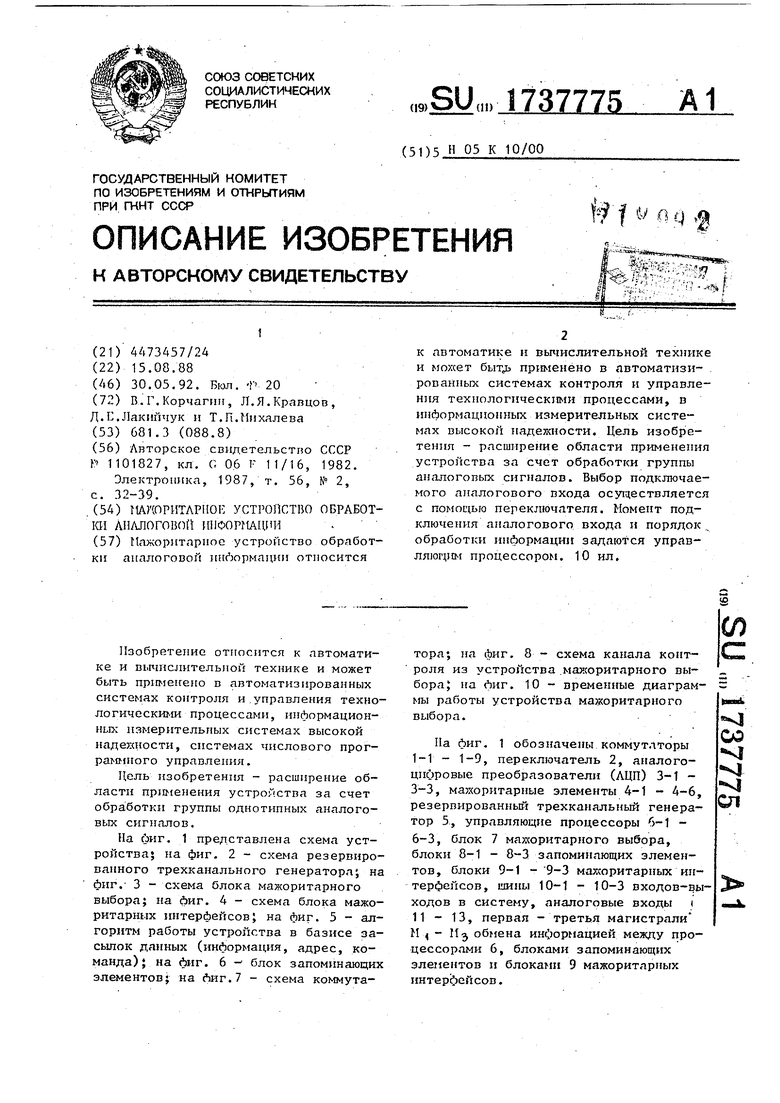

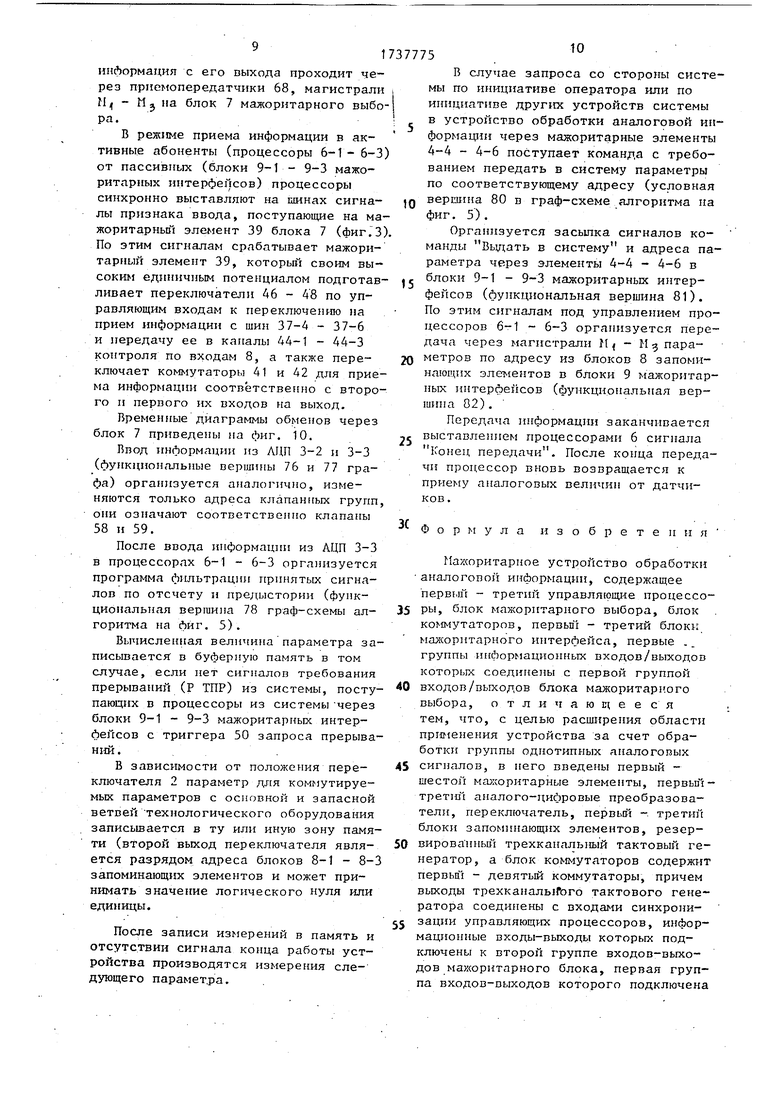

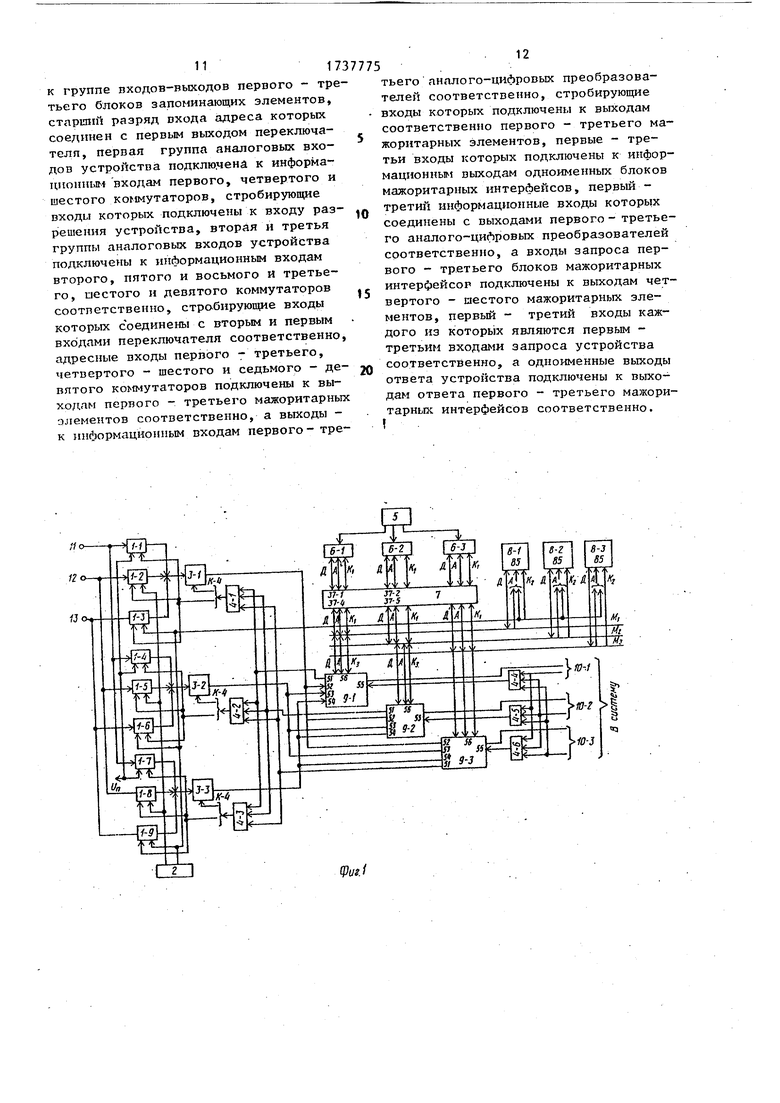

На фиг. 1 представлена схема устройства; на фиг. 2 - схема резервированного трехканального генератора; на фиг. 3 - схема блока мажоритарного выбора; на Фиг. 4 - схема блока мажоритарных интерфейсов; на фиг. 5 - алгоритм работы устройства в базисе засылок данных (информация, адрес, команда); на Фиг. 6 - блок запоминающих элементов; на Фиг.7 - схема коммутатора; на Фиг. 8 - схема канала контроля из устройства мажоритарного выбора; на Фиг. 10 - временные диаграммы работы устройства мажоритарного выбора.

На Фиг. 1 обозначены коммутаторы 1-1 - 1-9, переключатель 2, аналого- цифровые преобразователи (АЦП) 3-1 - 3-3, мажоритарные элементы 4-1 - 4-6, резервированный трехканальный генератор 5, управляющие процессоры 6-1 - 6-3, блок 7 мажоритарного выбора, блоки 8-1 - 8-3 запоминающих элементов, блоки 9-1 - 9-3 мажоритарных интерфейсов, шины 10-1 - 10-3 входов-выходов в систему, аналоговые входы ( 11 - 13, первая - третья магистрали М - М обмена информацией между процессорами 6, блоками запоминающих элементов и блоками 9 мажоритарных интерфейсов.

(Л

с

со

ч Ч

ч

ел

На фиг. 2 обозначены первый - третий выходы 14-1 - 14-3, канальные ге нераторы 15-1 - 15-3, содержащие кварцевый резонатор 16, резистор 17 обратной связи, ключевой усилительный элемент 18, первый и второй инверторы 19 и 20 и развязывающие резисторы 21 и 22, я также восстанавливающие органы 23-1 - 23-3, содержащие выходные ключевые усилительные элементы 24 - 26 и суммирующие резисторы 27 - 35.

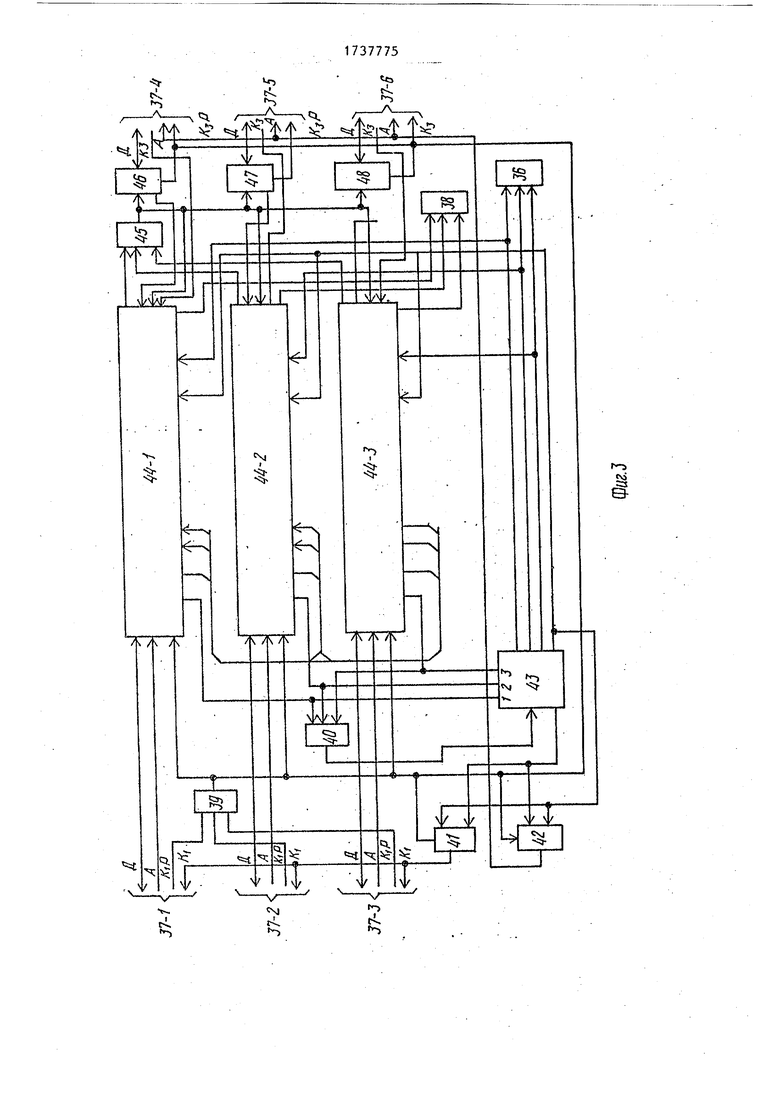

На биг. 3 обозначены первый индикатор 36, первый - шестой 37-1 - 37-6 входы-выходы, второй индикатор 38, мажоритарные элементы 39 и 40, коммутаторы 41 и 42, блок 43 выделения строба, каналы 44-1 - 44-3 контроля, мажоритарный элемент 45 и канальные приемопередатчики 46 - 48.

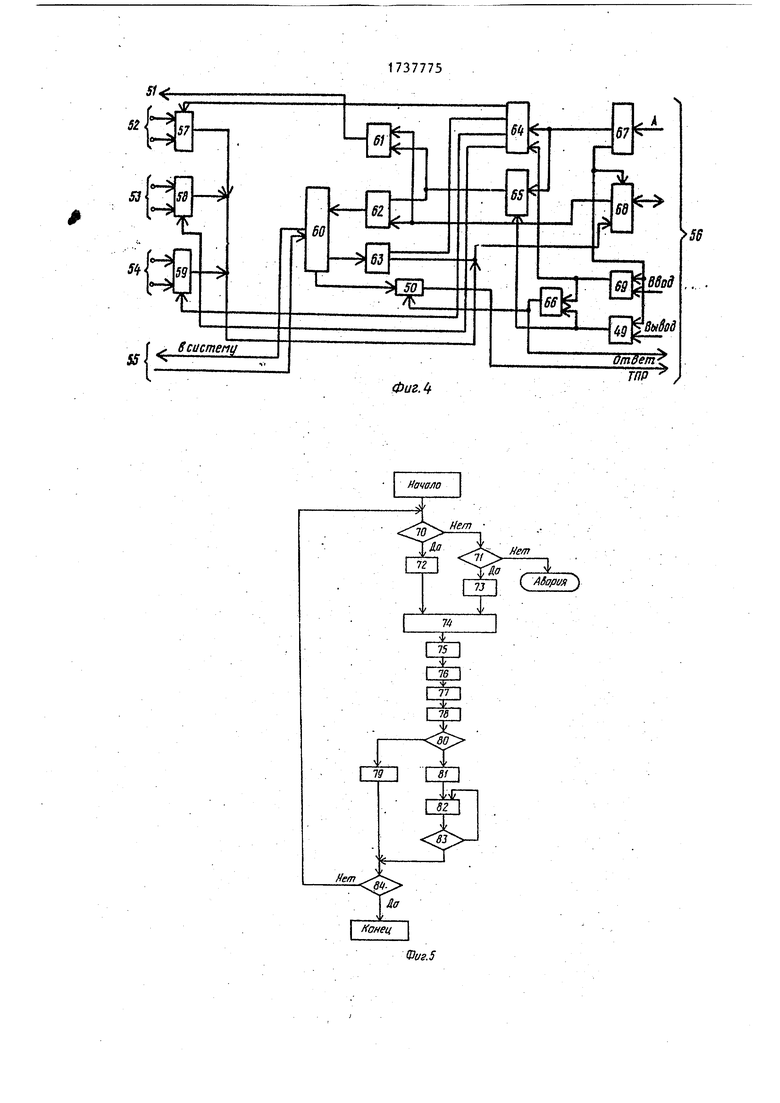

На Лиг. 4 обозначены элемент ИЛИ 49, триггер 50 запроса прерывания, шипы 51 второго выхода, вторые - четвертые входные шины 52 - 54, группы 55 (первый вход, первый выход системы), первый групповой вход-выход 56, группы клапанов 57-59 соответственно первого - третьего входов от АЦП, элемент 60 последовательного интер- йейса, регистр 61 вывода Л1Щ, регистр 62 вывода в систему, регистр 63 ввода из системы, дешифратор 64 команд ввода, дешифратор 65 команд вывода, первый элемент И 66, канальные приемники 67 адреса, канальные приемопередатчики 68 информации и второй элемент И 69.

На фиг. 5 введены следующие обозначения для функциональных узлов и условных вершин граф-схемы алгоритма:

70- переключатель в положении Основная часть технологического оборудования ;

71- переключатель в положении Запасная ветвь технологического оборудования }

72- засыпка аналогового параметра в Л1Щ (3-1 - 3-3) через коммутаторы некоммутируемой части (1-1, 1-4

и 1-7) и коммутаторы основной ветви (1-2, 1-5 и 1-8);

73- засыпка аналогового параметра в АЦП (3-1 - 3-3) через коммутаторы некрммутируемой части (1-1, 1-4 и 1-7) и коммутаторы запасной ветви (1-3, 1-6 и 1-9)i

74- засылка из процессора (6-1 - 6-3) через устройство 7 мажоритарного выбора сигналов, магистраль (М - Мэ) блок мажоритарных интерфейсов (9-1

5

9-3), мажоритарные элементы (4-1 - 4-3) команды Запуск А1Щ и адреса коммутаторов ,

75- засыпка результатов преобра- зования первого АЦП 3-1 из первого , регистра блоков 9-1 - 9-3 мажоритарных интерфейсов в процессоры 6-1 - 6-3 через магистрали Мц - М и блок 7 мажоритарного выбораJ

76- засылка результатов преобразования второго АЦП 3-2 из второго регистра блоков 9-1 - 9-3 мажоритарных интерфейсов в процессоры 6-1 с 6-3 через магистрали И - Н3 и устройство 7 мажоритарного выбора;

77- засылка результатов преобразования третьего АЦП 3-3 из третьего регистра блоков 9-1 - 9-3 мажоритарных интерфейсов в процессоры 6-1 - 6-3 через магистрали И 4 - И о и устройство 7 мажоритарного выбора;

73 - фильтрация по отсчету и предыстории, вычисление;

79 - засылка результатов фильтрации выборки ординат из процессров 6-1 - 6-3 в блоки 8-1 - 8-3 запоминающих элементов через магистрали М и устройство 7 мажоритарного выбора по прямому доступу

00 - имеется ли сигнал требования прерывания из системы ;

81- засылка сигналов команды Выдать в систему и адреса параметра

в бпоки 9-1 - 9-3 мажоритарных интерфейсов, засылка команды и адреса из блоков 9-1 - 9-3 мажоритарных интерфейсов в процессоры 6-1 - 6-3 через магистрали 1Ц - блок 7 мажоритарного выбора}

82- засылка величины параметра из блоков 8-1 - 8-3 запоминающих элементов через магистрали II - И в блоки 9-1 - 9-3 мажоритарных интерфейсов, засылка параметра из блоков 9-1 - 9-3

5 мажоритарных интерфейсов, в систему через устройство 7 мажоритарного выбора и входы-выходы 14-1 - 14-3 в систему;

83- имеется ли сигнал конца передачи сообщения в систему ;

84- имеется ли сигнал конца работы устройства.

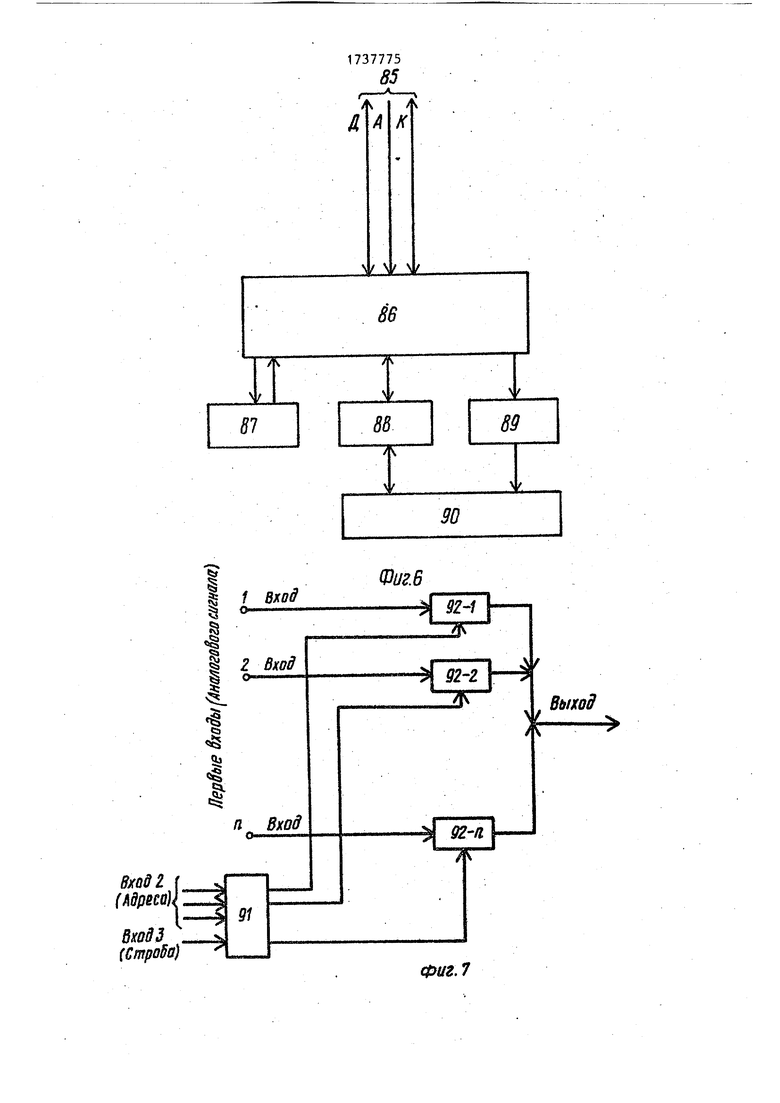

На фиг. 6 приведен пример реализации блока запоминающего устройства, где обозначены двунаправленные шины 85 входа-выхода, блок 86 сопряжения с шиной, регистр 87 режима, регистр 88 данных, регистр 89 адреса и накопитель 90 ОЗУ.I

0

S

0

0

5

Коммутатор (фиг. 7) содержит дешифратор 91 адреса коммутатора и набор аналоговых ключей 92-1 - 92-п.

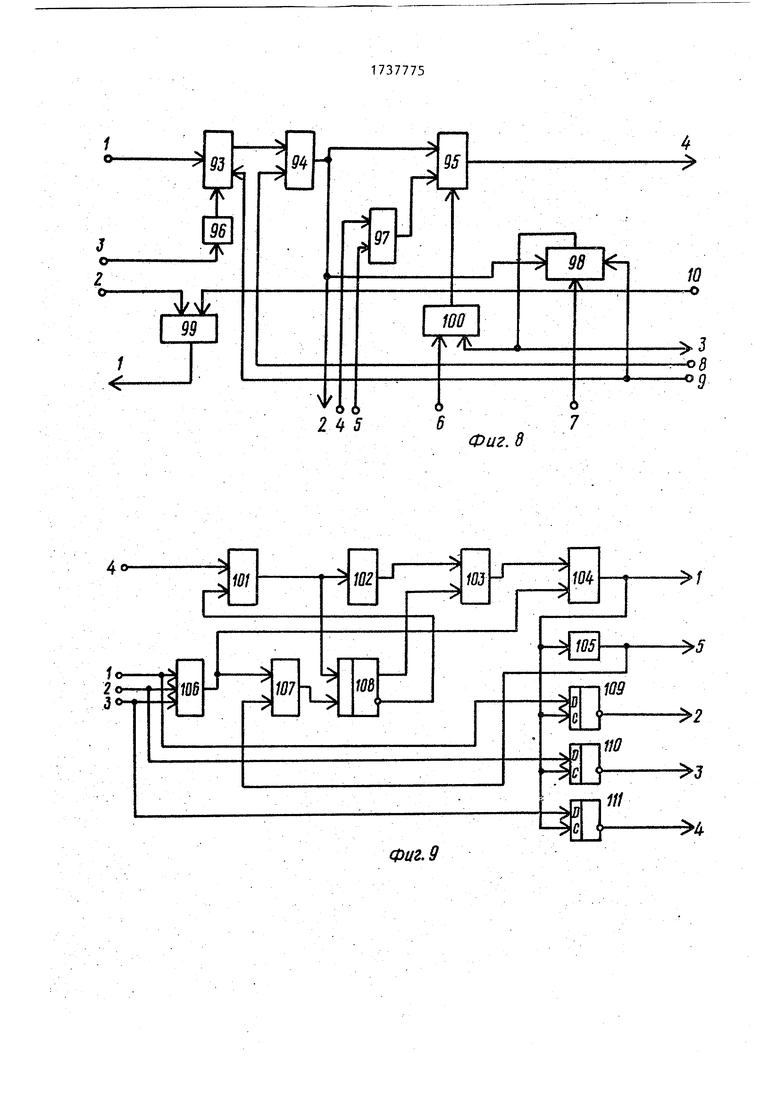

На фиг. 8 обозначены коммутаторы 93 - 95, инвертор 96, элемент ИЛИ 97, коммутатор 98 и элементы ИЛИ 99 и

100,на фиг. 9 - первый элемент И.

101,первый элемент 102 задержки, второй элемент И 103, элемент ИЛИ 104, второй элемент 105 задержки, третий элемент И 106, элемент ИЛИ 107

и триггеры 108-111.

Перед началом работы аналоговые сигналы с датчиков выставлены и поступают на входные шины 11 - 13. Переключатель 2 установлен в положение, которое указывает, с какой ветвью технологического оборудования работает вся система. В случае работы с основной ветвью на первом выходе переключателя 2 имеется потенциал логической единицы.

Производится режим начальной установки по инициативе от системы. По сигналу начальной установки обнуляются 8-1 - 8-3 блоки запоминающих элементов и оперативная память процессоров 6-1 - 6-3, а также элементы памяти в блоках 9-1 - 9-3 мажоритарных интерфейсов.

После начальной установки устройство готово к работе по программе.

Устройство работает следующим образом.

Программа работы всего устройства синхронно разворачивается процессорами 6-1 - 6-3. Помимо одновременности запуска, синхронность работы процессоров обеспечивается работой резервированного трехканального генерато- ра 5.

Синхронизация работы генераторов обеспечивается синхронизующими связями через развязывающие резисторы 21-1 - 21-3 и 22-1 - 22-3. Синхрони- зированные сигналы генераторов через ключевые усилительные элементы 18-1 - 18-3 подаются на восстанавливающие органы 23-1 - 23-3 с тремя выходами, являющимися выходами резервированных трехканальных генераторов 14-1 - 14-3.

Процессоры 6-1 - 6-3 синхронно пересылают для коммутаторов 1-1-1-9 адрес аналогового параметра и команду Запуск АЦП. Адрес и команда передаются через устройство 7 мажоритарного выбора сигналов, магистрали

5

0

5

Q

5 0

5 0

,

0

М - И в блоки 9-1 - 9-3 мажоритарных интерфейсов.

Блок 7 мажоритарного выбора (фиг. 3) включает в свой состав первую - третью группы входных-выходных шин 37-1 - 37-3 для связи с активным абонентом (процессорами), четвертую - шестую группы входных-выходных шин 37-4 - 37-6 для связи с пассивным абонентом (блоками интерфейса). ч

Инициатором обмена являются активные абоненты. На них выставляется информация по шинам 37-1 - 37-3, в случае режима ввода в пассивные абоненты на пинах строба сопровождения информации, подключенных к входу каналов контроля,выставляется г единичный потенциал, который, пройдя ряд элементов канала, оказывается на его выходе. Сигналы стробов с трех каналов контроля через элемент 40 поступают в блок 43 выделения строба.

На шинах режима, соединенных с входами мажоритарного элемента 39, выставлен нулевой потенциал. На выходе элемента 39 также присутствует нулевой потенциал, который подготавливает коммутаторы 41 и 42 и ряд ментов каналов 44-1 - 44-3 контроля для переключения на выход информации с первых входов, канальные приемопередатчики 47-49 подготовлены для пропуска информации со стороны входов в сторону входа-выхода (шины 37-4 - 37-6).

Сигнал информации при исправности процессов 6-1 - 6-3 проходит через коммутаторы 93 всех каналов контроля на коммутаторы 94 по первому входу. С выхода коммутатора 94 информация поступает на третьи входы компаратора 98 и на первый вход коммутатора 95 соответствующего канала контроля, на первые и вторые входы соответствующих элементов ИЛИ 97 других каналов контроля, а также через входы 4 собственного канала контроля приходят сигналы информации из других каналов контроля.

Сигналы стробов сопровождения информации, пройдя на вход мажоритарного элемента 40, с его выхода поступают через блок 43 выделения строба на элемент И 101. Так как триггер 108 в исходном состоянии имеет высокий потенциал на инверсном выходе, то сигнал с выхода элементов И 101 после задержки на элементе 102 задержки

выставляет высокий потенциал на выходе элемента 102. Триггер 108 остается в состоянии О в любом случае, т.е. если сигнал с элемента И 101 перекинет его в состояние 1, то после элемента ИЛИ 104, элемента 105 задержки и элемента ИЛИ 107 вновь установится состояние О в триггере 108. Через элемент 105 задержки формируется выходной синхронизирующий сигнал в блоке 43, проходящий через коммутатор 42, сигнал управления на котором от элемента 39 позволяет пропустить на выход входную информацию по первому входу.

Сигналы информации при исправности всех активных абонентов, приходящие на первые входы каналов 44 контроля, проходят через них, контролируя на наличие соответствующего строба из блока 43 выделения строба, и выходят по четвертому выходу каналов 44 контроля. После выхода из каналов контроля сигналы поступают на мажоритарный элемент 45 совместно с сигналами из других каналов. С выхода мажоритарного элемента 45 сигналы подаются на вход канальных приемопередатчиков 46 - 48 для передачи пассивным абонентам. В случае отсутствия какого- либо сигнала информации или рассогласования во времени больше допустимого срабатывает индикатор 38, в случае попадания сигнала строба сопровождения или сигнала режима срабатывает индикатор 36.

Через блоки мажоритарных интерфейсов передается адрес коммутатора и команда Запуск АЦП. В блоке 9 мажоритарного интерфейса (фиг. 4) адрес попадает в канальные приемники 67 адреса, откуда, расшифровавгаись, кла- панирует элементы 68, 69 и 49, информация (адрес коммутатора, команда Запуск А1Щ) - в канальные приемопередатчики 68 информации, признак режима (команда Вывод по отношению к процессору) - в элемент И 49.

Адрес коммутатора и команда Запуск АЦП по шине 51 из блоков 9-1 - 9-3 мажоритарных интерфейсов поступают на мажоритарные схемы 4-1 - 4-3.

С выхода мажоритарных элементов 4-1 - 4-3 адрес коммутатора поступает на коммутаторы 1-1 - 1-9, а команда - на ЛИП 3-1 - 3-3. Коммутаторы построены так, что принимают определенную группу разрядов адреса. Коммутаторы 1-2, 1-5 и 1-8 откликаются

5

5

на свои адреса только тогда, когда переключатель 2 установлен в такое положение, при котором на его первом выходе установлен высокий потенциал, а коммутаторы 1-3, 1-6 и 1-9 - при высоком потенциале на втором выходе переключателя, т.е. в коммутаторах (йиг. 7) стробируется дешифратор 91. Таким образом осуществляется анализ работы с основной или запасной ветвями технологического оборудования (условные вершины 70 и 71 алгоритма на фиг. 5).

После получения адреса коммутатором, к которому подключен аналоговый датчик, опрашиваемый в данный момент, аналоговый сигнал с этого датчика получает возможность прохождения на АЦП 3-1 - 3-3 через соответствующие коммутаторы.

После преобразования на АЦП 3-1 - 3-3 сигнал в цифровой форме записывается одновременно в три блока 9-1 - 9-3 мажоритарных интерЛенсов последовательно следующим образом.

Из АЦП 3-1 информация заносится через клапаны 57 всех блоков 9-1 - .9-3 интербейсов и через приемопередатчики 68 в процессоры 6-1 - 6-3, из АЦП 3-2 информация заносится через клапаны 58 всех блоков 9-1 - 9-3 и через их приемопередатчики 68 в процессоры 6-1 - 6-3, из АЦП 3-3 информация заносится через клапаны 59 всех блоков 9-1 - 9-3 и через их приемопередатчики 68 в процессоры 6-1 - 6-3.

АЦП 3-1 - 3-3 имеют в своем составе выходной регистр результата, поэтому результат преобразования вы- 0 ставляется через время 1п. после команды Запуск АЦП и стирает старое значение результата преобразования.

Программа обработки информации в процессорах 6-1 - 6-3 построена та- 5 ким образом, что она учитывает время преобразования инбормации на преобразователях 3, давая возможность достоверного интегрального измерения параметра, чтобы случайное кратковременное отклонение величины параметра (всплеск) не было заАиксировано.

Передача информации из АЦП происходит следующим образом.

Процессоры 6-1 - 6-3 подают коман- 5 ду на ввод результата преобразования АЦП 3-1, которая поступает параллельно с адресом группы клапанов 57. Адрес группы клапанов 57 с выхода дешифратора 64 открывает клапаны 57 и .,

0

5

0

инАормация с его выхода проходит через приемопередатчики 68, магистрали Н 4 - Mj на блок 7 мажоритарного выбора.

В режиме приема информации в активные абоненты (процессоры 6-1-6-3) от пассивных (блоки 9-1 - 9-3 мажоритарных интерфейсов) процессоры синхронно выставляют на шинах сигналы признака ввода, поступающие на мажоритарный элемент 39 блока 7 (фиг.З). По этим сигналам срабатывает мажоритарный элемент 39, который своим высоким единичным потенциалом подготавливает переключатели 46 - 48 по управляющим входам к переключению на прием информации с шин 37-4 - 37-6 и передачу ее в каналы 44-1 - 44-3 контроля по входам 8, а также переключает коммутаторы 41 и 42 для приема информации соответственно с второго и первого их входов на выход.

Временные диаграммы обменов через блок 7 приведены на фиг. 10.

Ввод информации из ЛЦП 3-2 и 3-3 (функциональные вершины 76 и 77 графа) организуется аналогично, изменяются только адреса клапанных групп, они означают соответственно клапаны 58 и 59.

После ввода информации из ЛЦП 3-3 в процессорах 6-1 - 6-3 организуется программа фильтрации принятых сигналов по отсчету и предыстории (функциональная вершина 78 граф-схемы алгоритма на Лиг. 5).

Вычисленная величина параметра записывается в буферную память в том случае, если нет сигналов требования прерываний (Р ТПР) из системы, поступающих в процессоры из системы через блоки 9-1 - 9-3 мажоритарных интер- Лейсов с триггера 50 запроса прерываний.

В зависимости от положения переключателя 2 параметр для коммутируемых параметров с основной и запасной ветвей технологического оборудования записывается в ту или иную зону памяти (второй выход переключателя является разрядом адреса блоков 8-1 - 8-3 запоминающих элементов и может принимать значение логического нуля или единицы.

После записи измерений в память и отсутствии сигнала конца работы устройства производятся измерения следующего параметра.

0

В случае запроса со стороны системы по инициативе оператора или по инициативе других устройств системы в устройство обработки аналоговой информации через мажоритарные элементы 4-4 - 4-6 поступает команда с требованием передать в систему параметры по соответствующему адресу (условная вершина 80 в граф-схеме алгоритма на фиг. 5).

Организуется засылка сигналов команды Выдать в систему и адреса параметра через элементы 4-4 - 4-6 в , блоки 9-1 - 9-3 мажоритарных интерфейсов (функциональная вершина 81). По этим сигналам под управлением процессоров 6-1 - 6-3 организуется передача через магистрали }{i - М параметров по адресу из блоков 8 запоминающих элементов в блоки 9 мажоритарных интербейсов (функциональная вершина 02).

Передача информации заканчивается выставлением процессорами 6 сигнала Конец передачи. После конца передачи процессор вновь возвращается к приему аналоговых величин от датчиков.

0

5

С

5

0

5

0

5

Формула изобретения

Мажоритарное устройство обработки аналоговой информации, содержащее первый - третий управляющие процессоры, блок мажоритарного выбора, блок коммутаторов, первый - третий блоки мажоритарного интерфейса, первые .. группы инйормационных входов/выходов которых соединены с первой группой входов/выходов блока мажоритарного выбора, отличающееся тем, что, с целью расширения области применения устройства за счет обработки группы однотипных аналоговых сигналов, в него введены первый - LiecToi i мажоритарные элементы, первьш - третий аналого-цифровые преобразователи, переключатель, первый - третий блоки запоминающих элементов, резервированный трехканальный тактовый генератор, а блок коммутаторов содержит первый - девятый коммутаторы, причем выходы трехканалыГЬго тактового генератора соединены с входами синхронизации управляющих процессоров, информационные входы-выходы которых подключены к второй группе входов-выходов мажоритарного блока, первая группа входов-выходов которого подключена

к группе входов-выходов первого - третьего блоков запоминающих элементов, старший разряд входа адреса которых соединен с первым выходом переключателя, первая группа аналоговых входов устройства подключена к информационным входам первого, четвертого и шестого коммутаторов, стробирующие входи которых подключены к входу разрешения устройства, вторая и третья группы аналоговых входов устройства подключены к информационным входам второго, пятого и восьмого и третьего , иестого н девятого коммутаторов соответственно, страбнрующие входы которых соединены с вторым и первым входами переключателя соответственно, адресные входы первого - третьего, четвертого - шестого и седьмого - девятого коммутаторов подключены к выходам первого - третьего мажоритарных элементов соответственно, а выходы - к информационным входам первого - третьего аналого-цифровых преобразователей соответственно, стробирующие входы которых подключены к выходам соответственно первого - третьего мажоритарных элементов, первые - третьи входы которых подключены к информационным выходам одноименных блоков мажоритарных интерфейсов, первый - Ф третий информационные входы которых соединены с выходами первого - третьего аналого-циЛровых преобразователей соответственно, а входы запроса первого - третьего блоков мажоритарных интерфейсор подключены к выходам четвертого - шестого мажоритарных элементов, первый - третий входы каждого нэ которых являются первым - третьим входами запроса устройства соответственно, а одноименные выходы ответа устройства подключены к выходам ответа первого - третьего мажоритарных интерфейсов соответственно.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| МЕТЕОРОЛОГИЧЕСКАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 1991 |

|

RU2084922C1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

| АВТОМАТИЗИРОВАННАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ ЗАПРАВКОЙ КРИОГЕННОГО РАЗГОННОГО БЛОКА | 1995 |

|

RU2084011C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1992 |

|

RU2054198C1 |

| АВТОМАТИЧЕСКАЯ НРЛС С УВЕЛИЧЕННЫМ НЕОБСЛУЖИВАЕМЫМ ПЕРИОДОМ АВТОНОМНОЙ РАБОТЫ | 2012 |

|

RU2522910C2 |

| Устройство ввода-вывода | 2020 |

|

RU2753980C1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2002 |

|

RU2221267C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

Мажоритарное устройство обработки аналоговой информации относится к автоматике и вычислительной технике и может быт«ь применено в автоматизированных системах контроля и управления технологическими процессами, в информационных измерительных системах высокой надежности. Цель изобретения - расширение области применения устройства за счет обработки группы аналоговых сигналов. Выбор подключаемого аналогового входа осуществляется с помощью переключателя. Момент подключения аналогового входа и порядок обработки информации задаются управляющим процессором. 10 ил.

ы

f

OJ

t-J

-4

S

s

SULtL

ФигЛ

BxodZ ( (Адресов

ВхоЗЗ

(Строба)

Фиг. 7

4°101

106

107

L

Фиг. в

$

Ъ

103

-

№

хГП

SF

2

1

fftf

о

///

Фиг. 9

Вх.-8ых. инф. ff-t-6-З

CmpoS(Ki) 37-1 - 37-3

Вых. синхр. 37-1-37-3

Ре кип к,Р

8хг$ш. инф. J7-4 - 37-6$

tmpob (К3) 37-4-Я-6

Режин (к,р) 37-b-37-S

вш. синхр. J7-4-J7-0

| Резервированная система | 1982 |

|

SU1101827A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Электроника, 1987, т | |||

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

Авторы

Даты

1992-05-30—Публикация

1988-08-15—Подача