Изобретение относится к Hhmynbc- ной и измерительной технике и может быть использовано при контроле отклонения частоты сигнала от эталонной в цифровых системах автоматического контроля и регулирования.

.Целью изобретения является расширение диапазона частот входных сигналов, повьшение помехоустойчивости (при повьшенных фазовых шумах входных сигналов).

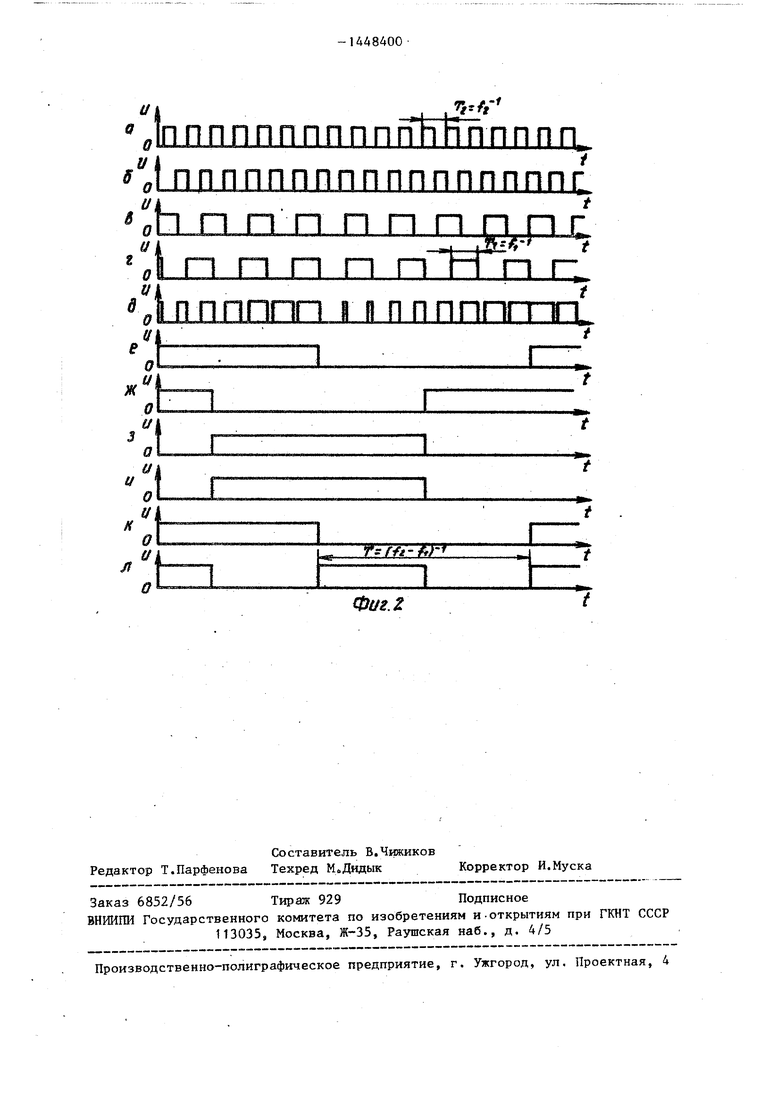

На фиг.1 изображена блок-схема предлагаемого устройства на фиг.2 - временные диаграммы.

Формирователь сигналов разностно частоты, содержит первый 1 и второй D-триггеры, входы которых соединены между собой, а первые выходы которых подключены соответственно к S- и R- входам первого Е-триггера 3, второй Е-триггер 4 и третий D-триггер 5 D- и С-входы которого подключены соответственно к выходам первого и второго Е-триггеров, а выход третьего р- триггера соединен с первой выходной шиной 6, первую и вторую входные и вторую выходную шины 7-9 соответственно , первый делитель 10 частоты на два, вход которого соединен с первой.входной шиной 7 формирователя сигнала разностной частоты, последовательно соединенные инвертор 1, второй делитель 12 частоты на два и первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ .13, второй вход которого подключен к выходу первого делителя 10 частоты на два, и второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 подключен к D-входам первого и второго D-триггера 1 и 2, выход инвертора 11 подключен к С-вхо ду первого D-триггера 1, вход инвертора 11 подключен к С-входу второго D-триггера 2 и соединен с второй входной шиной 8 формирователя сигнала разностной.частоты, S-вход второго Е-триггера 4 подключен к выходу первого D-триггера 1, а R-вход его соединен с инверсным выходом второго D-триггера 2, к выходам первого и второго Е-триггера 3 и 4 подключены входы второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14, выход которого соединен с второй выходной шиной 9,

Формирователь сигнала разностной частоты работает следующим образом.

Сигнал с частотой f (период Т ,) и любой скважностью поступает на пер25

30

.

10

15

20 354045 Q 55

484002

вую входную шину 7

и вызывает при переключении из состояния о в состояние 1 переключение, сигнала на выходе первого делителя 10 частоты на два в противоположное состояние (фиг.1). На выходе делителя 10 частоты на два скважность импульсов, независимо от скважности на его входе, равна двум (фиг.2г). Полагаем, что на вторую входную шину 8 поступает сигнал с частотой f (период Т,) .со скважностью, равной двум (фиг.2а). По переходам из состояния О в состояние 1 происходит тактирование D- триггера 2, а по обратным переходам (относительно второго входа) через инвертор 11 - тактирование D-триггера 1 (фиг.2 б). Одновременно с тактированием D-триггера 1 происходит тактирование делителя 12 частоты на два (фиг.2 в), который при этом переключается в противоположное состояние, и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13 (фиг.2д) инвертирует сигнал на входах D-триг- геров 1 и 2. Этот сигнал представляет собой импульсы с широтно-импульс- ной модуляцией. На выходах D-тригге- ров 1 и 2 выделяются импульсы с полуразностной частотой, со скважностью, равной двум, и взаимным фазовым сдвигом 90(фиг.2е,ж,з). Включение на выходах D-триггеров двух Е-триггеров (фиг.2и,к) предназначено для фильтрации нижних частот.

На выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 происходит удвоение полуразностных частот с результирующим значением, равным модулю разностной частоты, с периодом Т (f,2.f i) (фиг. 2 л). При помощи D-триггера 5 происходит определение знака разностной частоты, в данном случае при f, f г нэ выходе D-триггера 5 (фиг.2м) устанавливается состояние О. Рассмотрим работу формирователя при воздействии на второй вход сигнала со скважностью, отличной от двух. При этом фазовый сдвиг между сигналами полуразностной частоты на выходах D-.триггеров 1 и 2 отличен от 90, а это приводит только лишь к снижению допустимого уровня фазовьгх шумов во входных сигналах.

Предлагаемый формирователь сигнала разностной частоты работоспособен практически в неограниченном диапазоне частот входных сигналов (ограничение обусловлено лишь предельным быстродействием цифровых микросхем в отличие от устройства-прототипа, в котором для достижения того же эффекта необходимо изменять параметры элементов задержки в соответствии со значениями частот вхо5з,ных сигналов). В предлагаемом формирователе сигнала разностной частоты получена максимальная (оптимальная) помехоустойчивость при повьшенных фазовых шумах входных сигналов путем автоматической установки фазового сдвига 90 сигналов полуразностных частот. Формирователь работоспособен и при кратных частотах входных сигналов на первом входе (относительно частоты сигнала на втором входе). При этом на выходе знака разностной частоты формирователя знак меняется на противо7f

положный на частотах 3f,i, где 1 частота входного втором входе формирователя.

2 5

сигнала на

Формула изобретения Формирователь сигнала разностной частоты, содержащий первый и второй D-триггеры, D-входы которых соединены между собой, а первые выходы подключены соответственно к S- и Р- входам первого Е-триггера, второй Е-триггер и третий D-триггер. D- и С-входы которого подключены соответственно к выходам первого и второго Е-тркггеров, а выход третьего D-триг- гера соединен с первой выходной шиной, первую и вторую входные и вторую выходную шнны,

отличающийся тем, что, с целью расширения диапазона частот входных сигналов и повышения помехоустойчивости,

введены первый делитель частоты на два, вход которого соединен с первой входной шиной формирователя сигнала разностной частоты, последовательно соединенные инвертор, второй делитель частоты на два и первый элемент- ИСК-ПЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу первого делителя частоты на два, и второй элемент ИСКЛЮЧАЩЕЕ ИЛИ, выход первого эле мента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к

D-входу первого D-триггера, выход инвертора подключен к С-вхсду первого D-триггера, вход инвертора подсоединен к С-входу второго D-триггера.и

соединен с второй входной шиной формирователя сигнала разностной частоты, S-вход второго Е-триггера подключен к выходу первого D-триггера, а R-вход его подсоединен к инверсному

выходу второго D-триггера, к выходам первого и второго Е -триггеров подключены входы второго элемента ИСКЛЮЧМ)- ЩЕЕ ИЛИ, выход которого соединен с второй выходной шиной.

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Демодулятор сигналов частотной и фазовой телеграфии | 1981 |

|

SU1070683A1 |

| Делитель частоты с дробным коэффициентом деления | 1988 |

|

SU1596456A1 |

| Дискретное фазосдвигающее устройство | 1989 |

|

SU1666970A1 |

| ДИСКРЕТНЫЙ СОГЛАСОВАННЫЙ ФИЛЬТР | 2014 |

|

RU2589404C2 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Управляемый делитель частоты | 1984 |

|

SU1238234A1 |

| Цифровой усредняющий фазометр | 1983 |

|

SU1219982A1 |

| Устройство для автоподстройки частоты | 1983 |

|

SU1408529A1 |

| Измеритель разности фаз | 1990 |

|

SU1800382A1 |

Изобретение относится к импульсной и измерительной технике. Может быть использовано при контроле отклонения частоты сигнала от эталонной в цифровых системах автоматического контроля и регулирования. Цель.изобретения - расширение диапазона частот входных сигналов, повышение помехоустойчивости (при повышенных фазовых шумах входных сигналов). Устройство содержит D-триггеры 1 и 2; Е Тригге- ры 3 и 4; D-триггер 5. Введение делителя 10 частоты на два, инвертора 11, делителя 12 частоты на два, злемен- тов ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и 14 позволяет обеспечить работоспособность формирователя сигнала разностной частоты в диапазоне частот, ограниченном лишь предельны 5 быстродействием применяемых цифровых микросхем, и повысить помехоустойчивость при повышенных фазовых шумах входных сигаалов путем автоматической установки фазового сдвига 90 .сигналов попуразностных частот. 2 ил. с 5В (Л ф.

| Гутников B.C | |||

| Интегральная электроника в измерительных приборах | |||

| Л | |||

| : Энергия, 1974, с | |||

| Ударно-долбежная врубовая машина | 1921 |

|

SU115A1 |

| КАЧАЮЩИЙСЯ ПИТАТЕЛЬ | 1950 |

|

SU90502A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-30—Публикация

1987-01-07—Подача