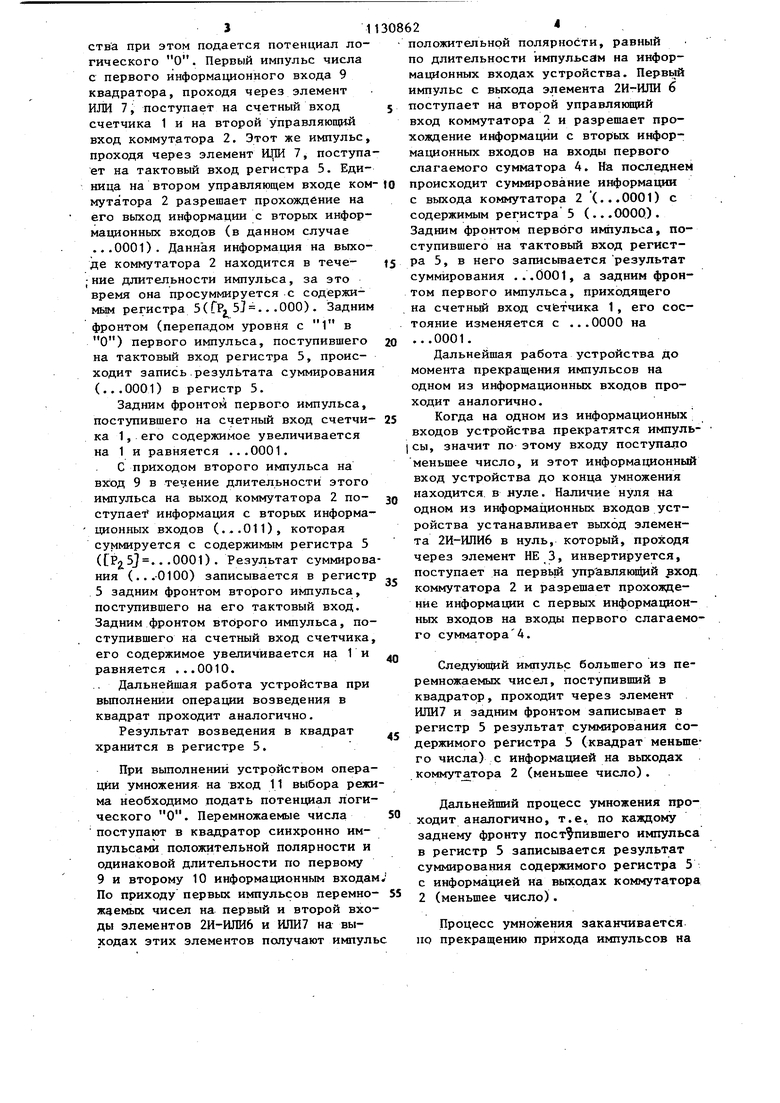

Изобретение относится к вычислительной технике и может быть использовано В цифровых измерительных приборах,: а также для обработки информации, представленной число-импульсным кодом. Известен квадратор, содержащий двоичный счетчик, линию задержки, триггер, сумматор и элементы И tij Недостатками такого квадратора яв ляются сложность схемой реализации и ограниченные функциональные возмож ности. Наиболее близким по технической сущности к предлагаемому является устройство, содержащее двоичный счет чик, разрядные выходы которого соеди нены с первыми входами элементов И, выходы которых соединены с разрядными входами сумматора, информационный .вход квадратора соединен со счет ным входом триггера второго разряда двоичного счетчика и вторыми входами элементов И C2J. Недостатком устройства является невозможность выполнения операции ум ножения . Цель изобретения - расширение области применения путем обеспечения возможности выполнения операций возведения- в квадрат и умножения. Поставленная цель достигается тем что в вычислительное устройство, содержащее счетчик и сумматор, допол нительно введены коммутатор, регистр элемент. НЕ, элемент ИЛИ, элемент 2И-И11И, первый вход которого соединен с первым информационным входом устройства и первым входом элемента ИЛИ, второй вход которого соединен с вторым информационным входом устройства и вторым входом элемента 2ИИЛИ, третий вход которого соединен . с входом выбора режима устройства, «Четвертый вход элемента 2И-ШШ объединен со своим первым входом, выход элемента 2И-ШШ соединен со счетным входом счетчика, первым управляющим входом коммутатора и входом элемента НЕ, выход которого соединен с вторым управлягадим входом коммутатора, первая группа информационных вхо дов которого соединена с разрядными выходами счетчика соответственно, вторая группа информационных входов коммутатора соединена с разрядными выходами счетчика со сдвигом на один разряд в сторону старших разрядов. причем вход старшего разряда первой группы информацнонных входов коммутатора соединен с шиной логического О, вход младшего разряда второй группы информационных входов коммутатора соединен с шиной логической 1, выходы коммутатора соединены с входами (h+1) младших разрядов первого слагаемого сумматора, входы первого слагаемого Oi-1) старших разрядов которого соединены с шиной логического О (где п - разрядность счетчика), разрядные выходы сумматора соединены соответственно с информационными входами регистра, разрядные выходы которого соединены соответственно с входами второго слагаемого сумматора, тактовый вход регистра соединен с выходом элемента ИЛИ. На чертеже показана блок-схема вычислительного устройства. Квадратор содержит счетчик 1, коммутатор 2, -элемент НЕ 3, сумматор 4, регистр 5, элемент 2Й-ИЛИ 6, элемент ИЛИ 7, вход 8 сброса устройства, первый и второй, информационные входы 9 и 10 устройства соответственно, вход 11 задания режима. Работа устройства при вьшолнении операции возведения в квадрат основана на реализации зависимости . .((2i.-1) ), где m - число, возводимое в квадрат. Работа устройства при выполнении операции умножения сводится к выполнению операции возведения в квадрат меньшего из перемножаемых чисел, и прибавлению к полученно гу результату э,того меньшего числа такое количество раз, которое равно, разности между перемножаемыми числами rhi4m(K-mJ, т-кU KCm-K}, ПРИ , где m и k - перемножаемые числа. Перед началом работы устройства на вьпсод 8 сброса устройства подается импульс отрицательной полярности, который производит установку счетчика 1 и регистра 5 в нулевое состояние . Для выполнения устройством операции возведения в квадрат на вход 11 выбора режима необходимо подать потенциал логической 1. Число, возводимое в квадрат, поступает по первому информационному входу 9 импульсами положительной полярности. На второй информационный вход 10 устройства при этом подается потенциал логического О. Первый импульс числа с первого информационного входа 9 квадратора, проходя через элемент ИЛИ 7, поступает на счетный вход счетчика 1 и на второй управляющий вход коммутатора 2. Этот же импульс, проходя через элемент ЩШ 7, поступа ет на тактовый вход регистра 5. Единица на втором управляющем входе ком мутатора 2 разрешает прохождение на его выход информации с вторых информационных входов (в данном случае ...0001). Данная информация на выходе коммутатора 2 находится в тече;ние длительности импульса, за это время она просуммируется с содержимым регистра 5 ( .. .000) . Задним фронтом (перепадом уровня с 1 в О) первого импульса, поступившего на тактовый вход регистра 5, происходит запись результата суммирования (...0001) в регистр 5. Задним фронто первого импульса, поступившего на счетньй вход счетчи- ка 1, его содержимое увеличивается на 1 и равняется ...0001. С приходом второго импульса на вход 9 в течение длительности этого импульса на выход коммутатора 2 поступает информация с вторых информа ционных входов (...011), которая суммируется с содержимым регистра 5 (Pjr 5j.. .0001) . Результат суммирова ния (...-0100) записывается в регистр 5 задним фронтом второго импульса., поступившего на его тактовый вход. Задним фронтом второго импульса, поступившего на счетный вход счетчика его содержимое увеличивается на 1 и равняется ... 0010. Дальнейшая работа устройства при вьтолнении операции возведения в квадрат проходит аналогично. Результат возведения в квадрат хранится в регистре 5. При выполнении устройством операции умножения на вход 11 выбора режи ма необходимо подать потенциал логического О. Перемножаемые числа поступают в квадратор синхронно импульсами положительной полярности и одинаковой длительности по первому 9 и второму 10 информационным входам По приходу первых импульсов перемножземых чисел на первый и второй входы элементов 2И-ИЛИ6 и ИЛИ7 на выходах этих элементов получают импул положительной полярности, равный по длительности импульсам на информационных входах устройства. Первьй импульс с выхода элемента 2И-ИЛИ б поступает на второй управляющий вход коммутатора 2 и разрешает прохождение информации с вторых информационных входов на входы первого слагаемого сумматора 4. На последнем происходит суммирование информации с выхода коммутатора 2 (...0001) с содержимым регистра 5 ( .. .0000.) . Задним фронтом первого импульса, поступившего на тактовый вход регистра 5 , в него записьгаается результат суммирования ...0001, а задним фронтом первого импульса, приходящего на счетный вход счЬтчика 1, его состояние изменяется с ...0000 на ...0001. Дальнейшая работа устройства до момента прекращения импульсов на одном из информационных входов проходит аналогично. Когда на одном из информационных входов устройства прекратятся импульсы, значит по- этому входу поступало меньшее число, и этот информационный вход устройства до конца умножения находится в нуле. Наличие нуля на одном из информационных входов устройства устанавливает выход элемента 2И-ИЛИ6 в нуль, который, проходя через элемент НЕ 3, инвертируется, поступает на первьй управляющий вход коммутатора 2 и разрещает прохождение информации с первых информационных входов на входы первого слагаемого сумматора4. Следуюп ий импульс большего из перемножаемых чисел, поступивший в квадратор, проходит через элемент ШШ7 и задним фронтом записывает в регистр 5 результат суммирования содержимого регистра 5 (квадрат меньшего числа) с информацией на выходах коммутатора 2 (меньшее число). Дальнейший процесс умножения проходит аналогично, т.е. по каждому заднему фронту пост пившего импульса в регистр 5 записывается результат суммирования содержимого регистра 5 с информацией на выходах коммутатора 2 (меньшее число). Процесс умножения заканчивается по прекращению прихода импульсов на S информационные входы устройства, зультат умножения записывается в гистре 5. ре-; По сравнению с известным предларе- гаемое устройство применяется для ре.11308626 шения более широкого круга задач.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1984 |

|

SU1242938A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Генератор нормально распределенных случайных величин | 1984 |

|

SU1244664A1 |

| Устройство для возведения в степень | 1983 |

|

SU1087990A1 |

| Медианный фильтр | 1988 |

|

SU1562902A1 |

| Устройство для контроля аналоговых объектов | 1989 |

|

SU1718189A1 |

| Устройство для вычисления средне-КВАдРАТичЕСКОгО зНАчЕНия | 1979 |

|

SU849229A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1686439A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее счетчик и сумматор, о т личающеес-я тем, что, с целью расширения области применения путем обеспечения возможности выполнения операций умножения, в него введены коммутатор, регистр, элемент НЕ, I элемент ИЛИ, элемент 2И-ИЛИ, первый вход которого соединен с первым информационным входом устройства и первьпч входом элемента ИЛИ, второй вход которого соединен с вторым информационным входом устройства и вторым входом элемента 2И-ИЛИ, третий вход которого соединен с входом выбора режима устройства, четвертый вход элемента 2И-ИЛИ объединен со своим первым входом, выход элемента 2И-ИЛИ соединен со счетным входом счеТчика, первым управляющим входом коммутатора и входом элемента НЕ, выход которого соединен с вторым управляющим входом коммутатора, первая группа информационных входов которого соединена с разрядными выходами счетчика соответственно, вторая группа информационных входов коммутатора соединена с разрядными выходами счетчика со сдвигом на один разряд в сторону старших разрядов, причем вход старшего разряда первой группы.информационных входов коммутатора соединен с шиной логического О, вход младшего разряда второй группы информационных входов коммутатора соединен с шиной логической 1, выходы коммутатора (Л соединены с входами (п+1) младших разрядов первого слагаемого сумматора, входы первого слагаемого (п-1) старших разрядов которого соединены с шиной логического О (где п - разрядность счетчика), разрядные выходы сумматора соединены соответствен00 О X 3d но с информационными входами регистра, разрядные вьпсоды которого соединены соответственно с входами второго слагаемого сумматора, тактовый вход регистра соединен с выходом мента ИЛИ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Мельников А.А | |||

| и др | |||

| Обработка частотных и временных импульсных сигналов | |||

| М., Энергия, 1976, с | |||

| Шланговое соединение | 0 |

|

SU88A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Квадратор | 1978 |

|

SU769537A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-23—Публикация

1983-09-22—Подача