Изобретение относится к импульсной технике и может быть использовано в устройствах синхронизации цифровых систем передачи данных. I Цель изобретения - расширение функциональных возможностей путем обеспечения получения любых целочисленных коэффициентов умножения, задаваемых программно изменением входного кода.

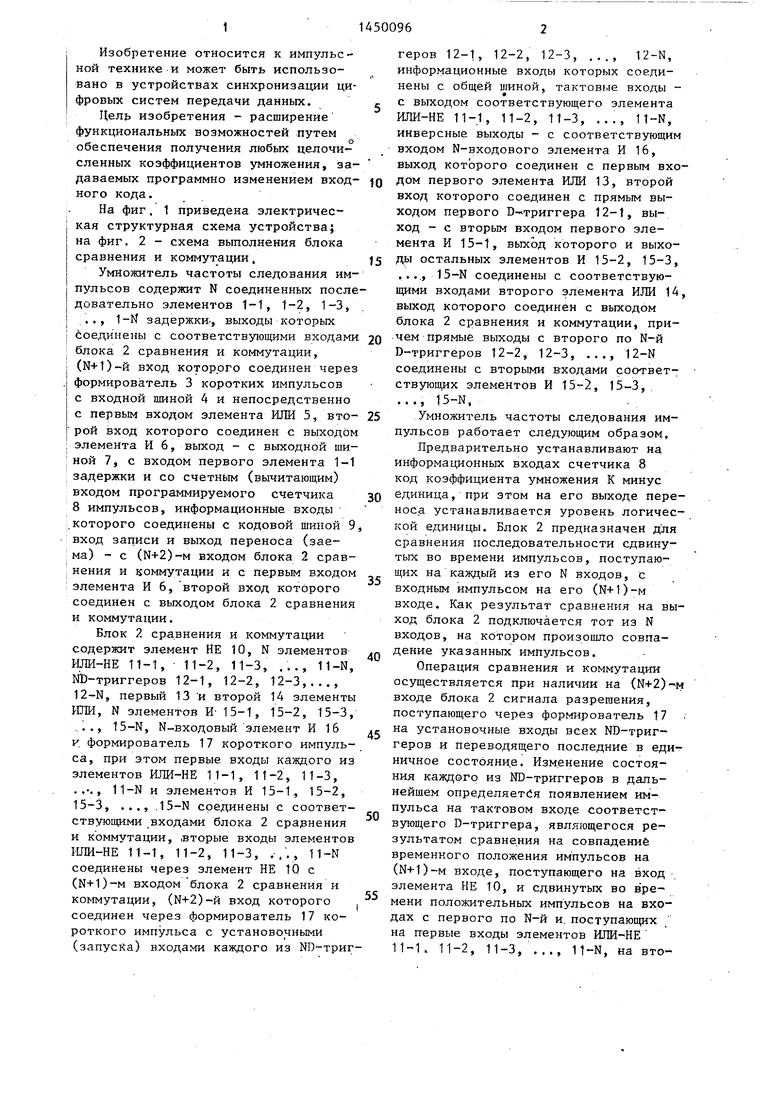

На фиг. 1 приведена электричес- I кая структурная схема устройства; I на фиг. 2 - схема выполнения блока I сравнения и коммутации,

Умножитель частоты следования им- j пульсов содержит N соединенных после I довательно элементов 1-1, 1-, 1-3, I ..., 1-N задержки., выходы которых i Соединены с соответствующими входами : блока 2 сравнения и коммутации, I ()-й вход которого соединен через I формирователь 3 коротких импульсов I с входной шиной 4 и непосредственно I с первым входом элемента ИЛИ 5, вто- I рой вход которого соединен с выходом ; элемента И 6, выход - с выходной ши- : ной 7, с входом первого элемента 1-1 ; задержки и со счетньш (вычитающим) входом программируемого счетчика 8 импульсов, информационные входы ;. которого соединены с кодовой шиной 9 вход записи и выход переноса (зае- ; ма) - с (N+2)-M входом блока 2 срав- ;нения и коммутации и с первым входом элемента И 6, второй вход которого соединен с выходом блока 2 сравнения и коммутации.

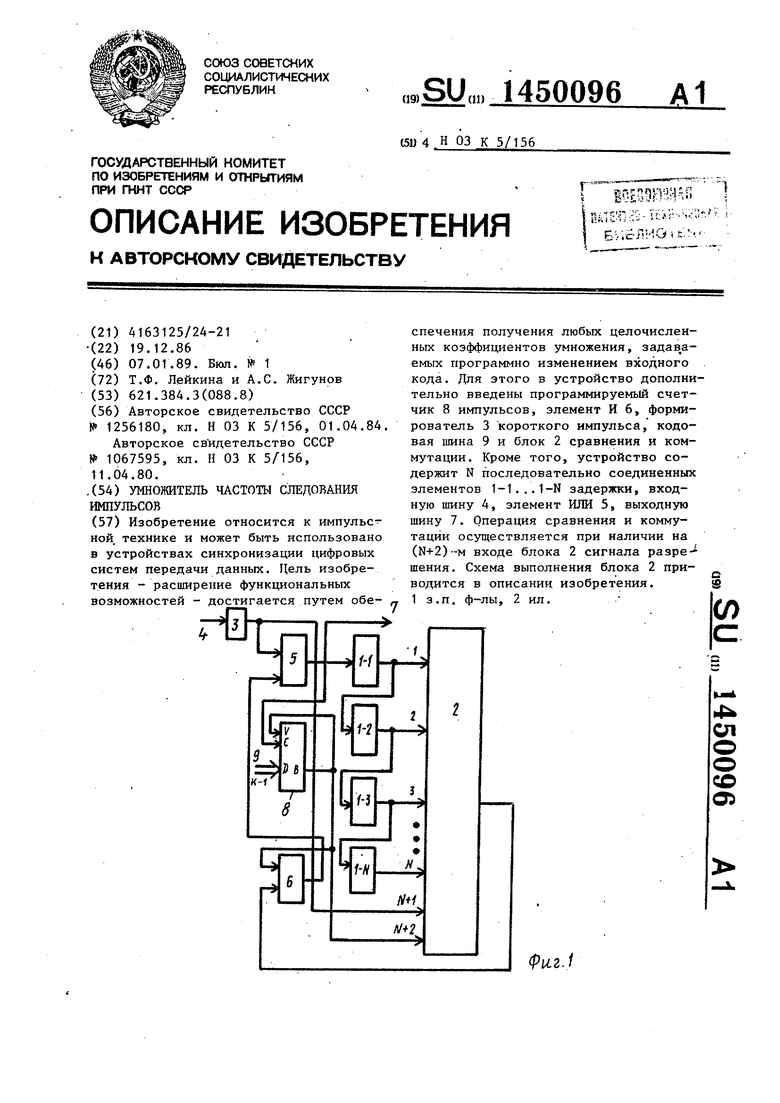

Блок 2 сра.внения и коммутации содержит элемент НЕ 10, N элементов ШШ-НЕ 11-1, 11-2, 11-3, ..., 11-N, Nb-триггеров 12-1, 12-2, 12-3,.,., 12-N, первый 13 и второй 14 элементы ИЛИ, N элементов И 15-1, 15-2, 15-3, ..., 15-N, N-входовый элемент И 16 и формирователь 17 короткого импульса, при этом первые входы каждого из элементов ИЛИ-НЕ 11-1, 11-2, 11-3, . ,-., 11-N и элементов И 15-1, 15-2, 15-3, ... .15-N соединены с соответствующими входами блока 2 сравнения и коммутации, .вторые входы элементов 1ШИ-НЕ 11-1, 11-2, 11-3, ./. , 11-N соединены через элемент НЕ 10 с (N+1)-M входом блока 2 сравнения и коммутации, (Ы+2)-й вход которого соединен через формирователь 17 короткого импульса с установочными (запуска) входами каждого из ND-триг0

5

0

геров 12-1, 12-2, 12-3, ,.., 12-N, информационные входы которых соединены с общей шиной, тактовые входы - с выходом соответствующего элемента ШШ-НЕ 11-1, 11-2, 11-3, ,.., 11-N, инверсные выходы - с соответствующим входом N-входового элемента И 16, выход которого соединен с первым входом первого элемента ИЛИ 13, второй вход которого соединен с прямым выходом первого D-триггера 12-1, выход - с вторым входом первого элемента И 15-1, выход которого и выходы остальных элементов И 15-2, 15-3, ...., 15-N соединены с соответствующими входами второго элемента ИЛИ 14, выход которого соединен с выходом блока 2 сравнения и коммутации, причем прямые выходы с второго по N-й

D-триггеров 12-2, 12-3,

12-N

5

0

5

0

5

0

5

соединены с вторыми входами соответствующих элементов И 15--2, 15-3, ..., 15-N.

Умножитель частоты следования импульсов работает следующим образом,

Предварительно устанавливают на информационных входах счетчика 8 код коэффициента умножения К минус единица, при этом на его выходе переноса устанавливается уровень логической единицы. Блок 2 предназначен для сравнения последовательности сдвинутых во времени импульсов, поступающих на каждый из его N входов, с входным импульсом на его ()-M входе. Как результат сравнения на выход блока 2 подключается тот из N входов, на котором произошло совпадение указанных импульсов.

Операция сравнения и коммутации осуществляется при наличии на (N+2)-M входе блока 2 сигнала разрешения, поступающего через формирователь 17 на установочные входы всех ND-триг- геров и переводящего последние в единичное состояние. Изменение состояния каждого из ND-триггеров в дальнейшем определяется появлением импульса на тактовом входе соответствующего D-триггера, являющегося результатом сравнения на совпадение временного положения импульсов на (N+1)-M входе, поступающего на вход элемента НЕ 10, и сдвинутых во в ре- мени положительных импульсов на входах с первого по N-й и. поступающих на первые входы элементов ИЛИ-НЕ 11-1. 11-2, 11-3, ..., 1t-N, на ВТОрые входы которых поступает инвертированный сигнал с (N+1)-ro входа. В результате сравнения на выходах всех элементов ИЛИ-НЕ появляются импульсы, кроме того, в котором прои- зошло точное совпадение импульсов во времени. Это означает, что только один из ND-триггеров не изменит своего состояния и сохрани г разрешение на прохождение импульсов через соответствующий элемент И на выход блока 2. В исходном состоянии или при несовпадении исходного импульса ни с каким из N входных импульсов в блоке 2 разрешено прохождение сигнала на выход с его первого входа.

Работа устройства начинается, когда первый импульс с выхода формирователя 3 через элемент 5 поступает на шину 7 и на вход элемента J-1, с выхода которого импульс, за держанный на время U,, поступает на первый вход блока 2 и на вход элемента 1-2, на выходе, которого появляется импульс, задержанный на время l, поступающий на второй вход блока 2 и на вход элемента 1-3, и так далее. Таким образом, на каждом из N входов блока 2 образуются смещенные относительно друг друга импульсы. Так как в исходном состоянии в блоке 2 соединен первый его вход с выходом, то сначала на второй вход элемента 5 через элемент 6 поступает импульс, задержанный элементом

вход элемента 1 самым на N вход смещенные во вр друг друга импу импульса на (N+ соответствующег на входе шины 4 сравнения и пере 10 входа на выход б торого совпал с входе, и цикл ум ся. В этом случа связи окажется п 15 па элементов 1-1 по i-ю, период в дет определяться в элементах заде и задержки в эле 20 ке 2. Это подклю тех пор, пока по сигнала совпаден гому i-входу.

Времена задер 25 ки выбираются сл ли fj и f gj, ная и выходная ч cooTBetcTBeHHo п выходного сигнал

30

в MX

Тьх

где К 35

коэффици целое чи Тогда для элем

которое и опредегде

Ь -2.

40

1-1 на время

яет вместе с задержкой в блоке 2 элементах 5 и 6 период выходного игнала .- С выхода элемента 5 импульс оступает также на счетный вход счетика 8, в котором из кода (К-1), со- ержащегосй в последнем, вычитается исло импульсов, прошедших на шину 7.

роцесс многократного прохождения им- 45 (с учетом знака): ульса через элемент 1-1 продолжаетя до тех пор, пока содержимое счетика 8 не обнулится. В результате а вьгходе переноса сигнал меняет остояние с логической единицы на уль, который запрещает прохождение адержанных импульсов через элемент и элемент 5 на шину 7. Этот импульс

бих

- суммар ментах Для каждого по задержки время за из известной врем сти первого элеме превьш1ающей допус

S.

вцх

51

50

и известного откл

значения Т

от

дновременно поступает на (Ы+2)-й ход блока 2, давая разрешение на равнение. Последний из серии задеранных импульсов, который обнуляет четчик 8, поступает также на вход лемента 1-1, затем с его выхода на

Sr

55

Если по програм ваться формировани

то Di; i

).

fidix {

-

вход элемента 1-2 и так далее, тем самым на N входах блока 2 образуются смещенные во времени относительно друг друга импульсы. При появлении импульса на (N+1)-M входе блока 2, соответствующего следующему импульсу на входе шины 4, начинается операция сравнения и переключения того i-ro входа на выход блока 2, импульс которого совпал с импульсом на (N+1)-M входе, и цикл умножения продолжается. В этом случае в кольцо обратной связи окажется подключенной уже груп- па элементов 1-1, 1-2, .,, с первой по i-ю, период выходного сигнала будет определяться суммарной задержкой в элементах задержки с первой по i-ю и задержки в элементах 5 и 6 и в бло- ке 2. Это подключение сохраняется до тех пор, пока по приходу входного сигнала совпадение произойдет по другому i-входу.

Времена задержек элементов задерж- ки выбираются следующим образом. Если fj и f gj, соответственно входная и выходная частоты, то Т и Tg, - cooTBetcTBeHHo периоды входного и выходного сигнала:

в MX

Тьх

BOX

i-ey

где К

коэффициент умножения, любое целое число. Тогда для элемента 1-1:

где

Ь -2.

0

5 (с учетом знака):

бих

- суммарная задержка в элементах 5 и 6 и в блоке 2. Для каждого последующего элемента задержки время задержки определяется из известной временной нестабильности первого элемента задержки ,, превьш1ающей допустимое значение ЛТа«,(

45 (с учетом знака):

S.

вцх

Ч

51

4

50

4i

и известного отклонения

значения Т

от

Sr

5

V- Если по программе может потребоваться формирование различных Т

то Di; i

).

fidix {

- (( )

9ых;

+

Формула изобретения

I - .

I 1. Умножитель частоты следования

|1мпульсов, содержащий N последовате- hbHo соединенных элементов задержки, бзсодную шину и элемент ИЛИ, выход ко- Iroporo соединен с выходной шиной. Отличающийся тем, что, I целью расширения функциональных ю зозможностей, в него введены програм;жируемый счетчик импульсов, элемент i, формирователь короткого импульса, одовая шина и блок сравнения и ком- : 1утации, первые N входов которого 15 соединены с выходами соответствующих элементов задержки, (Ы+1)-й вход соединен с выходом формирователя корот- kHx импульсов, вход которого подклю- .цен к входной шине, и с первым вхо- 20 элемента ИЛИ, выход которого сое- инен с входом первого элемента заЬержки и со счетным входом програм- |4ируемого счетчика импульсов, инфор | 1ационные входы которого соединены |с кодовой шиной, вход записи и выход |переноса - с (N+2)-M входом блока Сравнения и коммутации и с первым ходом элемента И, выход которого роединен с вт орым входом элемента КЛИ, второй вход - с выходом блока сравнения и коммутации. : 2. Умножитель по п. 1, отличающийся тем, что блок сравнения и 5;:оммутации содержит элемент НЕ, N элементов ИЛИ-НЕ, ND-тригге25

30

2g

5 0

ров, (N+1) элементов И, первый и второй элементы ИЛИ, формирователь короткого импульса, (N+2) входов и один выход, при этом (Ы+1)-й вход блока сравнения и коммутации подключен к входу элемента НЕ, выход которого подключен к первым входам N элементов ИЛИ-НЕ, выход каждого из которых подключен к С-входам соответствующих с первого по N-й D-триг- геров, прямые выходы с второго по N-й из которых соединены с первыми входами соответствующих элементов И,

выходы которых с первого по N-й подключены к N входам второго элемента ИЛИ, выход которого является выходом блока сравнения и коммутации,, инверсные выходы ND-триггеров соединены с N входами (N+1)-ro элемента И, «ьгход которого соединен с первым входом первого элемента ИЛИ, к второму входу которого подключен прямой выход первого D-триггера, S-входы

5 каждого D-триггера соединены с выходом формирователя короткого импульса, вход которого является (N+2)-M входом блока сравнения и коммутации, D-вхрды ND-триггеров подключены к

0 уровню логического нуля, входы блока сравнения и коммутации с первого. по N-й соединены с вторыми входами соответствующих элементов И, выход первого элемента ИЖ соединен с перg вым входом первого элемента из N элементов И.

Вх{Л/ 2)

F i7

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОПРЕДЕЛЕНИЯ ВЕСОВЫХ ХАРАКТЕРИСТИК ДОСТОВЕРНОСТИ ДЛЯ ОБРАБОТКИ ПРИНЯТЫХ МНОГОПОЗИЦИОННЫХ СИГНАЛОВ | 2007 |

|

RU2339164C1 |

| Каскадный коммутатор | 1989 |

|

SU1608792A1 |

| АССОЦИАТИВНЫЙ КОММУТАТОР | 1991 |

|

RU2101760C1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1798743A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для контроля модулей коммутации | 1984 |

|

SU1273931A1 |

| Коммутационное устройство | 1985 |

|

SU1285486A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Система коммутации | 1986 |

|

SU1354200A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах синхронизации цифровых систем передачи данных. Цель изобретения - расширение функциональных возможностей - достигается путем обеспечения получения любых целочисленных коэффициентов умножения, задав а- емых программно изменением входного кода. Для этого в устройство дополнительно введены программируемый счетчик 8 импульсов, элемент И 6, формирователь 3 короткого импульса, кодовая шина 9 и блок 2 сравнения и коммутации. Кроме того, устройство содержит N последовательно соединенных элементов 1-1...1-N задержки, входную шину 4, элемент ИЛИ 5, выходную шину 7. Операция сравнения и коммутации осуществляется при наличии на (N+2)--M входе блока 2 сигнала разре- шения. Схема выполнения блока 2 приводится в описании изобретения. 1 3.п. ф-лы, 2 ил. i (Л 42ь 01 СО О) (plLZ.I

)

iO

fi-H

ii-5

ii-2

r //-/

BX.N o--

5л: J

оВх.2

Bx.i

Ln

16

i2-2

r

r

12-1

i5-N

гЛ

J r

r I

1f1

Вых

l-

15-1

Фие.2

| Умножитель частоты следования импульсов | 1984 |

|

SU1256180A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты | 1980 |

|

SU1067595A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-01-07—Публикация

1986-12-19—Подача