Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых устройств повьшенной надежности.

Цель изобретения повьшение быстродействия контролируемого ариф метического устройства.

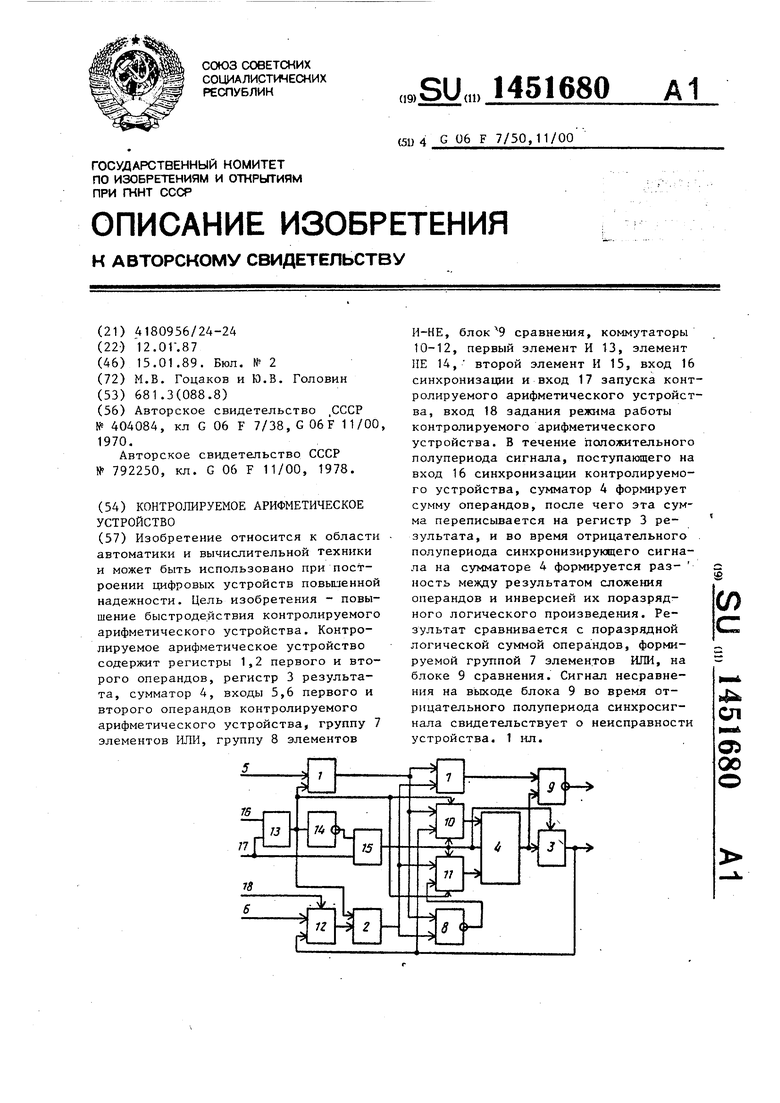

На чертеже представлена схема контролируемого арифметического уст ройства.

На схеме обозначены регистры 1 и 2 первого и второго операндов, регистр 3 результата, сумматор 4, вхо ды 5 и 6 первого и второго операн- .дов контролируемого арифметического устройства, блок 7 элементов ИЛИ, блок 8 элементов И-НЕ, блок 9 срав

нения, коммутаторы 10- 12, первый элемент И 13 элемент НЕ 14, второй элемент И 15, вход 16 синхронизации и вход 17 запуска контролируемого арифметического устройства, а также вход 18 задания режима работы контролируемого арифметического устройства .

Устройство работает следующим образом.

На вход 17 запуска контролируемого арифметического устройства подаётся единичный сигнал. На вход 16 синхронизацир контролируемого арифметического устройства поступают импульсы синхронизации, и с выходов элементов И 13 и 15 снимаются сигналы для управления работой узлами устройства. Сигнал с выхода первого элемента И 13 поступают на входы записи регистров 1 и 2 операндов, сигнал с выхода второго элемента И 15 - на вход записи регистра 3 результата.

По положительному фронту синхроимпульсов информация с входов 5 и 6 первого и второго операндов контролируемого арифметического устройства записывается в регистры 1 и 2 первого и второго операндой. В это время на выходы коммутаторов 10 и 11 проходят сигналы с первых информационных входов. Таким образом, на входы первого и второго операндов сумматора 4 проходит содержимое регистров 1 и 2 операндов (на вход переноса сумматора 4 поступает нулевой сигнал с выхода элемента И 15). По окончании положительного импульса синхронизации содержимое сумматора 4

0

0

5

0

5

0

5

0

5

записывается в регистр 3 результата. При этом вторые информационные входы коммутаторов 10 и 11 оказываются подключенными к выходам этих коммутаторов. Таким образом, на вход первого операнда сумматора 4 поступает результат сложения операндов, на вход второго операнда - инверсия поразрядного логического умножения первого и второго операндов, а на вход переноса единичный сигнал.

На выходе сумматора 4 образуется разность между суммой операндов и их поразрядным логическим произведением. При правильной работе контролируемого арифметического устройства эта разность должна быть равной результату поразрядной логической суммы двух операндов, которая подсчитывается блоком 7 элементов ИЛИ.

Правильность работы устройства контролируется блоком 9 сравнения, единичный сигнал на выходе которого во время действия отрицательного сигнала на входе 16 синхронизации контролируемого арифметического устройства свидетельствует о неисправности устройства.

С помощью сигнала, поступающего на вход 18 задания режима работы контролируемого арифметического устройства, можно подключать к информационному входу регистра 2 второго операнда либо результат предыдущего сложения, либо число с входа 6 второго операнда контролируемого арифметического устройства.

Формула изобретения

Контролируемое арифметическое устройство, содержащее два регистра операндов, регистр результата, блок элементов ИЛИ , блок элементов И-НЕ, сумматор, блок сравнения, причем информационный вход регистра первого операнда является входом первого операнда контролируемого арифметического устройства, информационные выходы регистров первого и второго операндов соединены соответственно с первым и вторым входами блока элементов ИЛИ, выход результата сумматора соединен с информадаонньм входом регистра результата и первым информационным входом блока сравнения, выход которого является выходом

31451

неисправности контролируемого арифметического устройства, информационный выход регистра результата является информационным выходом контролируемого арифметического устройства, информационные выхЬды регистров первого и операндов соединены соответственно с первым и вторым входами бло

входом регистра второго операнда, информационный выход регистра результата соединен с вторым информационным входом первого коммутатора, выход блока элементов И-НЕ соединен с вторым информационным входом второго коммутатора, первый вход первого элемента И является входом синхрони

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Операционное устройство микропроцессора | 1979 |

|

SU1164719A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1312611A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении цифровых устройств повышенной надежности. Цель изобретения - повышение быстродействия контролируемого арифметического устройства. Контролируемое арифметическое устройство содержит регистры 1,2 первого и второго операндов, регистр 3 результата, сумматор 4, входы 5,6 первого и второго операндов контролируемого арифметического устройства, группу 7 элементов ИЛИ, группу 8 элементов И-НЕ, сравнения, коммутаторы 10-12, первый элемент И 13, элемент НЕ 14, второй элемент И 15, вход 16 синхронизации и вход 17 запуска контролируемого арифметического устройства, вход 18 задания режима работы контролируемого арифметического устройства. В течение положительного полупериода сигнала, поступающего на вход 16 синхронизации контролируемого устройства, сумматор 4 формирует сумму операндов, после чего эта сумма переписьшается на регистр 3 результата, и во время отрицательного полупериода синхронизирующего сигнала на сумматоре 4 формируется раз- ность между результатом сложения операндов и инверсией их поразрядного логического произведения. Результат сравнивается с поразрядной логической суммой операндов, формируемой группой 7 элементов ИЛИ, на блоке 9 сравнения. Сигнал несравнения на выходе блока 9 во время отрицательного полупериода синхросигнала свидетельствует о неисправности устройства. 1 ил. 1 (Л 4 ел О5 00

ка элементов И-НЕ, о т л и ч а ю щ зации контролируемого арифметичесе с я тем, что, с целью повышения быстродействия контролируемого арифметического устройства, в него введены три коммутатора, два элемента И, элемент НЕ, причем информаци- онньй выход регистра первого операнда соединен с первым информационным входом первого коммутатора, выход которого соединен с входом первого операнда сумматора, информационный выход регистра второго операнда соединен с первым информационным входом (Второго коммутатора, выход которого соединен с входом второго операнда сумматора,первый информационный вход третьего коммутатора является входом второго операнда контролируемого арифметического устройства, информационный выход регистра результата соединен с вторым информационным входом третьего коммутатора, выход которого соединен с информа дионным

кого устройства, выход первого элемента И через элемент НЕ соединен с первым входом второго элемента И, выход которого соединен с входом

15 переноса сумматора,вторые входы пер го и второго элементов И объединены и образуют вход запуска контролируемо го арифметического устройства, выход первого элемента И соединен с

2Q входами записи регистров первого и второго операндов и первыми управляющими входами первого и второго коммутаторов, выход второго элемента И соединен с входом записи регис

25 ра результата и вторыми управляющим входами первого и второго коммутаторов, управляющий вход третьего коммутатора является входом задания режима работы контролируемого арйф2Q метического устройства, выход блока элементов ИЛИ соединен с вторым информационным входом блока сравнения

кого устройства, выход первого элемента И через элемент НЕ соединен с первым входом второго элемента И, выход которого соединен с входом

переноса сумматора,вторые входы первого и второго элементов И объединены и образуют вход запуска контролируемого арифметического устройства, выход первого элемента И соединен с

входами записи регистров первого и второго операндов и первыми управляющими входами первого и второго коммутаторов, выход второго элемента И соединен с входом записи регистра результата и вторыми управляющими входами первого и второго коммутаторов, управляющий вход третьего коммутатора является входом задания режима работы контролируемого арйфметического устройства, выход блока элементов ИЛИ соединен с вторым информационным входом блока сравнения.

| Авторское свидетельство ,СССР № 404084, кл G 06 F 7/38, G 06F 11/00, 1970, Авторское свидетельство СССР № 792250, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1987-01-12—Подача