(21)4270396/24-24

(22)29.06.87

(46) 15.01.89. Бюл. № 2

(71)Таганрогский радиотехнический институт им. В.Д.Калмыкова

(72)В.Е.Золотовский и Р.В.Коробков (53) 681.325 (088.8)

(56) Авторское свидетельство СССР № 1146662, кл. G 06 F 7/552, 1985.

Авторское свидетельство СССР № 1283810, кл. G 06 F 7/552, 1985.

(54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ

(57) Изобретение относится к вычисп лительной технике и может быть использовано при построении универ- сальньпс и специализированных цифровых вычислительных машин. Целью изобретения является упрощение устройства. Эта цель достигается тем, .что в устройство, содержащее два регистра 1,2, сумматор 3, элемент НЕ 4, введен элемент И 5. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1988 |

|

SU1571581A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1283810A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1015380A1 |

| ОПТИЧЕСКИЙ СТРАНИЧНЫЙ ВЫЧИСЛИТЕЛЬ КВАДРАТНОГО КОРНЯ | 1986 |

|

SU1367753A1 |

| Устройство для вычисления корня @ -степени | 1986 |

|

SU1381494A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Устройство для извлечения квадратного корня | 1980 |

|

SU942005A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

ГО 71

f

«

(Л

4i СП

СЬ 00 ч|

Изобретение относится к вычислительной технике, и предназначено для использования в цифровых вычислительных машинах различного.назначения,

Цель изобретения - упрощение устройства.

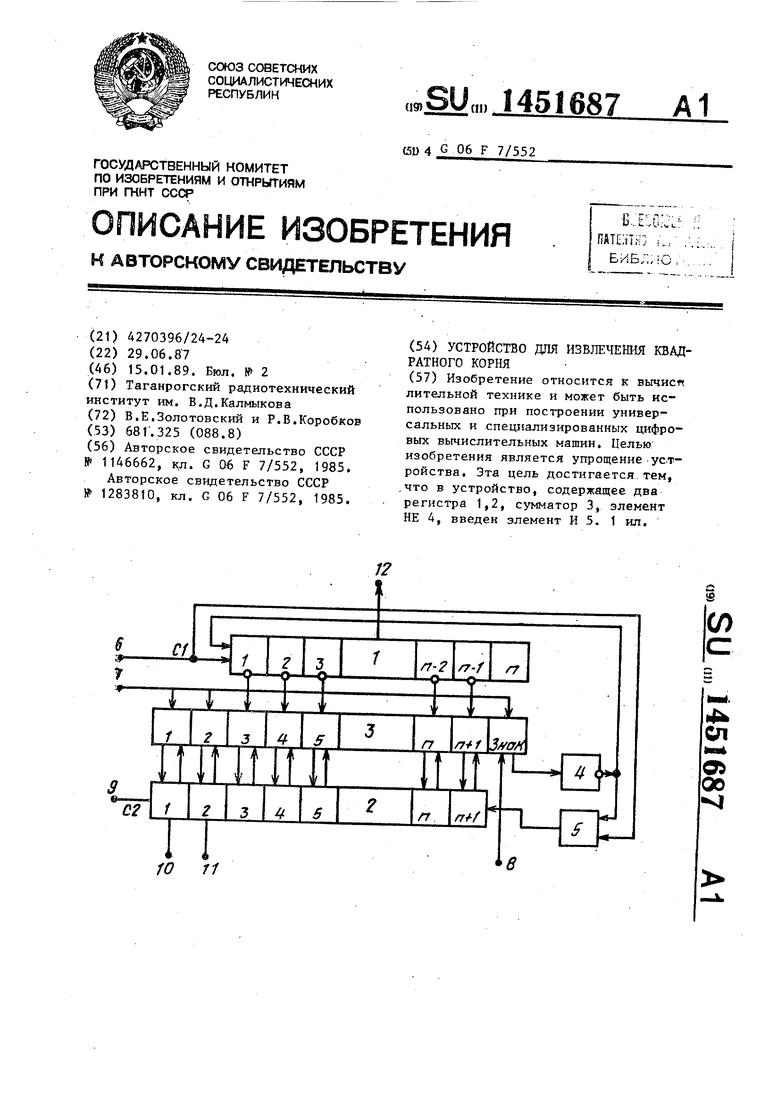

На чертеже представлена структурная схема устройства.

На схеме обозначены регистры 1 и 2, сумматор 3,. элемент НЕ 4, элемент И 5, входы 6 - 11 и выход 12 устройства.

Устройство работает следующим образом.

Перед началом операции регистры

1и 2 сброшены в ноль. На входы 10 и 11 подается старшая пара разрядов подкоренного числа. На первые входы .сумматора 3 поступает код 1,1... 11 2. В сумматоре 3 фор- мируется разность X, 2 + Х 2 - - 2. По завершении операции .суммирования подается сигнал С1. Если эта разность положительна, в младший разряд регистра 1 записывается код 1, в регистр 2 записывается эта же разность. Если разность отрицательна, в регистр 1 записывается О, сигнал С1 через элемент И не проходит и содержимое регистра

2не изменяется (запись отсутствую ет). По завершении записи на вход 9 подается сигнал С2. Одновременно на входы 10 и 11 подается вторая пара разрядов подкоренного числа X. В регистре 2 происходит сдвиг

L 2, в младшие разряды регистра 2 записывается вторая пара разрядов X. Первый цикл закончен. Аналогичным образом вьтолняются еще п-1 циклов. Результат считывается из р гисп-ра 1.

5

0

5

0

5

40

Формула изобретения

Устройство для извлечения квадратного корня, содержащее два регистра, сумматор и элемент НЕ, причем вход управления сдвигом первого регистра соединен с первым управляющим входом устройства, единичные разрядные выходы первого регистра являются выходами результата устройства, я инверсные вькоды разрядов с первого по (п-1)-й (где п-разряд- ность входного кода) первого регистра соединены с первыми входами разрядов с третьего по (п+1)-й сумматора соответственно, первые входы первого, второго и знакового разрядов суш1атора подключены к входу логической единицы устройства, вход логического нуля которого соединен с вторым входом знакового разряда сумматора, выход которого соединен с входом элемента НЕ, выход которого подключен к управляющему входу первого регистра, о т л и ч а ю щ е- е с я тем, что, с целью упрощения, оно содержит элемент И, первый и второй входы которого соединены с t( первым управляющим входом устройства и выходом элемента НЕ соответственно, а выход - с входом разрешения записи второго регистра, вход управления сдвигом которого подключен к : второму управляющему входу устройства, входы и выходы разрядов с первого по (п+1)-й второго регистра соединены с выходами и. вторыми входами одноименных разрядов сумматора соответственно, вторые входы первого и второго разрядов второго регистра соединены с первым и вторым информационными входами устройства.

Авторы

Даты

1989-01-15—Публикация

1987-06-29—Подача