18

со

00

N-4

со

N

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Устройство для вычисления корня третьей степени | 1985 |

|

SU1288695A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1273921A1 |

| Арифметическое устройство | 1978 |

|

SU809169A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

Изобретение относится к цифровой вычислительной технике и может быть применено в цифровых вычислительных машинах и при построении специализированных вычислительных устройств. Цель изобретения - повышение быстродействия при одновременном расширении класса решаемых задач за счет возможности обработки чисел в форме с плавающей запятой. Устройство содержит регистр 3 показателя степени, регистр 4 основания, шифраторы 5, 6 адреса, блоки 7-9 памяти, умножители 10, 11, коммутатор 12, сумматоры 13,14 блок 15 выравнивания порядков, блок 16 управления, регистр 17 результата. Вычисление корня п-й степени в устройстве производится путем вычисления полинома при заранее вычисленных и хранимых в памяти коэффициентов. (П

(puff.l

Изобретение относится к цифровой вычислительной технике и может быть применено в цифровых вычислительных машинах и при построении специализированных вычислительных устройств.

Цель изобретения - повышение быстродействия устройства при одновременном расширении класса решаемых задач за счет обработки чисел в форме с плавающей запятой.

Вычисление корня п-й степени в предлагаемом устройстве производится

путем вычисления полинома

при заранее вычисленных и в памяти коэффициентах

y-f(xii) (i)

vfe-;.

При представлении аргумента ме с фиксированной запятой или вакицей запятой и апроксимации

f(x)

полином первой степени, с точностью не хуже 10 , вычисляется соответственно по следующим алгоритмам:

47 А;Х;- В; для чисел с фиксированной запятой

Ч- ( (пРц /. LPx

х (А; т +В;Н2

для чисел с плавающей запятой, где А; и В; - коэффициенты для данной степени корня и

подкоренного выражения;

2 ш.

- мантисса подкоренного выражения; X - подкоренное выражение; РХ - порядок подкоренного

выражения;

п - показатель степени кор- Н, где i О,1,2...12 Значения , также как и коэф- фициенты А; и Bj вычисляются заранее и хранятся в памяти.

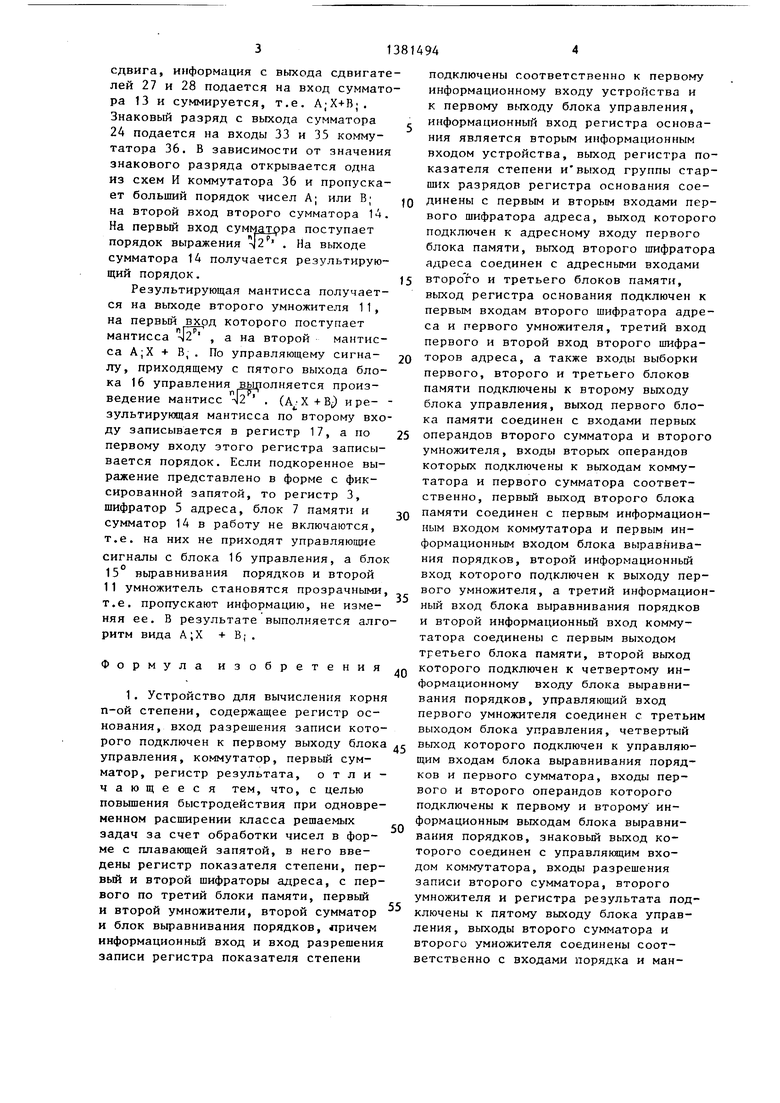

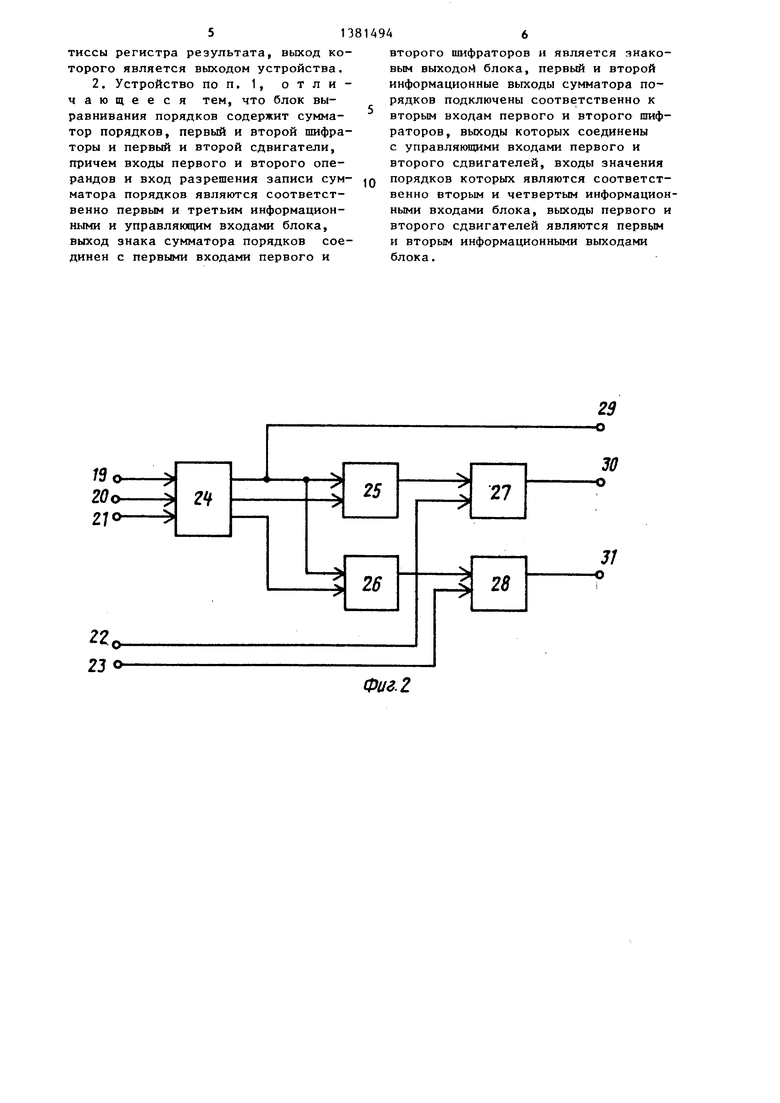

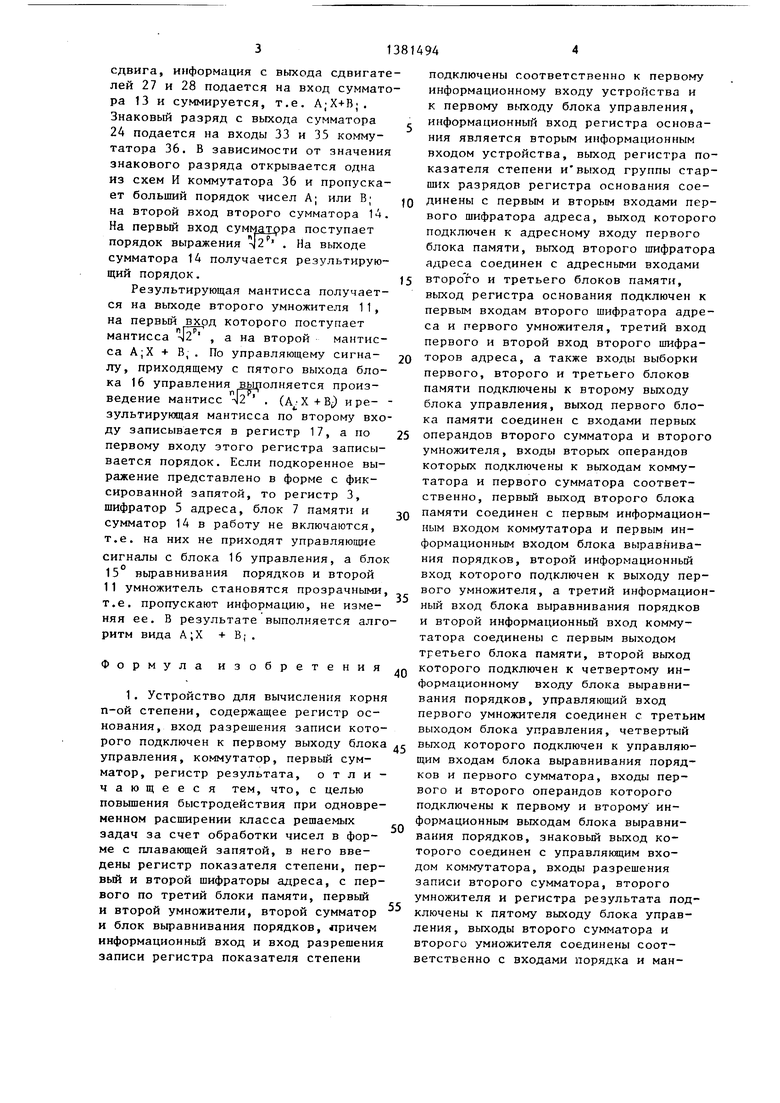

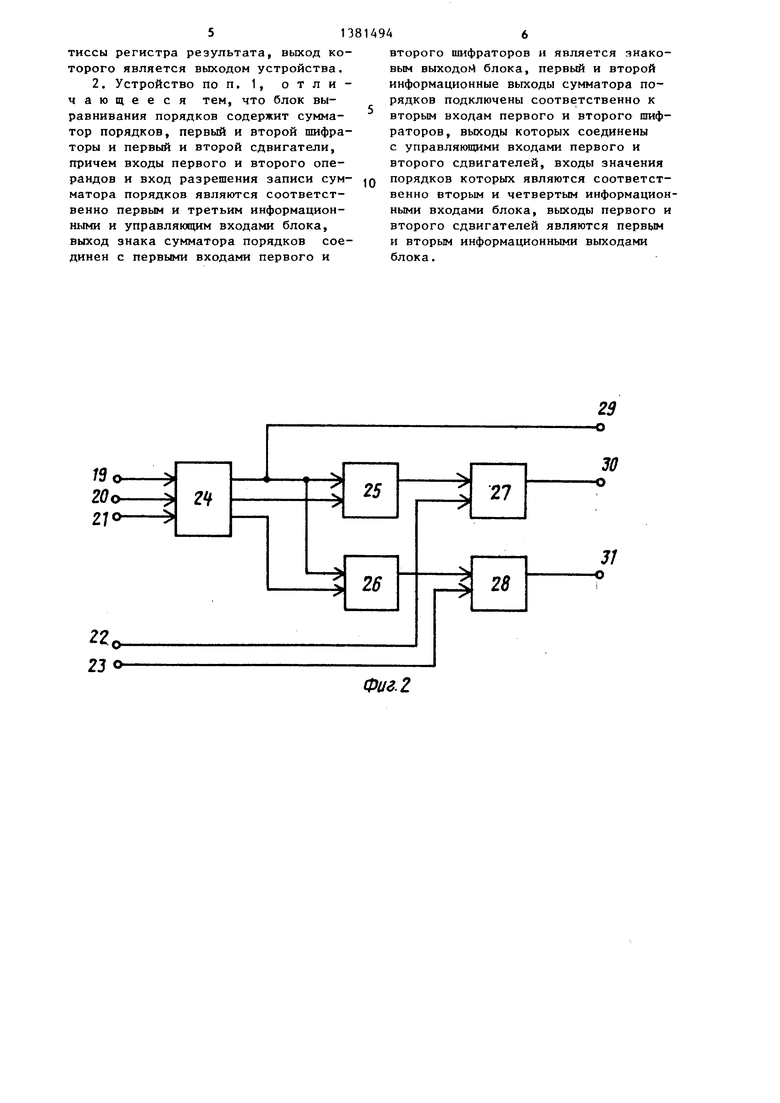

На фиг. 1 изображена структурная схема устройства для вычисления корня п-й степени; на фиг. 2 - схема блока выравнивания порядков; на фиг. 3 и 4 - варианты схем реализации коммутатора и сднигателя соответственно.

Q

5

0

5

0

5

0

5

0

5

Устройство для выключения корня п-й степени содержит первый 1 и второй 2 информационные входы, регистр 3 показателя степени, регистр 4 основания, шифраторы 5 и 6 адреса, блоки 7-9 памяти, умножители 10 и 11, коммутатор 12, сумматоры 13 и 14, блок 15 выравнивания порядков, блок 16 управления, регистр 17 результата, выход 18 результата, входы 19-23 блока выравнивания порядков, сумматор 24, шифраторы 25 и 26, сдвига- тели 27 и 28, выходы 29-31 блока выравнивания порядков, входы 32-35 коммутатора 36 с выходом 37 и входы 38-44 сдвигателей 45 с выходом 46.

Устройство для вычисления корня п-й степени работает следующим образом.

По входу 1 поступает показатель степени корня, а по входу 2 - основание в двоичном коде. В зависимости от содержимого степени корня и подкоренного выражения и при приходе управляющего сигнала со второго выхода блока управления первый шифратор 5 формирует адрес и с первого блока 7 памяти по адресу выбирается информация . По содержимому регистра 4 второй шифратор 6 одновременно с первым шифратором 5 формирует

адрес и со второго 8 и третьего 9 блоков памяти по этому адресу выбирается информация коэффициентов А и В. На первом умножителе 10 по сигналу с третьего выхода блока 16 управления второго блока 8 памяти производится умножение А Х. Затем с выхода первого умножителя 10 и третьего блока 9 памяти поступают числа на блок 15 выравнивания порядков и по сигналу с четвертого выхода блока 16 управления начинается выравнивание порядков. Если числя, представлены в форме с плавающей запятой, то порядки чисел вычитаются на сумматоре 24, т.е. из порядка коэффициента А вычитается порядок коэффициента В. В зависимости от знака разности порядков и полученного частного шифратора 25 и 26 определяют код сдвига, который подается соответственно на сдвигатели 27 и 28. На информационные входы сдвигателей подаются числовые значения мантисс. Сдвигается та мантисса, порядок которой меньше. После сдвига мантиссы с меньшим порядком и передачи мантиссы с большим порядкам без

сдвига, информация с выхода сдвигате лей 27 и 28 подается на вход сумматора 13 и суммируется, т.е. А;Х+В;. Знаковый разряд с выхода сумматора 24 подается на входы 33 и 35 коммутатора 36. В зависимости от значения знакового разряда открывается одна из схем И коммутатора 36 и пропускает больший порядок чисел А; или В; на второй вход второго сумматора 14. На первый вход сумматора поступает порядок выражения 2 . На выходе сумматора 14 получается результирующий порядок.

Результирующая мантисса получается на выходе второго умножителя 11, на первый вход которого поступает мантисса 2 , а на второй мантисса А;Х + В,. По управляющему сигна- лу, приходящему с пятого выхода блока 16 управления выполняется произП Г р

ведение мантисс . (A/X-t-B,) и ре- - зультирующая мантисса по второму входу записывается в регистр 17, а по первому входу этого регистра записывается порядок. Если подкоренное выражение представлено в форме с фиксированной запятой, то регистр 3, шифратор 5 адреса, блок 7 памяти и сумматор 14 в работу не включаются, т.е. на них не приходят управляющие сигналы с блока 16 управления, а блок 15° вьфавнивания порядков и второй 11 умножитель становятся прозрачными, т.е. пропускают информацию, не изменяя ее. В результате выполняется алгоритм вида А;Х -i- Bj .

Формула изобретения

JQ J5

20

25on 35

40

дс

50

5

подключены соответственно к первому информационному входу устройства и к первому выходу блока управления, информационньп1 вход регистра основания является вторым информационным входом устройства, выход регистра показателя степени и выход группы старших разрядов регистра основания соединены с первым и вторым входами первого шифратора адреса, выход которого подключен к адресному входу первого блока памяти, выход второго шифратора адреса соединен с адресными входами второ го и третьего блоков памяти, выход регистра основания подключен к первым входам второго шифратора адреса и первого умножителя, третий вход первого и второй вход второго шифраторов адреса, а также входы выборки первого, второго и третьего блоков памяти подключены к второму выходу блока управления, выход первого блока памяти соединен с входами первых операндов второго сумматора и второго умножителя, входы вторых операндов которых подключены к выходам коммутатора и первого сумматора соответственно, первый выход второго блока памяти соединен с первым информационным входом коммутатора и первым информационным входом блока выравнивания порядков, второй информационный вход которого подключен к выходу первого умножителя, а третий информационный вход блока выравнивания порядков и второй информационный вход коммутатора соединены с первым выходом третьего блока памяти, второй выход которого подключен к четвертому информационному входу блока выравнивания порядков, управляющий вход первого умножителя соединен с третьим выходом блока управления, четвертый выход которого подключен к управляющим входам блока выравнивания порядков и первого сумматора, входы первого и второго операндов которого подключены к первому и второму информационным выходам блока выравнивания порядков, знаковый выход которого соединен с управляющим входом коммутатора, входы разрешения записи второго сумматора, второго умножителя и регистра результата подключены к пятому выходу блока управления, выходы второго сумматора и второго умножителя соединены соответственно с входами порядка и мантиссы регистра результата, выход которого является выходом устройства.

второго шифраторов и является знаковым выходом блока, первьй и второй информационные выходы сумматора порядков подключены соответственно к вторым входам первого и второго шифраторов, выходы которых соединены с управляющими входами первого и второго сдвигателей, входы значения порядков которых являются соответственно вторым и четвертым информационными входами блока, выходы первого и второго сдвигателей являются первь1м и вторым информационными выходами блока.

Фиг. 2

Фиг.З

ФигМ

| Устройство для вычисления многочленов вида @ @ | 1978 |

|

SU868767A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для извлечения корня п-й степени | 1979 |

|

SU883898A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-04-30—Подача