Изобретение относится к вычислительной технике, а именнр к устройствам, имитирующим сбои и отказы аппаратурньгх средств вычислительной ; системы.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения возможности изменения длительности сбоя и синхронизации генерации сбоя с внешними сигналами, поступающими от элементов контролируемой аппаратуры.

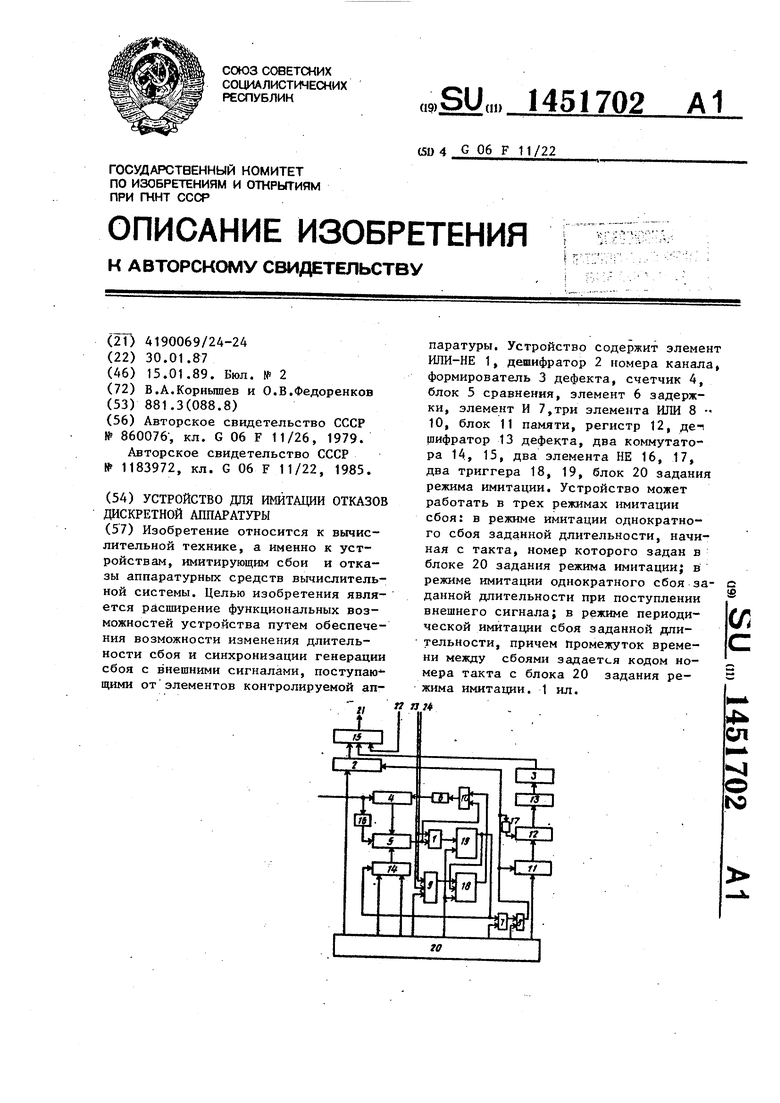

Схема устройства изображена на чертеже .

Устройство содержит элемент ИЛИ- НЕ 1, дешифратор 2 номера канала, формирователь 3 дефекта, счетчик А, блок 5 сравнения, элемент 6 задержки, элемент И 7, три элемента ИЛИ 8-10, блок 11 памяти, регистр 12, дешифратор 13 дефекта, два коммутатора 14 и 15., два элемента НЕ 16, 17 два триггера 18 и 19, блок-20 задания режима имитации, группу 21 ин- формационных выходов устройства, группу 22 информационных входов устройства, два входа 23 и 24 запуска устройства.

Устройство работает следующим об- разом.

Потребитель подключает информационные входы и выходы устройства к соответствующим выходам и входам дискретной аппаратуры, в которую не- обходимо внести дефект, а тактовый вход устройства соединяет с синхронизирующим выходом.указанной дискретной аппаратуры.

Перед пуском контролируемой ап- паратуры с блока 20 задания режима имитации задается номер канала, в ко TqpoM необходимб имитировать дефект, режим имитации (отказ или сбой), адрес,, ячейки блока 11 памяти, в которой хранится в соответствующем масштабе тестовое воздействие, номер цикла работы аппаратуры, начиная С которого необходимо имитировать дефект, и код длительности сбоя. Перечисленные гфизнаки хранятся в блоке 20 задания режимов имитации в течение всего включения контролируемой аппаратуры.

Устройство может работать в трех режимах имитации сбоя: режим имитации однократного сбоя заданной длительности, начиная с такта, номер которого задан в блоке 20 задания

режима имитации; режим имитации однократного сбоя заданной длительности при поступлении внешнего сигнала; режим периодической имитации сбоя заданной длительности, причем промежуток времени между сбоями задается кодом номера такта с блока 20 задания режима имитации.

Ппред работой в каждом из режимов с помощью сигнала начальной установки, поступающего с блока 20, осуществляется начальная установка устройства, причем счетньй триггер 19 устанавливается в нулевое состояние, а триггер 18 - в единичное состояние. При этом с прямого выхода триггера 18 на первый вход элемен- .та ИЛИ 10 поступает единичный уровень, на второй вход - сигнал нулевого уровня с выхода блока 5 сравнения. С выхода элемента ИЛИ 10 сигнал через линию задержки устанавли- вает счетчик 4 в нулевое состояние, запрещая отсчет циклов. Сигнал отсутствия сбоя с выхода триггера 19 поступает на управляющий вход коммутатора 14, при этом через коммутатор 14 на вторую группу входов блока 5 сравнения йоступает код но- мера такта с выходов блока 20 за- . Дания режима имитации.

Для задания первого режима необходимо с блока 20 задать значение сигнала режима однократного сбоя, равное О с, Вход 23 запуска устройства подключается к выходу элемента контролируемой аппаратуры, по сигналу с которого начинается отсчет тактов до момента начала имитации сбоя. Вход 24 не используется (сигнал 24 равен нулю),

Сигнал запуска можно выдавать до пуска контролируемой аппаратуры вруч- вручную с блока 20 .(сигнал режима однократного сбоя), при этом вход 23 устройства не используется.

. Сигнал,поступающий на вход 23 устройства, проходит на вход элемента ИЛИ 9. Сигнал, формируемый на выходе элемента ИЛИ 9, поступает на вход установки в ноль счетного триггера 18, в результате чего сигнал нулевого уровня поступает на первый вход элеме:нта ИЛИ 10, на второй вход которого поступает сигнал с выхода блока 5 сравнения. С выхода элемента ШШ 10 сигнал поступает на вход обнуления счетчика 4 и разрешает

отсчет циклов. Так как на счетньвЧ вход счетчика 4 поступают тактовые импульсы, по мере их поступления ег содержимое увеличивается на единицу Через элемент НЕ 16 эти же импульсы опрашивают блок 5 сравнения. При равнозначности информации,,поступающей на первые и вторые группы информационных входов блока 5 сравнения, последний вырабатывает сигнал, который поступает на .вход эле ме нта ИЛИ-НЕ, на вькоде которого вырабатывается сигнал, устанавливаю пщй счетный триггер 19 в состояние 1 (триггеры 18 и 19 взяты с инверсными динамическими входами).

С выхода триггера 19 сигнал наличия сбоя поступает на управляющий вход коммутатора 14, в резуль,.. чего на вторую группу входов схемы сравнения поступает код длительности сбоя с группы выходов блока 20. Сигнал с выхода триггера 19 поступает также на первый вход элемента И 7, второй вход которого соединен с выходом режима сбоя блока 20 задания режима имитации. Сигнал, формируемый на выходе элемента И 7, поступает на первый вход элемента ИЛИ 8, на втсррой вход которого поступает сигнал о наличии режима имитации отказа с блока 20 задания режима имитации. Сигнал, формируемый на выходе элемента ИЛИ 8, поступает на вход стробирования блока 11 памяти и на вход стробирования дешифратора номера канала и через элемент НЕ 17 - на вход обнуления, регистра 12, разрешая запись в него. Дешифратор номера канала в соответствии с кодом, поступающим на его входы с группы выходов нсче.)а канала блока 20 задания режима имитации, осуществляет выбор канала коммутатора 15, в который должен быть внесён сбой. Считанное с блока 11 памяти тестовое воздействие через регистр 12 вьщается на дешифратор 13 дефекта..

Посредством сигнала, возбуждаемого на одном из выходов дешифратора .13 дефекта, являющихся входами формирователя 3 дефекта, на выходе формирователя 3 дефекта формируется заказанный дефект, который поступает на группу информационных входов коммутатора 15 и далее на заказанный выход устройства.

Сигнал с выхода блока 5 сравнения поступает также на первый вход элемента ИЛИ 10. Импульс, формируемый g на выходе элемента ИЛИ 10, поступает на вход установки счетчика 4, в результате чего счетчик обнуляется. При поступлении очередного тактового импульса счетчик начинает от 10 счет длительности сбоя. При равнозначности информации, поступающей на первые и вторые входы блока срав- нения, последний вырабатьшает сигнал, который переключает счетный 15 триггер 19 в состояние О. Поступление сбоя в заказанный канал прекращается.

В момент, переключения триггера 19 сигнал, поступающий с прямого 20 выхода триггера 19 на счетный вход триггера 18, переключает триггер 18. Сигнал с прямого выхода тригге ра 18 через элемент ИЛИ 10 поступает в качестве сигнала обнуления 25 счетчика, блокируя его работу. Схема устанавливается в исходное состояние. При поступлении очередного сигнала на вход 23 цикл работы устройства повторяется.

30 Для работы во втором режиме 2 необходимо задать с блока 20 значение сигнала режима однократного сбоя, равное логическому нулю. Код номера такта, задаваемый с блока 20 задания ,jg режима имитации, должен быть отличен от н5гля. Вход 24 устройства подключается к выходу элемента аппаратуры,, по сигналу с которого необходимо имитировать сбой заданной дли- 0 тельности. ,

При Поступлении внешнего сигнала на в Ход запуска устройства на вы- ходе элемента ИЛИ-НЕ формируется сиг5 который поступает на счетный вход триггера 19 и переключает его в единичное состояние. Сигнал запуска поступает также на вход элемента ИЛИ

. 9 выходе которого формируется

Q сигнйл, который устанавливает триггер 18 в состояние О, при этом разрешается работа счетчика 4. По сигналу с выхода триггера 19 коммутатор 14 осуществляет коммутацию ко5 Д длительности сбоя на вторую группу информационных входов блока 5 сравнения. Далее устройство работает так же, как и в первом режиме. После вьщачи в аппаратуру сбоя заданной длительности схема возвращается в исходное состояние.

В третьем режиме значение сигнала режима однократного сбоя равно 1. В этом случае счетчик после окончания цикла работы устройства не обнуляется, так как триггер 18 находится в состоянии О.

Функционирование устройства в каждом цикле работы происходит аналогично функционированию в первом режиме, за исключением того, что внешних сигналов для начала цикла работы устройства не требуется. Устройство в этом случае формирует последовательндсть сбоев заданной длительности, причем,промежуток времени (количество тактов) между соседними сбоями равно коду номера такта, задаваемому с блока 20 задания режима имитации.

Формула изобретени

Устройство для имитации отказов дискретной аппаратуры, содержащее блок задания режимов имитации, блок сравнения, первый коммутатор, дешифратор номера канала, счетчик, первый элемент НЕ, элемент задержки, блок памяти, регистр,дешифратор дефекта, формирователь дефекта,элемент И и первый элемент ИЛИ, причем вьгходы первого коммутатора образуют группу информационных выходов усройства, группа информационных входов устройства соединена с первой группой информационных входой первого коммутатора, вторая группа ин- форма ционных входов которого соеди- нена с группой выходов формирователя дефекта, группа выходов задания номера дефекта блока задания режима имитации соединена с группой адресных входов блока памяти, группа выходов которого соединена с группой информационных входов регистра, группа выходов которого соединена с группой входов дешифратора дефек- та, выходы тсоторого соединены с входами формирователя дефекта,группа выходов задания номера канала блока задания режима имитации соединена с группой входов дешифратора номера канала, выходы которого соединены с управляющими входами первого коммутатора, выход задания режима сбоя и выход задания режима

0

5

0

отказа блока задания режима имитации соединены с первыми входами соответственно элемента И и первого элемента ИЛИ, выход элемента И соединен с вторым входом первого элемента ИЛИ,выход которого соединен со стробирующими входами блока памяти и номера канала, тактовый вход устройства соединен с входом синхронизации счетчика и с входом первого элемента НЕ, выход первого элемента НЕ соединен с входом разрешения сравнения блока сравнения, первая группа информационных входов которого соединена с группой разрядных выходов счетчика, отличающееся тем, что, с целью расширения его функциональных возможностей за счет изменения длительности сбоя и управления инерцией сбоя по внешним сигналам, в него введены, второй коммутатор, элемент ИЛИ-НЕ, два триггера, второй и третий эле- 5 менты ИЛИ, второй элемент НЕ, причем группа выходов задания номера цикла блока задания режима имитации соединена с первой группой информационных входов второго коммутатора, вторая группа информационных входов которого соединена с группой выходов задания длительности сбоя блока задания режима имитации, выход начальной установки которого соединен с входом установки в 1 первого триггера и с входом установки в 1 второго триггера, выход задания режима однократного сбоя блока за- Дания режима имитации соединен с первым входом второго элемента ИЛИ, второй вход которого является первым входом запуска устройства, выход второго элемента ИЛИ соединен с входом установки в О первого триггера, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом элемента задержки, вькод кото-- рого соединен с входом установки в О счетчика, выход сравнения блока сравнения соединен с первым входом элемента ИЛИ-НЕ и вторым входом третьего элемента ИЛИ,, второй вход элемента ИЛИ-НЕ объединен с третьим входом второго элемента ИЛИ и подключен к второму входу запуска устройства, выход элемента ИЛИ-НЕ соединен со счетным входом второго триггера, выход которого соединен

0

5

0

5

0

5

114517028

со счетным входом первого триггера, уходов блока сравнения, выход перво- с вторым входом элемента И и с уп- го элемента ИЛИ соединен с входом равляющим входом второго коммутато- второго элемента НЕ, выход которо- ра, группа выходов которого соеди- fo соединен с входом обнуления нен с второй группой информационных регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации отказов дискретной аппаратуры | 1990 |

|

SU1815642A1 |

| Устройство для имитации отказов дискретной аппаратуры | 1984 |

|

SU1183972A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Логический анализатор | 1985 |

|

SU1357958A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| Устройство для контроля интегральных схем | 1983 |

|

SU1182520A1 |

Изобретение относится к вычислительной технике, а именно к устройствам, имитирующим сбои и отказы аппаратурных средств вычислительной системы. Целью изобретения является расширение функциональных возможностей устройства путем обеспечения возможности изменения длительности сбоя и синхронизации генерации сбоя с внешними сигналами, поступаю- щими от элементов контролируемой аппаратуры. Устройство содержит элемент ИПИ-НЕ 1, дешифратор 2 номера канала, формирователь 3 дефекта, счетчик 4, блок 5 сравнения, элемент 6 задержки, элемент И 7,три элемента ИЛИ 8 - 10, блок 11 памяти, регистр 12, де-i шифратор 13 дефекта, два коммутатора 14, 15, два элемента НЕ 16, 17, два триггера 18, 19, блок 20 задания режима имитации. Устройство может работать в трех режимах 1шитации сбоя: в режиме имитации однократного сбоя заданной длительности, начиная с такта, номер которого задан в блоке 20 задания режима имитации; в режиме имитации однократного сбоя заданной длительности при поступлении внешнего сигнала; в режиме периодической имитации сбоя заданной длительности, причем Промежуток времени между сбоями задается кодом номера такта с блока 20 задания режима имитации. 1 ил. П Я сл 4 СП | о tc

| Устройство для отладки тестов | 1979 |

|

SU860076A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для имитации отказов дискретной аппаратуры | 1984 |

|

SU1183972A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1987-01-30—Подача