:л

зе

Изобретение относится к импульс- ной технике и может быть иг.пользо- вано в устройствах вычислительной техники и автоматики.

Целью изобретения является повышение быстродействия инвертора и снижение потребляемой им мощности.

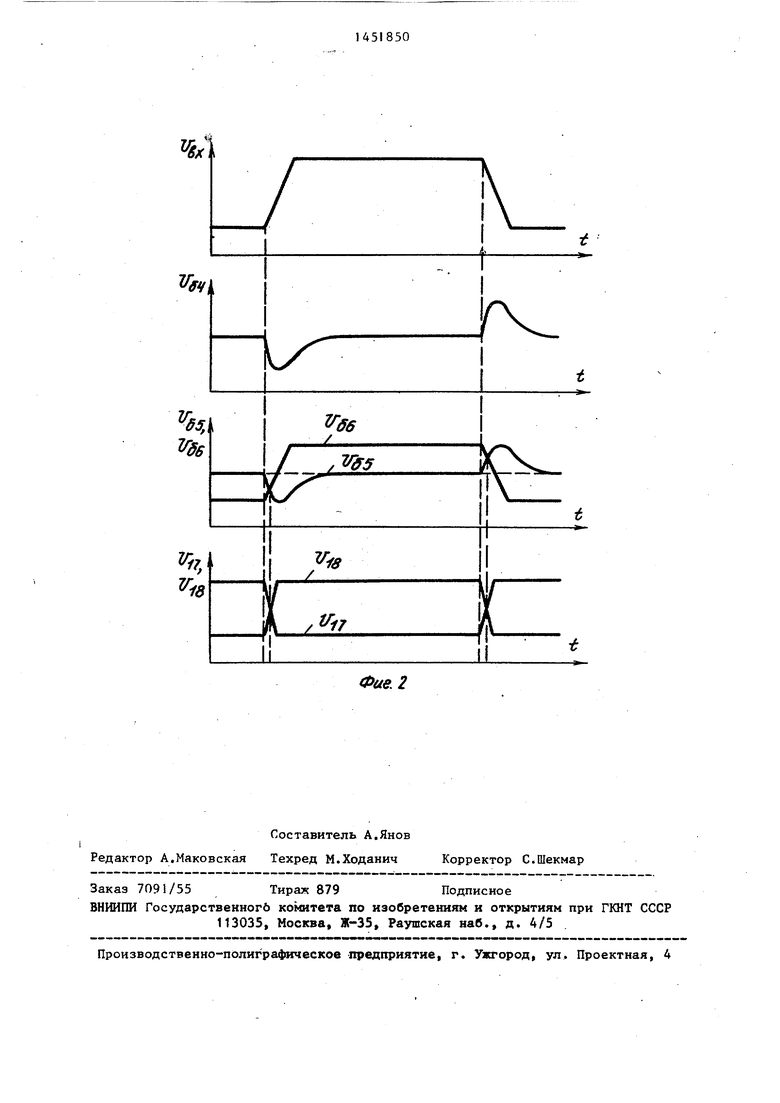

На фиг,1 приведена принципиальная электрическая схема инвертора; на фиг,2 - графики, поясняющие его работу.

Инвертор содержит- первый транзи с- Тор 1, база которого является входом 2 инвертора, коллектор первого транзистора 1 соединен с первым выводом первого резистора 3 и базой седьмого транзистора 4J эмиттеры второго 5 и третьего 6 транзисторов соединены с коллектором четвертого транзистора 1 эмиттер первого транзистора 1 соединен с базой второго 5 и коллектором шестого 8 транзисторов и первым выводом первого конденсатора 9 база третьего транзистора 6 соединена с эмиттером седьмого 4 и колекторрм пятого 10 транзисторов и первым выводом второго конденсатора 11; база четвертого транзистора 7 соединена с первой шиной 12 опорного напряжения, а второй вывод первого резистора 3 - со второй шиной 13 опорного напряжения, э.миттер четвертого транзистора 7 соединен с первым выводом второго резистора 14, коллекторы второго 5 и третьего 6 транзисторов соединены с первыми выводами третьего 15 и четвертого 16 резисторов и является инвертирующим 17 и неинвертирующим 18 выходами устройства, вторые выводы третьего 15 и четвертого 16 резисторов и коллектор седьмого транзистора 4 соединены с общей шиной. 19, база -шестого транзистора В соединена с первым выводом седьмого резистора 20 и вторым выводом второго конденсатора П , база пятого транзистора 10 соединена с первым выводом восьмого резистора,

21и вторым выводом первого конденсатора 95 второй вывод восьмого резистора 21 соединен с третьей шиной

22опорного напряжения, второй вывод седьмого резистора 20 соединен с пер: вой пганы 12 опорного напряжения, эмиттер шестого транзистора 8 .соединен с первым выводом седьмого резистора 23, а эмиттер пятого транзистора 10 - с первым выводом пятого ре

зистора 24I вторые выводы второго 14, пятого .3 и шестого 7.4 резисторов соединены с шиной 25 питания.

Инвертор работает следующим образом,

Для обеспечения работы инвертора к нему подключеньт шина 19 питания и три шины опорного напряжения 02, 13, 22), при этом в коллекторе транзистора 7 протекает ток, достаточный для быстрого переключения эмиттерно- связанной пары (второй 5 и третий 6 транзисторы, третий 15 и четвертый 16 резисторы), В коллекторе транзистора 8 протекает , близкий к току коллектора транзистора 7, и обеспечивает падение потенциала на первом резисторе 3 (ди/2, где ill г перепад входного логического сигнала), В коллекторе транзис.тора 10 протекает достаточно малый ток (в десятки раз меньше тока коллектора транзистора 7), необходимый для привязки поте н- циала базы транзистора 6 в соответствии с потенциалом баз транзисторов 1. 4,

Условимся, что в. исходном состоянии на входе 2 поддерживается низкий потенциал. При этом на базе третьего транзистора 6 установится потенциал

5

0

5

0

5

и.

К,

Кб (1)

Ч

Oj- 02

И на базе второго транзистора - потенциал

Д 8г s, - v,(2)

где Ер - величина напряжения .на

второй шине 13 опорного напряжения ; Т. - ток коллектора шестого

транзистора 8;

fi - коэффициент передачи базового тока в схеме с общим эмиттером;

величина первого резистора 3;

,падение потенциала на прямосмещенном р-п-пере- ходе база -эмиттер транзистора;

величина низкого уровня входного потенциала на базе первого транзистора 1 ,

Величина напряжения на второй шине 13 опорного напряжения, ток коллектора транзистора 8 и в.еличина первого резистора 3 выбираются такими, чтобы потенциал базы второго транзистора

v

IT

5 был меньше потенциала базы третьего транзистора 6 приблизительно на ди/2. Из распределения потенциалов на базах второго 5 и третьего 6 тразисторов можно заключить, что ток коллектора четвертого транзистора 7 замкнется на третий транзистор 6 и, соответственно, на неинвертирующем выходе 18 установится низкий потенциал, а на инвертирующем 17 - высокий.

Повышение потенциала на входе 2 инвертора приводит к переключению устройства, что происходит следумци образом.

Быстрое нарастание входного сигнала (передний фронт импульса)приводит к появлению емкостного тока

с.

г У

4t

(3)

первого конденсатора 9, который, замыкаясь в коллектор первого транзистора 1, вызывает быстрое падение потенциала на первом резисторе 3 и, соответственно, снижение потенциала базы седьмого транзистора 4

MlR, I + T..R, (4)

Кроме этого емкостный ток первого конденсатора 9 распределяется мезкду восьмым резистором 21 и базой пятого транзистора 10:

1.

(5)

соотношения следует.

что

т..

Кс

(1

е Ig , 1к5

,

(6)

Чб

токи базы и коллектора пятого транзистора соответственно; ток, ответвляющийся через восьмой -. резистор.

Из соотношения 6 идно, что в цепи коллектора развивается значительный ток (IK I f. ), который

весьма быстро разряжает второй рабочий конденсатор I1 и паразитные емкости этого узла и соответственно понижает потенциал базы третьего транзистора 6, Таким образом, по фронту входного сигнала происходит противофазное изменение потенциалов баз второго 5 и третьего 6 транзисторов что приводит к быстрому выравниванию потенциалов баз этих транзисторов и переключению инвертора, т.е. на инвер- щ ующем выходе (17) ус -ановится низкии потенциал, на неинвертирующем (181 высокий. По мере достижения входным сигналом верхней амплитуды прекря1 (ается действие емкостного тока, повышаются потенциалы баз седьмого 4 и третьего 6.транзисторов к своей исходной величине.

При быстрой смене входного сигнала

10 с. высокого уровня на низкий (задний фронт первый транзистор 1 запирается, ток коолектора транзистора 8 направлен на разряд первого конденсатора 9 и паразитных емкостей этого

15 узла. При таком распределении сигналов fbv. коллектора первого транзистора 1 устремляется к нулю, соответственно начинается быстрое падение потенциала на первом резисторе 3, по- 0 вьичение потенциалов базы и эмиттера транзистора 4, что приводит к появлению емкостного тока второго конденсатора 11. Этот ток, распределяясь между базой транзистора 8 и резисто5 ром 20, приводит к дополнительном увеличению тока коллектора транзистора и, соответственно, к более быстрому снижению потенциала базы второго транзистора 5. Подробное распре0 деление токов и потенциалов приводит к достаточно быстрому установлению равенства потенциалов баз второго 5 и третьего 6 транзисторов.и, соответственно, к переключению инвертора. На инвертируюв1ем выходе установится

5

высокий потенциал, ругацем - низкий.

а на неинверти40

45

50

55

Формула изобретения

Инвертор, содержаг(ий восемь резисторов, база первого транзистора соединена с входом инвертора, коллектор с первым выводом первого резистора, а эммитер - с первым выводом конденсатора и базой второго транзистора эмиттер которого соединен с эмиттером третьего транзистора и коллектором четвертого транзистора, база которого соединена с первой шиной опорного напряжения, а эмиттер через второй резистор - с шиной питания, коллекторы второго и третьего транзисторов соединены соответственно с инвертирующим и неинвертирующим выходами и с первыми выводйми соответственно третьего и четвертого резисторов, база третьего транзистора соединена с коллектором пятого

транзистора, эмиттер которого пятый резистор соединен с шиной питания и первым выводом шестого резистора, отличающийся тем, что, с целью повышения быстродействия., и снижения потребляемой мощности, введены второй конденсатор, шестой и седьмой транзисторы, второй вывод первого резистора соединен с.второй шиной опорного напряжения, эмиттер первого транзистора - с коллектором шестого транзистора, эмиттер которого соединен с вторым выводом шестого резистора, база

соответственно через седьмой резистор и второй конденсатор соединена с базами четвертого и третьего транзисторов, второй вывод первого конденсатора соединен с базой пятого транзистора и через восьмой резистор подключен к третьей шине опорного напряжения, коллектор первого

транзистора соединен с базой седьмого транзистора, коллектор которого подключен к вторым выводам третьего и чётвертог о резисторов и общей шине, а эмиттер . соединен с базой третьего транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРОСТАТИЧЕСКИХ ПОТЕНЦИАЛОВ | 1993 |

|

RU2083990C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ НАПРЯЖЕНИЯ | 1990 |

|

RU2022274C1 |

| Транзисторный ключ с защитой от перегрузки | 1986 |

|

SU1348993A1 |

| Логический элемент | 1988 |

|

SU1554136A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| Устройство задержки | 1989 |

|

SU1793535A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Устройство формирования импульсов | 1986 |

|

SU1347170A1 |

| Генератор импульсов | 1984 |

|

SU1195425A1 |

| Непрерывно-ключевой стабилизатор тока | 1985 |

|

SU1348800A1 |

Изобретение относится к импульс ной технике и предназначено для ис- пользования в устройствах вычислительной техники и автоматики. Цель изобретения - повышение быстродействия инвертора и снижение потребляемой мощности. Инвертор содержит восемь резисторов, семь транзисторов и два конденсатора. Введение второго конденсатора, шестого и седьмого транзисторов позволяет увеличить динамический базовый ток транзисторов источников тока во время нарастания и спада входного сигнала. Это приводит к увеличению крутизны фронтов выходных сигналов, при этом увеличивается быстродействие., статическая потребляемая мощность не изменяется. 2 Ш1. i (Л

25

Фиа.1

A

Фие.2

| Miyonoga Н | |||

| et al | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Miyanaga H | |||

| et al | |||

| A 0,85 ns 1 Kb Bipolar ECL RAM Extended, Abstracts of the 16 (1984) International Conference on Solid State Devices and Materials | |||

| Kobe, 1984, p.226, fig.3. | |||

Авторы

Даты

1989-01-15—Публикация

1987-06-10—Подача