Множительно-делительное устройство 2Q резистора 10. База логарифмирующего

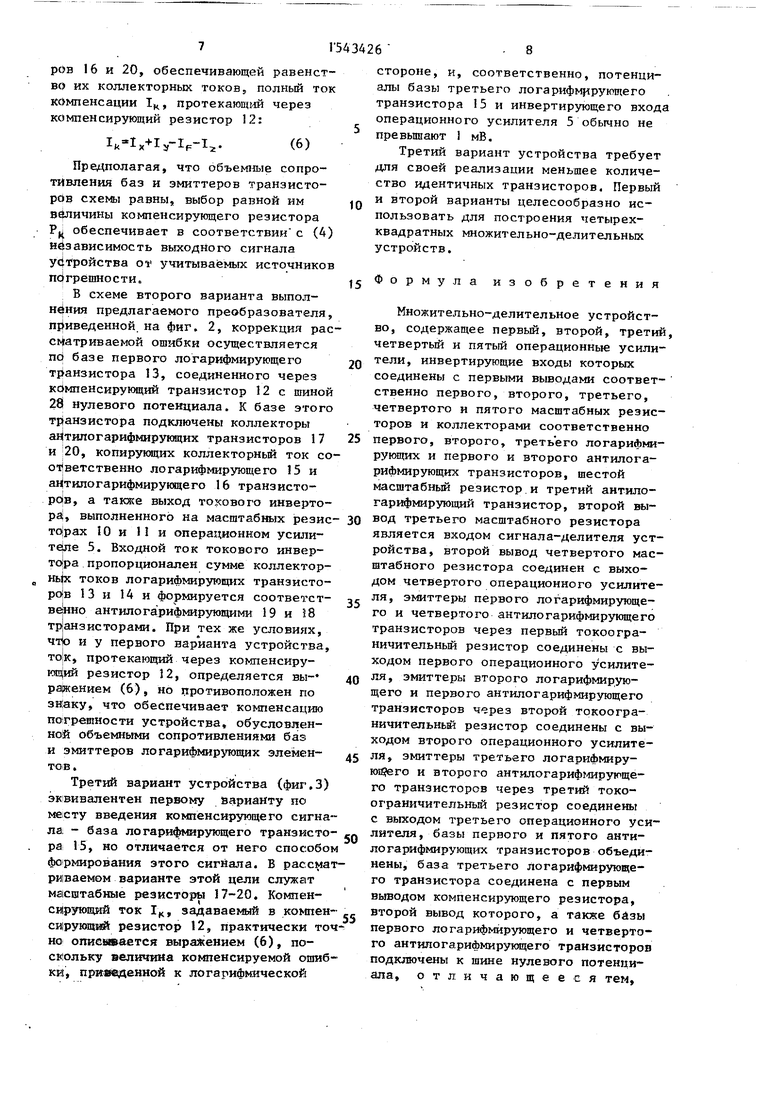

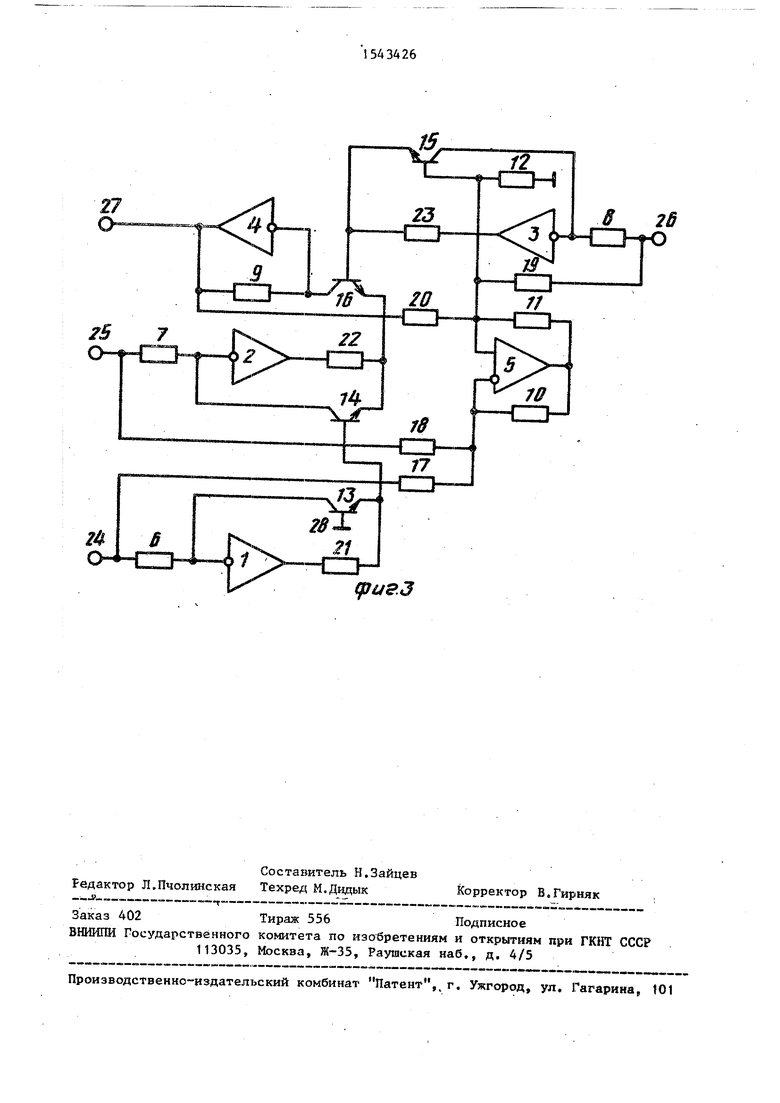

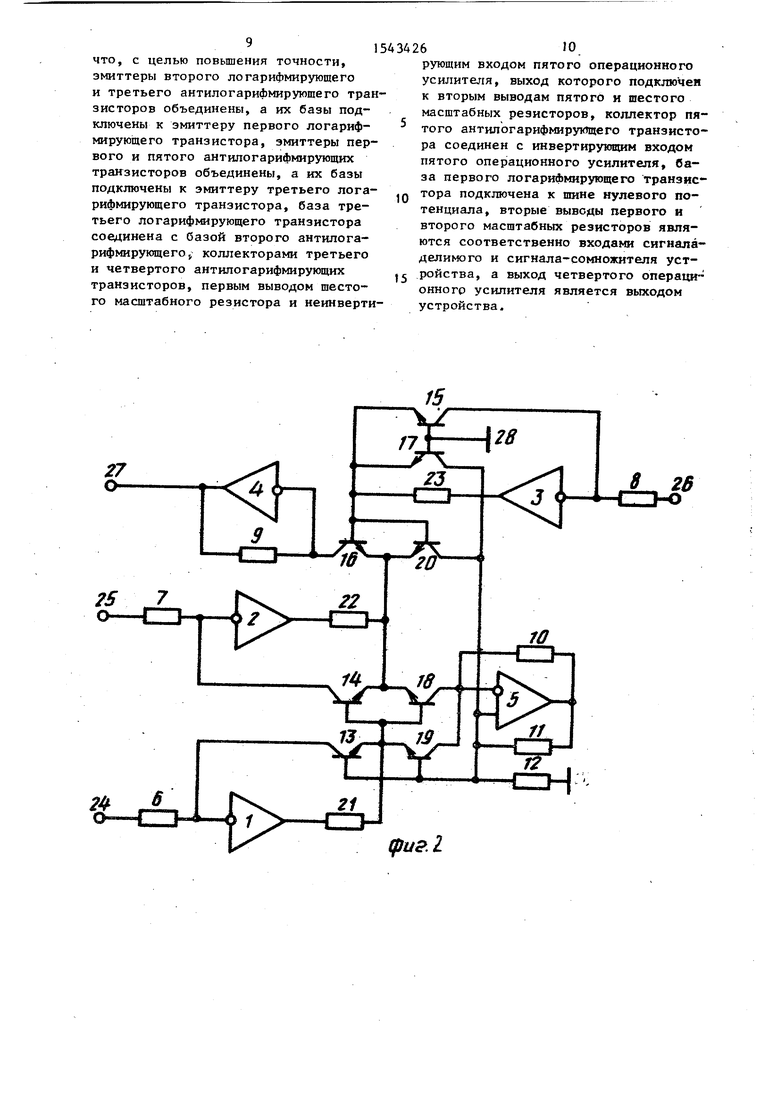

(фиг. 1 и 2) содержит первый 1, второй 2, третий 3, четвертый 4 и пятый 15 операционные усилители, первый 6, (второй 7, третий 8, четвертый 9, пя- гый 10 и шестой 1 I масштабные резис- оры, компенсирующий резистор 12, пер- йыи J3, второй 14 и третий 15 логарифмирующие транзисторы, первый 16, второй 17, третий 18, четвертый 19 и пятранзистора 15 соединена с неинвертирующим входом операционного усилителя 5, коллекторами антилогарифмирующих транзисторов 19 и 18, первыми 25 выводами масштабного 11 и компенсиру ющего 12 резисторов. Вторые выводы масштабных резисторов 10 и 11 подключены к выходу операционного усили теля 5. Второй вывод компенсирующего

i-ый 20 антилогарифмирующие транзисто- -jo резистора 12, а также базы логариф35

40

ры, первый 21, второй 22 и третий 23 токоограничительные резисторы, входы игнала-делимого 24, сигнала-сомно- э ителя 25 и сигнала-делителя 26, выход устройства 27 и шину 28 нулевого Потенциала.

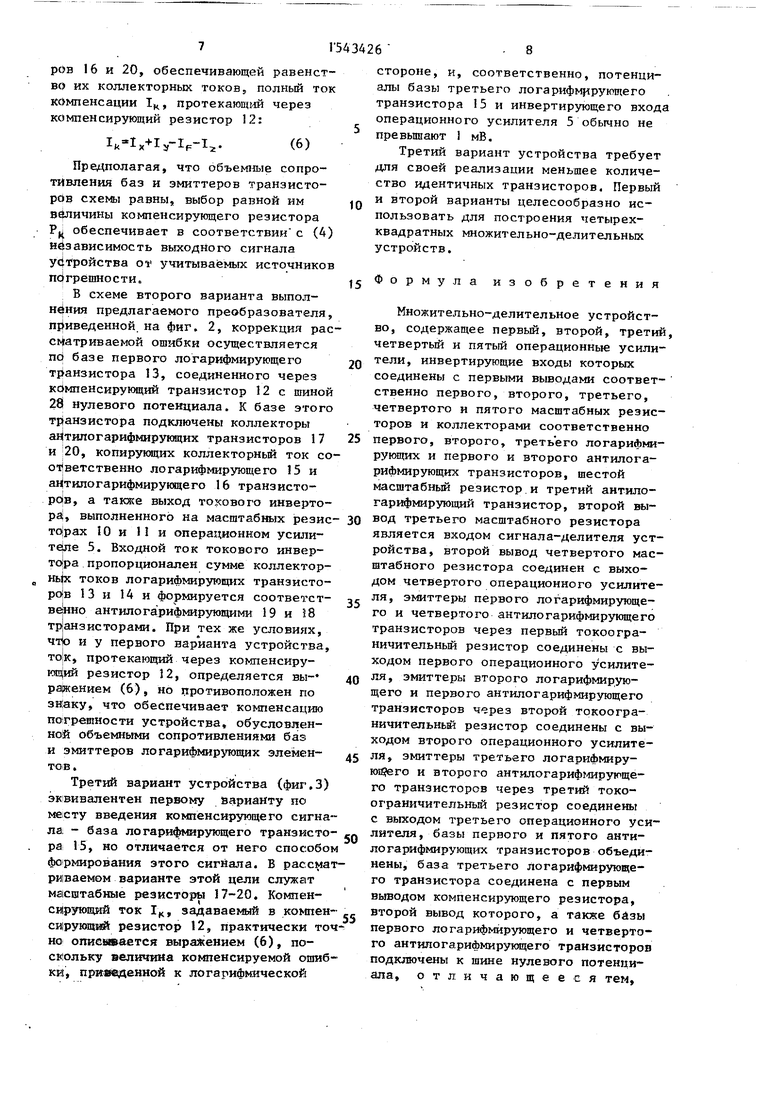

В схеме третьего варианта устрой- фтва (фиг. 3) позициями i7-20 обозна- Цены седьмой-десятый масштабные ре- исторы.

В множительно-делителг ном устройстве по фиг. 1 инвертирующие входы операционных усилителей 1-5 соединены с первыми выводами соответственно масштабных резисторов 6-10 и с коллекторами соответственно логарифмирующих 13-15 и антилогарифмирующих 16 И 20 транзисторов. Вторые выводы масштабных резисторов 6-8 являются сюответственно входами 24-26 сигнала- ,д делимого, сигнала-сомножителя и сигнала-делителя 26 устройства соответственно. Эмиттеры логарифмирующего 13 til антилогарифмирующего 19 транзисторов, а также базы логарифмирующего . 14 и антилогарифмирующего 13 транзисторов соединены через токоограничи- тельный резистор 2I с выходом операционного усилителя 1. Эмиттеры логариф45

мирующего 13 и антилогарифмирующего 19 транзисторов соединены с шиной нулевого потенциала 28.

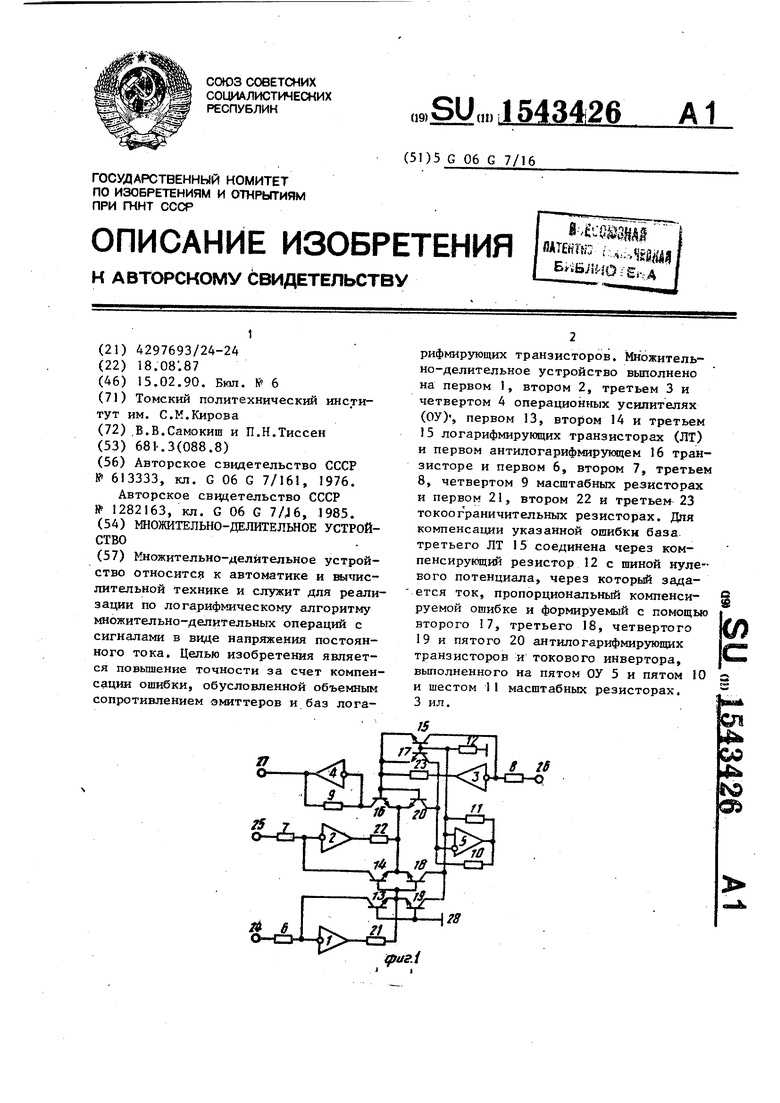

В схеме предлагаемого устройства по второму варианту в отличие от пер вого, базы логарифмирующего 13 и ант ло гарифмирующе го 19 транзисторов соединены с первыми выводами масштаб ного II и компенсирующего 12 резисто ров, неинвертирующим входом операционного усилителя 5 и коллекторами ан тило гарифмирующих усилителей 17 и 20 коллекторы антилогарифмирующих транзисторов 19 и 18 соединены с инвертирующим входом операционного усилителя 5 и первым выводом масштабного резистора 10, а базы логарифмирующего 15 и антилогарифмирующего 17 тран зисторов подключены к шине 28 нулевого потенциала,.

В схеме третьего варианта устройства, в оаличие от первого, исключены второй, третий, четвертый и пятый антилогарифмирующие транзисторы, а их Функции выполняют седьмой 17, вос мой 18, девятый 19 и десятый 20 масштабные резисторы. Первые выводы 18 масштабных резисторов 17 и 18 соединены с инвертирующим входом операцирезистора 10. База логарифмирующего

транзистора 15 соединена с неинвертирующим входом операционного усилителя 5, коллекторами антилогарифмирующих транзисторов 19 и 18, первыми выводами масштабного 11 и компенсирующего 12 резисторов. Вторые выводы масштабных резисторов 10 и 11 подключены к выходу операционного усилителя 5. Второй вывод компенсирующего

5

0

д

5

мирующего 13 и антилогарифмирующего 19 транзисторов соединены с шиной нулевого потенциала 28.

В схеме предлагаемого устройства по второму варианту в отличие от первого, базы логарифмирующего 13 и антило гарифмирующе го 19 транзисторов соединены с первыми выводами масштабного II и компенсирующего 12 резисторов, неинвертирующим входом операционного усилителя 5 и коллекторами антило гарифмирующих усилителей 17 и 20; коллекторы антилогарифмирующих транзисторов 19 и 18 соединены с инвертирующим входом операционного усилителя 5 и первым выводом масштабного резистора 10, а базы логарифмирующего 15 и антилогарифмирующего 17 транзисторов подключены к шине 28 нулевого потенциала,.

В схеме третьего варианта устройства, в оаличие от первого, исключены второй, третий, четвертый и пятый антилогарифмирующие транзисторы, а их Функции выполняют седьмой 17, восьмой 18, девятый 19 и десятый 20 масштабные резисторы. Первые выводы 18 масштабных резисторов 17 и 18 соединены с инвертирующим входом операци

онного усилителя 5, а первые выводы 20 масштабных резисторов 19 и 20 соединены с базой логарифмирующего транзистора 15. Вторые выводы масштабных резисторов 17-20 соединены соответст- венно с входом 24 сигнала-делимого, сигнала-сомножителя 25 и сигнала- делителя 26 и выходом 27 устройства.

Предлагаемое устройство работает следующим образом.

Во всех трех вариантах операционные усилители 1-4, логарифмирующие 13-15 и антилогарифмирующий 16 транзисторы, второй 7, третий 8, четвер- тый 9, первый 21, второй 22 и третий 23 токобграничительные 6-9, 21-23 и компенсирующий 12 резисторы образуют одноквадратный логарифмический вычислитель, реализующий выражение вида () с однополярными входными сигналами (положительными в случае использования п-р-п-транзисторов).

В первом варианте устройства (фиг. 1) для компенсации ошибки, обу- словленной объемными сопротивлениями баз и эмиттеров логарифмирующих и антилогарифмирующего транзисторов, база третьего логарифмирующего транзистора 15 соединена с шиной 28 ну- левого потенциала через компенсирующий резистор 12 величиной Р. , через который с помощью остальных элементов схемы задается т.ок 1К, пропорциональный напряжению огибки, приведенной к логарифмической стороне.

Первый операционный усилитель 1 по цепи: токоограничительный резистор 21, переход эмиттер - база первого логарифмирующего транзистора 13 задает ток коллектора Тх, пропорциональный напряжению на входе 24 сигнала- делимого. При этом напряжение на переходе база-эмиттер первого логариф- мирующего транзистора 15 равно логарифму сигнала с входа 24. Второй операционный усилитель 2 по цепи: токот ограничительный резистор 22, переход эмиттер - база второго логарифмирую- щего транзистора 14 задает ток коллектора последнего I , пропорциональный сигналу-сомножителю с входа 26. При этом на эмиттере первого антилогарифмирующего транзистора 16 фор- мируются сигнал

l/Tln Ь +ЦП.П Ь +1,

rx+Ivrv,

где 0,026 В - температурный потенциал;

I - тепловой ток эмиттерных переходов транзисторов. Операционный усилитель 3 через токоограничительный резистор 23, переход эмиттер - база логарифмирующего транзистора 15 устанавливает коллекторный ток последнего 12 пропорциональным напряжению на входе 27 сигнала-делителя . Напряжение на эмиттер- ном переходе первого антилогарифмирующего транзистора 16 с учетом падения напряжения на его объемном сопротивлении -базы и эмиттера и тока IK через компенсирующий резистор 12:

in Ј +IFrF-4Vln ЈЈ +lxrx+

e

+isr,-if in -± .RK,

о

где,If - ток антилогарифмирующего

транзистора 16.

Поскольку все транзисторы схемы идентичны и тепловые токи их эмиттерных переходов равны, то напряжение на выходе 27 устройства пропорционально току

l . LL exP(b ibr I2E2iMЈ).(4)

Как видно, погрешность преобразования носит мультипликативный характер, причем величина подлежащего компенсации напряжения в числителе экспоненты обычно не превосходит 1 м В, что соответствует относительной ошибке преобразования 4%.

Операционный усилитель 5, масштабные резисторы 10 и И образуют схему токового инвертора, коэффициент передачи которого определяется отношением указанных масштабных резисторов. При равенстве масштабных резисторов 10 и 11 и в силу идентичности параметров и режимов логарифмирующего 13 и антилогарифмирующего 19 транзисторов, а также логарифмирующего 14 и антилогарифмирующего 18 транзисторов выходной ток токового инвертора (ток через шестой масштабный резистор) равен

1х+1„.

(5)

до д550 55

В силу идентичности параметров и режимов логарифмирующего 15 и антилогарифмирующего 17 транзисторов, а также антилогарифмирующих транзисторов 16 и 20, обеспечивающей равенство их коллекторных токов, полный ток компенсации 1К, протекающий через компенсирующий резистор 12:

,-Ip-I.,.

(6)

Предполагая, что объемные сопротивления баз и эмиттеров транзисторов схемы равны, выбор равной им величины компенсирующего резистора Ри обеспечивает в соответствии с (4) независимость выходного сигнала устройства of учитываемых источников погрешности.

В схеме второго варианта выпол- нения предлагаемого преобразователя, приведенной, на фиг. 2, коррекция рассматриваемой ошибки осуществляется по базе первого логарифмирующего транзистора 13, соединенного через компенсирующий транзистор 12 с шиной 28 нулевого потенциала. К базе этого транзистора подключены коллекторы айтилогарифмнрующих транзисторов 17 и 20, копирующих коллекторный ток соответственно логарифмирующего 15 и ан|тилогарифмирующего 16 транзисто- рЬв, а также выход токового инвертора, выполненного на масштабных резис- 10 и 11 и операционном усилителе 5. Входной ток токового инвертора пропорционален сумме коллекторных токов логарифмирующих транэисто- 13 и 14 и формируется соответст- антилогарифмирующими 19 и 18 транзисторами. При тех же условиях, чтю и у первого варианта устройства, то к, протекающий через компенсирующий резистор 12, определяется вы- ранением (6), но противоположен по знаку, что обеспечивает компенсацию погрешности устройства, обусловленной объемными сопротивлениями баз и эмиттеров логарифмирующих элемен-

ТО В .

Третий вариант устройства (фиг.З) эквивалентен первому варианту по месту введения компенсирующего сигнала, - база логарифмирующего транзисто- pa 15, но отличается от него способом формирования этого сигнала. В рассматриваемом варианте этой цели служат масштабные резисторы 17-20. Компенсирующий ток 1ц, задаваемый в компен- сирующнй резистор 12, практически точно описывается выражением (6), поскольку величина компенсируемой ошибки, приведенной к логарифмической

стороне, и, соответственно, потенциалы базы третьего логарифмирующего транзистора 15 и инвертирующего входа операционного усилителя 5 обычно не превышают 1 мВ.

Третий вариант устройства требует для своей реализации меньшее количество идентичных транзисторов. Первый и второй варианты целесообразно использовать для построения четырех- квадратных множительно-делительных устройств.

Формула изобретения

Множительно-делительное устройство, содержащее первый, второй, третий четвертый и пятый операционные усилители, инвертирующие входы которых соединены с первыми выводами соответ- ственно первого, второго, третьего, четвертого и пятого масштабных резисторов и коллекторами соответственно первого, второго, третьего логарифмирующих и первого и второго антилога- рифмирующих транзисторов, шестой масштабный резистор и третий антило- гарифмирующий транзистор, второй вывод третьего масштабного резистора является входом сигнала-делителя устройства, второй вывод четвертого масштабного резистора соединен с выходом четвертого операционного усилителя, эмиттеры первого логарифмирующего и четвертого антилогарифмирующего транзисторов через первый токоогра- ничительный резистор соединены с выходом первого операционного усилителя, эмиттеры второго логарифмирующего и первого антилогарифмирующего транзисторов через второй токоогра- ничительный резистор соединены с выходом второго операционного усилителя, эмиттеры третьего логарифмиру- и второго антилогарифмирующего транзисторов через третий токо- ограничительный резистор соединены с выходом третьего операционного усилителя, базы первого и пятого анти- логарифмирующих транзисторов объединены, база третьего логарифмирующего транзистора соединена с первым выводом компенсирующего резистора, второй вывод которого, а также базы первого логарифмирующего и четвертого антилогарифмирующего транзисторов подключены к шине нулевого потенциала, отличающееся тем,

что, с целью повышения точности, эмиттеры второго логарифмирующего и третьего антилогарифмируюшего транзисторов объединены, а их базы подключены к эмиттеру первого логарифмирующего транзистора, эмиттеры первого и пятого антилогарифмирующих транзисторов объединены, а их базы подключены к эмиттеру третьего логарифмирующего транзистора, база третьего логарифмирующего транзистора соединена с базой второго антилога- рифмирующего,, коллекторами третьего и четвертого антилогарифмирующих транзисторов, первым выводом шестого масштабного резистора и неинверти

рующим входом пятого операционного усилителя, выход которого подключен к вторым выводам пятого и шестого масштабных резисторов, коллектор пятого антилогарифмируюшего транзистора соединен с инвертирующим входом пятого операционного усилителя, база первого логарифмирующего транзистора подключена к шине нулевого потенциала, вторые выводы первого и второго масштабных резисторов являются соответственно входами сигнала- делимого и сигнала-сомножителя устройства, а выход четвертого операци- онногр усилителя является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехквадратное множительно-делительное устройство | 1987 |

|

SU1474686A1 |

| Вычислительное устройство | 1987 |

|

SU1539798A1 |

| Вычислительное устройство | 1987 |

|

SU1462364A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Аналоговое логарифмическое вычислительное устройство | 1982 |

|

SU1095198A1 |

| Аналоговое логарифмическое вычислительное устройство | 1983 |

|

SU1137486A2 |

| Устройство с регулируемым усилением | 1988 |

|

SU1741257A1 |

| Аналоговый экспоненциальный преобразователь | 1982 |

|

SU1101849A1 |

| Среднеквадратический преобразователь | 1985 |

|

SU1275302A1 |

Множительно-делительное устройство относится к автоматике и вычислительной технике и служит для реализации по логарифмическому алгоритму множительно-делительных операций с сигналами в виде напряжения постоянного тока. Целью изобретения является повышение точности за счет компенсации ошибки, обусловленной объемным сопротивлением эмиттеров и баз логарифмирующих транзисторов. Множительно-делительное устройство выполнено на первом 1, втором 2, третьем 3 и четвертом 4 операционных усилителях (ОУ), первом 13, втором 14 и третьем 15 логарифмирующих транзисторах (ЛТ) и первом антилогарифмирующем 16 транзисторе и первом 6, втором 7, третьем 8, четвертом 9 масштабных резисторах и первом 21, втором 22 и третьем 23 токоограничительных резисторах. Для компенсации указанной ошибки база третьего ЛТ 15 соединена через компенсирующий резистор 12 с шиной нулевого потенциала, через который задается ток, пропорциональный компенсируемой ошибке и формируемый с помощью второго 17, третьего 18, четвертого 19 и пятого 20 антилогарифмирующих транзисторов и токового инвертора, выполненного на пятом ОУ 5 и пятом 10 и шестом 11 масштабных резисторах. 3 ил.

8 26

(риг 2.

$u&3

| Аналоговое множительное устройство | 1976 |

|

SU613333A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-15—Публикация

1987-08-18—Подача