ел

00

ел

Изобретение относится к информационно-измерительной технике и может быть использовано в системах регистрации и обработки сигналов в услови- як помех.

Цель изобретения - повышение точности при отношении сигнал/шум меньше единицы.

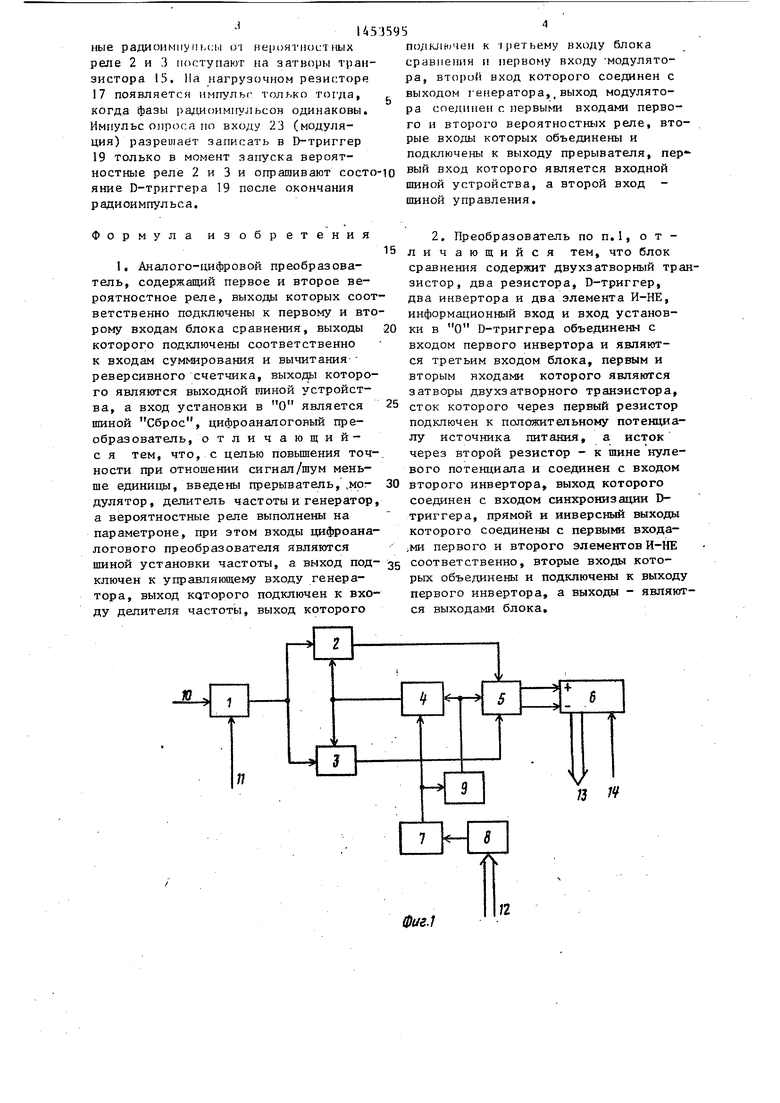

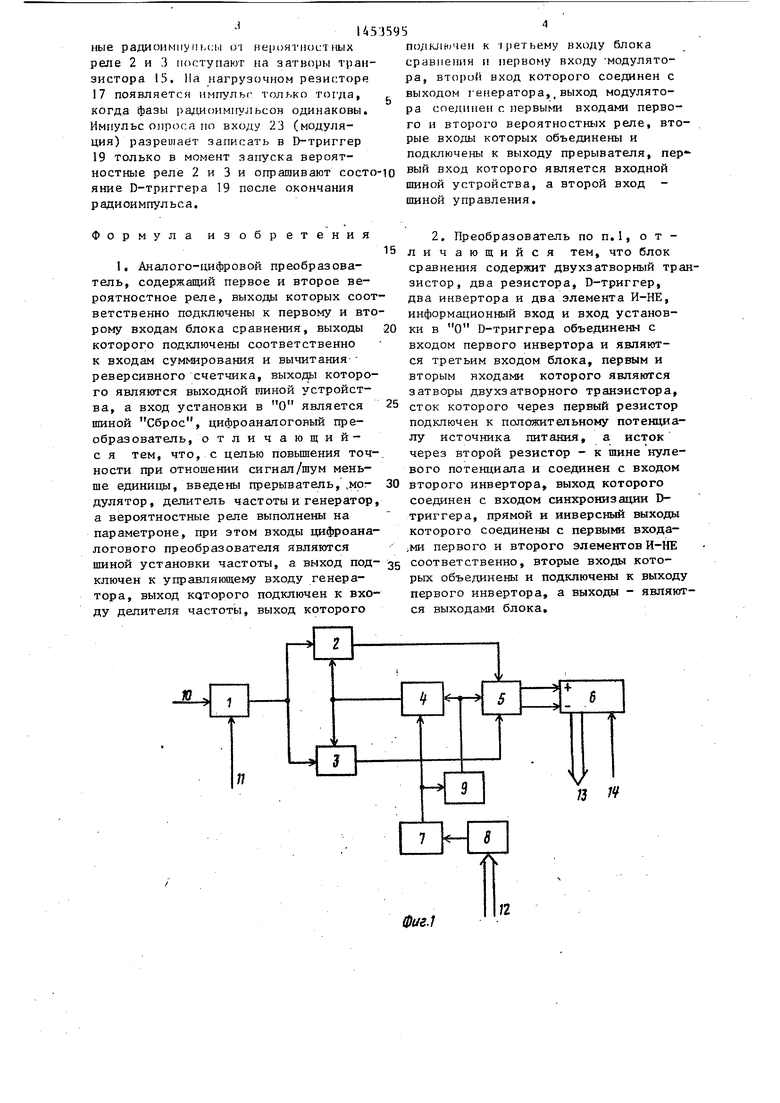

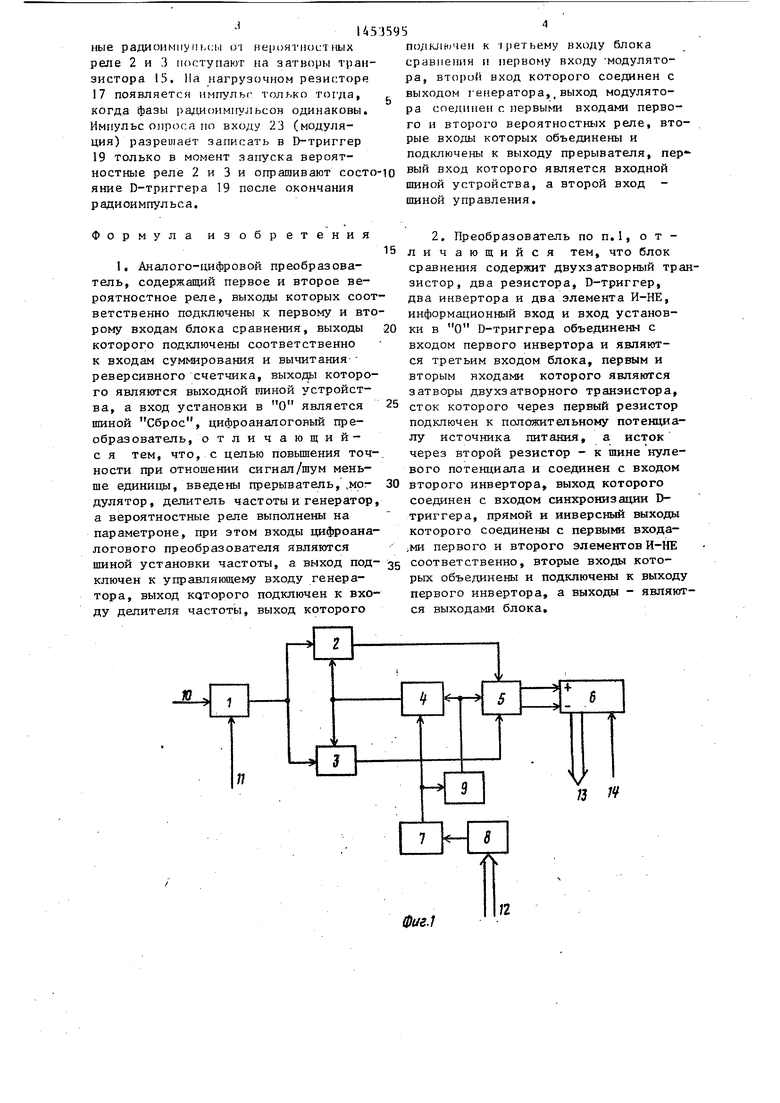

На фиг,1 представлена функциональ ная схема устройства; на фиг,2 - приципиальная схема блока сравнения.

Аналого-цифровой статистический преобразователь (фиг,1) содержит прерыватель 1, вероятностные реле 2 и 3, модулятор 4, блок 5 сравнения (фазовый детектор), реверсивный счетчик 6, генератор 7, цифроаналоговый преобразователь (ЦАП) 8, делитель 9 частоты, входную пгану 10, шину 11

управления, шину 12 Установка частоты, выходную шину 13 и шину 14 Сброс,

Блок сравнения (фиг,2) содержит двухзатворный транзистор 15, первый и второй резисторы 16 и 17, второй инвертор 18, D-триггер 19, первый инвертор 20, элементы 2И-НЕ 21, и 22, входную 23 и выходные 24 и 25 шины блока,

Аналого-цифровой преобразователь работает следуютщм образом.

По входной шине 10 на вход прерывателя 1 поступает сигнал, представ- лякщий собой аддитивную смесь полез- ного сигнала, амплитуду которого необходимо измерить, и шума, причем частота полезного сигнала априорно известна,Генератор 7 накачки вырабатывает частоту накачки вероятност- ных реле 2 и 3 в соотношении 2fj. - f,Управление частотой накачки осуществляется гтри помоши ДАЛ 8, на вход которого по шине 12 поступает код, соответствующий необходимой

частоте накачки.

Вероятностные реле 2 и 3 опредапя ют в условиях помех апостериорные вероятности попадания суммарной фазы сигнала и помехи в одну из возмож ных зон фазы 0-180°, 180 -360° относительно фазы частоты накачки, т.ео осуществляют квантование на два уровня фазы сигнала. Возможны только два состояния фазы сигнала на выходе веро ятностных реле 2 и 3 О или П, соответствуюпще начальным значениям фазы сигнала в момент возбуждения вероятностных реле

0

0

5 о 5

5

Модулятор 4 осуществляет ЛМ-моду- ляцию частоты накачки, Блок 5 сравнения при совпадении фаз радиоимпульсов на его первом и втором входах вырабатывает импульс на выходе 25, а при несовпадении фаз - на выходе 24, Делитель 9 частоты осуществляет синхронное деление частоты накачки на заданный коэффициент деления и вырабатывает импульсы управления модулятором 4,,

Реверсивный счетчик 6 осуществляет накопление результатов серии замеров, В исходном состоянии реверсивный счетчик 6 по шине Сброс устанавливается в нулевое состояние, а входная lUHHa 10 через прерыватель 1 подключена к входам вероятностных реле 2 и 3,

В режиме измерения делитель 9 частоты вырабатывает импульсы модуляции. При этом вероятностные реле 2 и 3 периодически возбуждаются. Если на входной шине 10 регулярный сигнал отсутствует, то установление колебаний с фазами О или П на их выходах равновероятно и показание реверсивного счетчика 6 минимально. Если на входной шине 10 присутствует полезный сигнал с частотой ц, то будут частые совпадения фаз на выходах вероятностных реле 2 и 3 и показания реверсивного счетчика 6 увеличиваются

Показания реверсивного счетчика б прямо пропорциональны амплитуде сигнала f Это справедливо и для отношений сигнал/помеха менее цы. Таким образом, код на выходе реверсивного счетчика отражает амплитуду входного сигнала,

В р ежиме калибровки устройства по шине 11 на вход прерывателя 1 поступает сигнал, по которому входная шина 10 отключается от устройства. За серию измерений определяют уровень собственных шумов вероятностных реле 2 и 3, Этот результат используется как значение порогов для принятия решения есть полезный сигнал или нет при последующих измерениях, а также при уточнении истинного значения амплитуды входного сигнала.

Реализация блока 5 сравнения зависит от частоты полезного сигнала. Приведенная на фиг,2 принципиальная ;, схема блока 5 позволяет обрабатывать сигналы в диапазоне до 50 МГц, Входные радиоимиуп}лл.1 от нероятностных репе 2 и 3 поступают на затворы транзистора 15. На нагрузочном резисторе 17 появляется нмггульс только тог да, когда фазы pa a oимкyJIьcoв одинаковы. Импульс опроса по входу 23 (модуляция) разрешает записать в D-триггер 19 только в момент запуска вероятностные реле 2 и 3 и опрашивают состо яние D-триггера 19 после окончания радиоимпульса.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий первое и второе вероятностное реле, выходы которых соответственно подключены к первому и второму входам блока сравнения, выходы которого подключены соответственно к входам суммирования и вычитания- реверсивного счетчика, выходы которого являются выходной ршной устройст

ва, а вход установки в О является шиной Сброс, цифроаналоговый преобразователь, отличающий- с я тем, что, с целью повьшения точности при отношении сигнал/шум меньше единицы, введены прерыватель, .мог дулятор, делитель частоты и генератор а вероятностные реле выполнены на параметроне, при этом входы цифроана- логового преобразователя являются шиной установки частоты, а выход под- ключен к управляющему входу генератора, выход которого подключен к входу делителя частоты, выход которого

0

15

20

25

30 35

подключен к третьему входу блока сравнения и первому входу модулятора, второй вход которого соединен с выходом reEiepaTopa,, выход модулятора соединен с первыми входами первого и второго вероятностных реле, вторые входы которых объединены и подключены к выходу прерывателя, вый вход которого является входной шиной устройства, а второй вход - шиной управления.

2, Преобразователь по п.1, о т - личающийся тем, что блок сравнения содержит двухзатворный транзистор, два резистора, D-триггер, два инвертора и два элемента И-НЕ, информационный вход и вход установки в О D-триггера объединены с входом первого инвертора и являются третьим входом блока, первым и вторым входами которого являются затворы двухзатворного транзистора, сток которого через первый резистор подключен к положительному потенциалу источника питания, а исток через второй резистор - к шине нулевого потенциала и соединен с входом второго инвертора, выход которого соединен с входом синхронизации D- триггера, прямой и инверсный выходы которого соединены с первыми входа- ;МИ первого и второго элементов И-НЕ соответственно, вторые входы которых объединены и подключены к выходу первого инвертора, а выходы - являются выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1640823A1 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2001 |

|

RU2187824C1 |

| Устройство преобразования сигнала с датчика | 1989 |

|

SU1651364A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Следящий аналого-цифровой преобразователь | 1983 |

|

SU1181116A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2045813C1 |

| Устройство фазовой автоподстройки частоты | 1984 |

|

SU1166301A1 |

| Дельта-модулятор | 1990 |

|

SU1709531A2 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ МЕТАНА И ДРУГИХ ГОРЮЧИХ ГАЗОВ | 1991 |

|

RU2013565C1 |

Изобретение относится к информа- дионно-иямерительной технике и мо- , жет быть использовано в системах регистрации и обработки сигналов в условиях помехо Изобретение позволяет повысить точность измерения регулярного сигнала при отношении сигнал/помеха меньше единицы за счет того, что в устройство, содержащее первое и второе вероятностные реле, блок сравнения, реверсивный счетчик и цифроаналоговый преобразователь, введены прерыватель, модулятор, генератор частоты и делитель частоты. Введение этих блоков позволило повысить точность измерения амплитуды входного регулярного сигнала при отношении сигнал/помеха меньше единицы за счет применения пассивного квантователя, имеюп;его малые собственные шумы. 1 3.п. ф-лы, 2 ил. f (Л

JbO

/7

Составитель В.Гейнрихс Редактор Н.Яцола Техред М.Ходанич

Заказ 7301/55

Тира)с 879

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ CCCi 113035, Москва, Ж-35, Раушская наб., д. 4/

19

22

2

фие.2

Корректор Э .Лончакова

Подписное

| Комолов В.П | |||

| и др | |||

| Параметроны в цифровых устройствах | |||

| - Библиотека по автоматике, М.: Энергия, 1968 | |||

| Следящий аналого-цифровой преобразователь | 1983 |

|

SU1181116A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-01-23—Публикация

1986-12-26—Подача