VI

О О СЛ Сл)

Изобретение относится к автоматике и вычислительной технике,может применяться для преобразования непрерывного аналогового сигнала в дельта-кодовые и импульсно-кодовомодулированные последовательности при построении адаптивных корреляционно-измерительных систем для идентификации образов и является дополнительным к основному авт.св. Ms 1448411.

Цель изобретения - повышение точности дельта-модулятора.

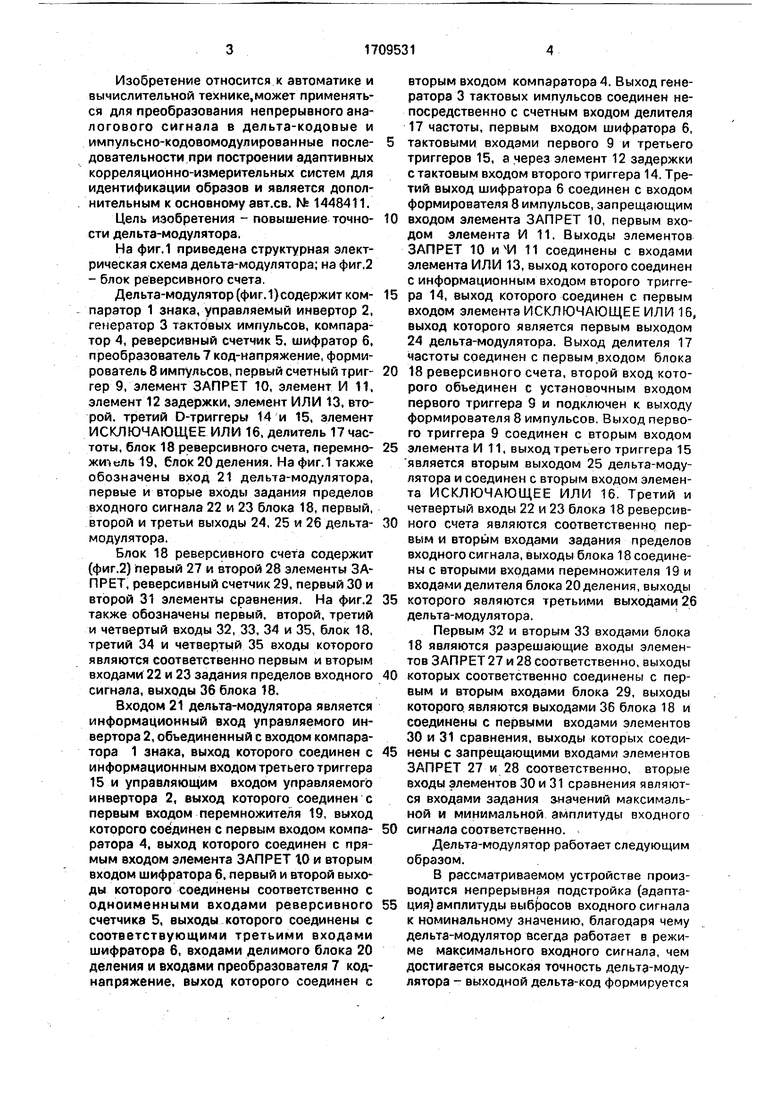

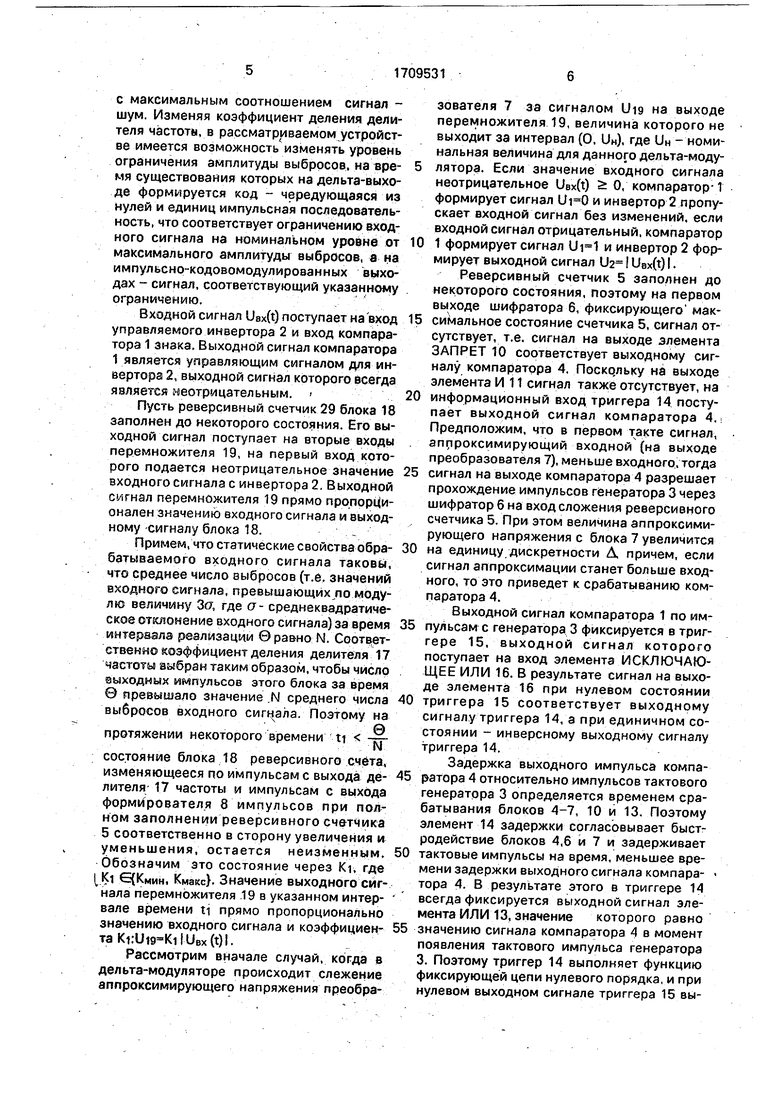

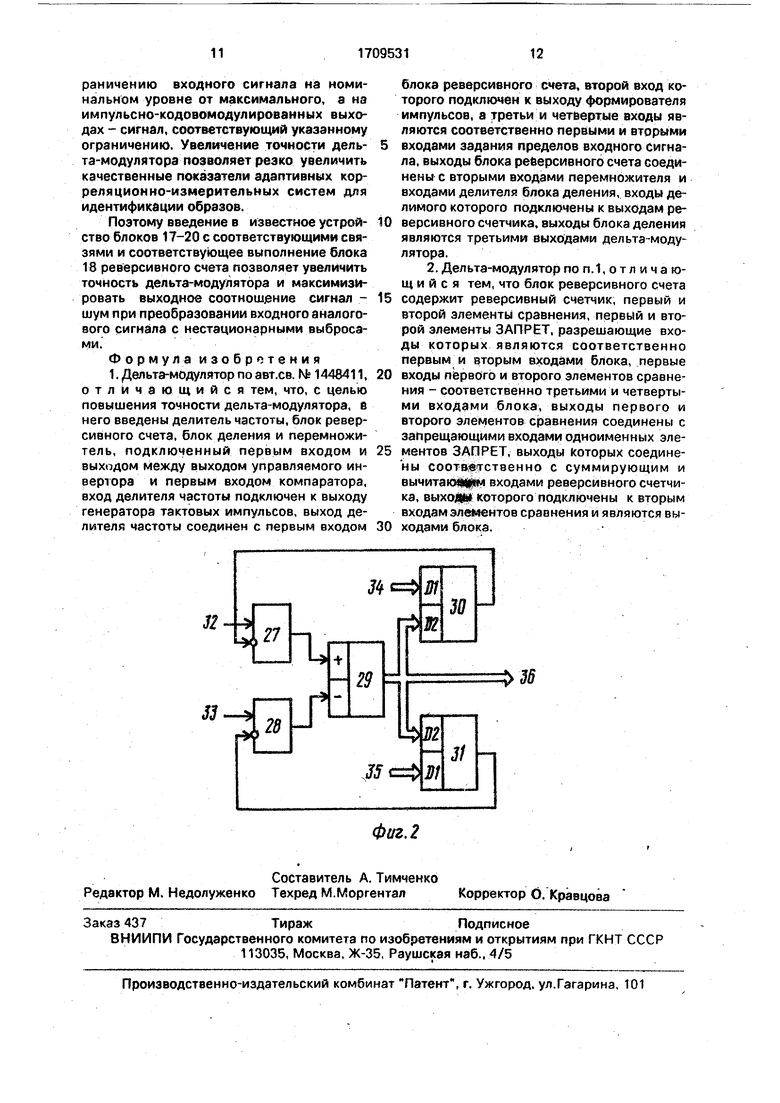

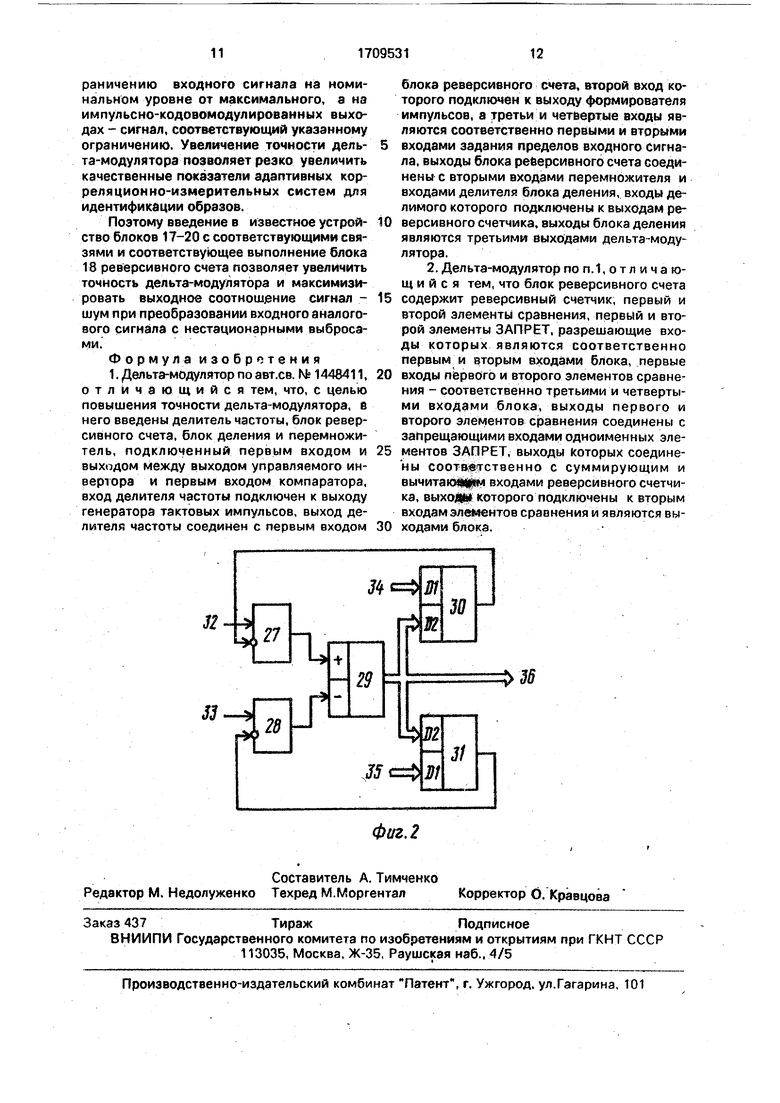

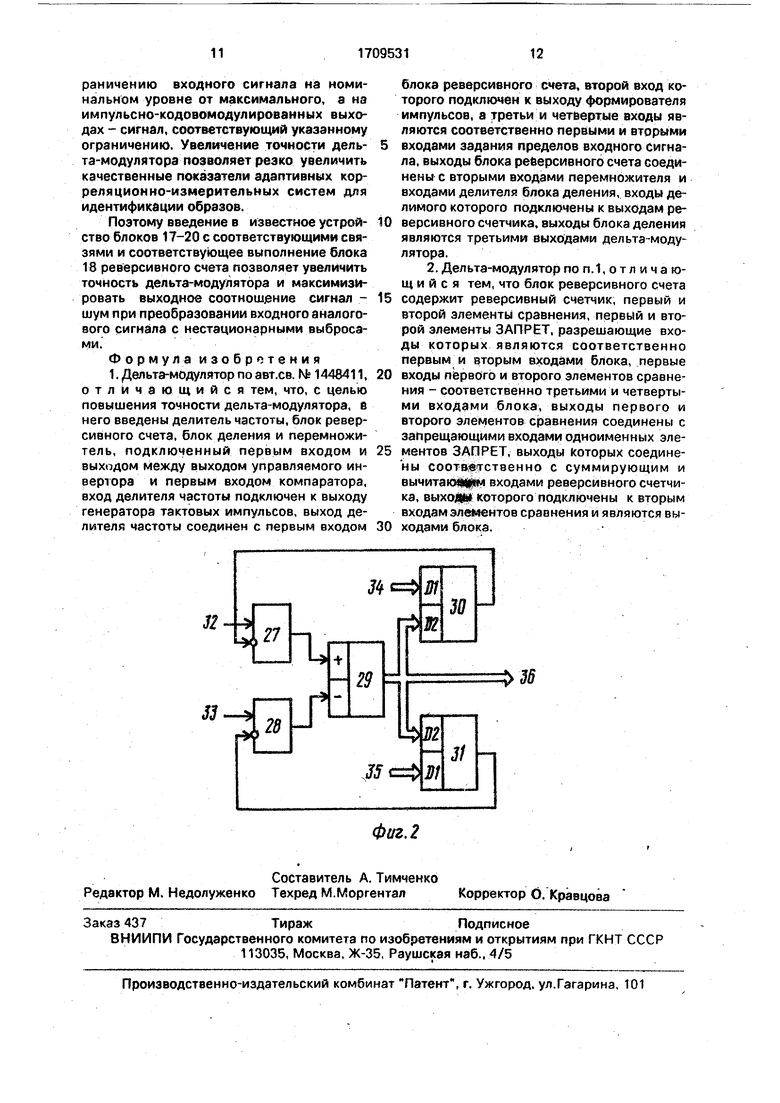

На фиг.1 приведена структурная электрическая схема дельта-модулятора; на фиг.2 - блок реверсивного счета.

Дельта-модулятор (фиг. 1) содержит компаратор 1 знака, управляемый инвертор 2, генератор 3 тактовых импульсов, компаратор 4, реверсивный счетчик 5, шифратор 6, преобразователь код-напряжение, формирователь 8 импульсов, первый счетный триггер 9, элемент ЗАПРЕТ 10, элемент И 11. элемент 12 задержки, элемент ИЛИ 13, второй, третий Ь-триггеры 14 и 15, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16, делитель 17 частоты, блок 18 реверсивного счета, перемножтель 19, блок 20 деления. На фиг.1 также обозначены вход 21 дельта-модулятора, первые и вторые входы задания пределов входного сигнала 22 и 23 блока 18, первый, второй и третьи выходы 24, 25 и 26 дельтамодулятора.

Блок 18 реверсивного счета содержит (фиг.2) первый 27 и второй 28 элементы ЗАПРЕТ, реверсивный счетчик 29, первый 30 и второй 31 элементы сравнения. На фиг.2 также обозначены первый, второй, третий и четвертый входы 32, 33, 34 и 35, блок 18, третий 34 и четвертый 35 входы которого являются соответственно первым и вторым входами 22 и 23 задания пределов входного сигнала, выходы 36 блока 18.

Входом 21 дельта-модулятора является информационный вход управляемого инвертора 2, объединенный с входом компаратора 1 знака, выход которого соединен с информационным входом третьего триггера 15 и управляющим входом управляемого инвертора 2, выход которого соединен с первым входом перемножителя 19, выход которого соединен с первым входом компаратора 4, выход которого соединен с прямым входом элемента ЗАПРЕТ 10 и вторым входом шифратора 6, первый и второй выходы которого соединены соответственно с одноименными входами реверсивного счетчика 5, выходы которого соединены с соответствующими третьими входами шифратора 6, входами делимого блока 20 деления и входами преобразователя 7 коднапряжение, выход которого соединен с

вторым входом компаратора 4. Выход генератора 3 тактовых импульсов соединен непосредственно с счетным входом делителя

17частоты, первым входом шифратора 6, тактовыми входами первого 9 и третьего

триггеров 15, а через элемент 12 задержки с тактовым входом второго триггера 14. Третий выход шифратора 6 соединен с входом формирователя 8 импульсов, запрещающим

0 входом элемента ЗАПРЕТ 10, первым входом элемента И 11. Выходы элементов ЗАПРЕТ 10 и И 11 соединены с входами элемента ИЛИ 13, выход которого соединен с информационным входом второго тригге5 ра 14, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16, выход которого является первым выходом 24 дельта-модулятора. Выход делителя 17 частоты соединен с первым.входом блока

0 18 реверсивного счета, второй вход которого объединен с установочным входом первого триггера 9 и подключен к выходу формирователя 8 импульсов. Выход первого триггера 9 соединен с вторым входом

5 элемента И 11, выход третьего триггера 15 является вторым выходом 25 дельта-модулятора и соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16. Третий и четвертый входы 22 и 23 блока 18 реверсивного счета являются соответственно первым и вторым входами задания пределов входного сигнала, выходы блока 18 соединены с вторыми входами перемножителя 19 и входами делителя блока 20 деления, выходы

5 которого являются третьими выходами 26 дельта-модулятора.

Первым 32 и вторым 33 входами блока

18являются разрешающие входы элементов ЗАПРЕТ 27 и 28 соответственно, выходы

0 которых соответственно соединены с первым и вторым входами блока 29, выходы которого, являются выходами 36 блока 18 и соединены с первыми входами элементов 30 и 31 сравнения, выходы которых соединены с запрещающими входами элементов ЗАПРЕТ 27 и 28 соответственно, вторые входы элементов 30 и 31 сравнения являются входами задания значений максимальной и минимальной амплитуды входного

0 сигнала соответственно.

Дельта-модулятор работает следующим образом.

В рассматриваемом устройстве производится непрерывная подстройка (адаптация) амплитуды Bbi6f)ocoB входного сигнала к номинальному значению, благодаря чему дельта-модулятор всегда работает в режиме максимального входного сигнала, чем достигается высокая точность дельта-модулятора - выходной дельта-код формируется с максимальным соотношением сигнал шум. Изменяя коэффициент деления делителя частоты, в рассматриваемом устройстве имеется возможность изменять уровень ограничения амплитуды выбросов, на время существования которых на дельта-выходе формируется код - чередующаяся из нулей и единиц импульсная последовательность, что соответствует ограничению входного сигнала на номинальном уровне от максимального амплитуды выбросов, а на импульснр-кодовомодулированных выходах - сигнал, соответствующий указанному ограничению. Входной сигнал UexCt) поступает на вход управляемого инвертора 2 и вход компаратора 1 знака. Выходной сигнал компаратора 1 является управляющим сигналом для инвертора 2, выходной сигнал которого всегда является меотрицательным. Пусть реверсивный счетчик 29 блока 18 заполнен до некоторого состояния. Его выходной сигнал поступает на вторые входы перемножителя 19, на первый вход которого подается неотрицательное значение входного сигнала с инвертора 2. Выходной сигнал перемножителя 19 прямо пропорционален значению входного сигнала и выходному-сигналу блока 18.-Примем, что статические свойства обрабатываемого входного сигнала таковы, что среднее число аыбросов (т.е. значений входного сигнала, превышающих по модулю величину Зо, где о- среднеквадратическое отклонение входного сигнала) за время интервала реализации 0 ра&но N. Соотв тственно коэффициент деления делителя 17 частоты выбран таким образом, чтобы число аыходных импульсов этого блока за время 0 превышало значение .N среднего числа выбросов входного . Поэтому на протяжении некоторого времени tr состояние блока 18 реверсивного счета, изменяющееся по импульсам с выхода делителя; 17 частоты и импульсам с выхода форм14 рователя 8 импульсов при полном заполнении реверсивного счетчика 5 соответственно в сторону увеличения и уменьшения, остается неизменным. Обозначим это состояние через Ki, где €{Кмин, Кмакс}. Значение выходного сигнала перемножителя .19 в указанном интервале времени ti прямо пропорционально значению входного сигнала и коэффициенTaKi:Ui9 KilUBx(t)l.J Рассмотрим вначале случай, когда в дельта-модуляторе происходит слежение аппроксимирующего напряжения преобразователя 7 за сигналом Uig на выходе перемножителя 19, величина которого не выходит за интервал (О, UH), где UH - номинальная величина для данного дельта-модулятора. Если значение входного сигнала неотрицательное UexW 2: О, компаратор- Т формирует сигнал и инвертор 2 пропускает входной сигнал без изменений, если входной сигнал отрицательный, компаратор 1 формирует сигнал и инвертор 2 формирует выходной сигнал U2 I Uaxfr) I. Реверсивный счетчик 5 заполнен до некоторого Состояния, поэтому на первом выходе шифратора 6, фиксирующего максимальное состояние счетчика 5, сигнал отсутствует, т.е. сигнал на выходе элемента ЗАПРЕТ 10 соответствует выходному сигналу компаратора 4. Поскрльку на выходе элемента И 11 сигнал также отсутствует, на информационный вход триггера 14 поступает выходной сигнал компаратора 4.; Предположим, что в первом такте сигнал, аппроксимирующий входной (на выходе преобразователя 7), меньше входного, тогда сигнал на выходе компаратора 4 разрешает прохождение импульсов генератора 3 через шифратор 6 на вход сложения реверсивного счетчика 5. При этом величина аппроксимирующего напряжения с блока 7 увеличится на единицу дискретности Д причем, если сигнал аппроксимации станет больше входного, то это приведет к срабатыванию компаратора 4. Выходной сигнал компаратора 1 по импульсам с генератора 3 фиксируется в триггере 15, выходной сигнал которого поступает на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16. В результате сигнал на выходе элемента 16 при нулевом состоянии триггера 15 соответствует выходному сигналу триггера 14, а при единичном состоянии - инверсному выходному сигналу триггера 14. Задержка выходного импульса компаратора 4 относительно импульсов тактового генератора 3 определяется временем срабатывания блоков 4-7, 10 и 13. Поэтому элемент 14 задержки согласовывает быстродействие блоков 4,6 и 7 и задерживает тактовые импульсы на время, меньшее времени задержки выходного сигнала компаратора 4. В результате этого в триггере 14 всегда фиксируется выходной сигнал элемента ИЛ И 13, значение которого равно значению сигнала компаратора 4 в момент появления тактового импульса генератора 3. Поэтому триггер 14 выполняет функцию фиксирующей цепи нулевого порядка, и при нулевом выходном сигнале триггера 15 выходной сигнал элемента 16 повторяет значение выходного ригнала компаратора 4.

Аналогично происходит работа дельта-модулятора в последующие интервалы времени. Сигнал элемента 16 повторяет сигнал триггера 14 и формируется с помощью сигнала элемента ИЛИ 13, соответствующего значению прироста сигнала аппроксимации блока 7, причем при монотонном нарастании входного сигнала Uex при KiUBx(t)€(0, UH) на первом выходе 24 дельта-модулятора формируется последовательность, содержащая больше единиц, чем нулей. При монотонном спаде Овх это соотношение меняется на обратное, а в области, где крутизна входного сигнала близка к нулю, число единиц и нулей в выходной последовательности элемента 1б примерно одинаково. На второй выход 25 поступает код, соответствующий знаку входного сигнала, а на третьих выходах 26 дельта-модулятора с помощью блока 20 деления формируется выходной сигнал в формате ИКМ, представленный прямым кодом со знаковым разрядом на выходе 25.

Блок 20 деления преобразует выходной код М - эеверсивного счетчика 5 в ИКМ-код Р на выходах 26 дельта-модулятора по правилу D M/S, где 5€{5мин. Змакс}- нормированное значение сигнала на выходах блока 18 реверсивного (чета, S Ki/Кмакс, Змин Змакс - значения минимального и максимального пределов изменения амплитуды входного сигнала на входах 22 и 23 блока 18 соответственно. ,

При изменении полярности входного сигнала Uex (t) в триггере 15 осуществляetcя запись выходного сигнала компаратора 1. Инвертор 2 формирует с помощью управляющего сигнала компаратора 1 выходнрй сигнал 02 IUBx(t)l. Аппроксимирующий сигнал преобразователя 7 в этом случав осуществляет слежение за сигналом на выходе перемножителя 19, пропорциональным |U№((t)|, как описано, причем на выходе триггера 14 при монотонном нарастании сигнала KtlUexii fO, UH} формируется последовательность, содержащая больше единиц, чем нулей, при монотонном спаде это соотношение меняется на обратное, а в области с низкой крутизной входного сигнала формируется последовательность из чередующихся единиц и нулей. На первом выходе 24 дельта-модулятора при помощи элемента 16 по единичному сигналу триггера 15 соотношение нулей и единиц в указанных последовательностях изменяется на обратное, т.е. при монотонном возрастании lUexCt) (Uex 0), что соответствует монотонному спаду Uex(t), на

первом выходе 24 дельта-модулятора формируется последовательность, содержащая больше нулей, чем единиц. Аналогично при монотонном спаде I UBx(t)l(Uex 0), что соответствует монотонному нарастанию UexW, на первом выходе 24 дельта-модулятора формируется последовательность, содержащая больше единиц, чем нулей,

В конце интервала времени ti по импульсу с делителя 17 частоты блок 18 реверсивного счета увеличивает свое состояние на единицу. Обозначим интервал времени после ЭТОГО; через t2. Соответственно это приводит к увеличению выходного

5 сигнала перемножителя 19 до величины Ui9 K2UBx(t), где Ка - состояние блока 18 (К.2 Kt+1) и увеличению выходного ИКМ-кода на третьих выходах 26 дельта-модулятора, а аппроксимирующий сигнал на выходе

0 преобразователя 7 осуществляет слежение за сигналом Uig в данном интервале времени 12. После нескольких интервалов времени Тк наступает момент времени, когда при слежении за сигналом 19 наступает

5 равенство значений аппроксимирующего

и номинальных напряжений блока 7, т.е.

и UH. Это происходит при наличии во

входном сигнале выброса, что приводит к

полному заполнению реверсивного счетчика 5 импульсами тактового генератора 3, в результате чего на первом выходе шифратора 6 появляется импульс, передний фронт которого через формирователь 8 устанавливает триггер 9 в единичное состояние и

5 одновременно уменьшает состояние блока 18 реверсивного счета на единицу.

Этот же импульс одновременно запрещает прохождение импульсов компаратора 4 через элемент ЗАПРЕТ 10 и разрешает

0 прохождение импульсов триггера 9 через элементы И 11 и ИЛИ 13 на вход триггера 14, в результате чего на выходе последнего, спустя время, равное времени задержки в элементе 12, появляется соответствующий

5 сигнал (1 выходного унитарного кода). До появления импульса на третьем выходе шифратора 6 триггер 9 работал в счетном режиме, изменяя после прихода каждого тактового импульса свое состояние на противоположное. Поэтому, за счет установки триггера 9 в единичное состояние не допускается случайный сбой в выходном коде из-за неправильного фазирования выходных Импульсов триггера 9.

За счет указанного уменьшения состояния блока 18 в дельта-модуляторе производится подстройка (адаптация) значений выбросов выходного сигнала перемножителя 19 к номинальному значению UH. т.е.

ограничение входного сигнала на номинальном уровне от максимального.

Если в следующем периоде дискретизации входного сигнала значение UBx(t) превышает импульс генератора 3, воздействуя на вход триггера 9, изменяет состояние последнего на нулевое. Импульс генератора 3 не изменяет состояние реверсивного счетчика 5, так как шифратор б Ьлокирует прохождение этих импульсов на вход сложения счетчика 5 при полном его заполнении. Поэтому на выходе элемента 16 при выполнении условия Ui9 UH формируется код - чередующаяся последовательность единиц и нулей, соответствующая номинальному значению UH.

Работа дельта-модулятора при последующем уменьшении входного сигнала характеризуется тем, что после прихода очередного тактового импульса генератора 3 импульс с второго выхода шифратора б поступает на вход вычитания реверсивного счетчика 5. При этом аппроксимирующий сигнал и уменьшается на единицу дискретности и становится меньше сигнала Ui9, что приводит к появлению на выходе компаратора 4 положительного потенциала. Импульс с третьего выхода шифратора 6, фиксирующего полное заполнение счетчика 15, принимает нулевое значение, разрешая прохождение импульсов компаратора 4 через элемент ЗАПРЕТ 10 и запрещая прохождение импульсов триггера 9 через элемент И 11. Поэтому на первом, втором и третьих выходах дельта-модулятора появляется , соответствующий знаку приращения и величине входного сигнала. X

Далее работа дельта-модулятора происходит аналогично (при фиксированном состоянии блока 18 реверсивного счета) до MotuieHTa появления импульса на выходе делителя 17 частоты или формирователя 8 импульсов, увеличивая, в первом случае размах выходного сигнала перемножителя 19 при отсутствии во входном сигнале Uex(t) выбросов, или уменьшая, во втором случае, размах выходного сигнала перемножителр 19 при числе выбросов во йходном сигнале UexCt) за период времени Гк. Поэтому в дельта-модуляторе устанавливается динамическое равновесие, по,цдёрживающее значение выбросов входного сигнала, близким к номинальному напряжению, что позволяет независимо от размаха входного сигнала UsxCt) в конкретном интервале времени t2 преобразовать сигнал UaxW в дельта-код с высокой точностью, максимизируя выходное соотношение сигнал - шум.

Блок 18 реверсивного счета работает следующим образом. При отсутствии в входном сигнале выбросов и малой амплитуде входного сигнала происходит непрерывное увеличение состояния реверсивного счетчика 29 (фиг.2) до некоторого максимального значения 8макс, заданного на входах 34 элемента 30 сравнения. При состоянии ревер сивного счетчика 29, равном указанному значению, на выходе элемента 30 сравнения появляется сигнал, запрещающий прохождение импульсов с выхода делителя 17 частоты на вход сложения счётчика 29 через элемент ЗАПРЕТ 27, т.е. предотвращается переполнение счетчика 29 и обеспечивается работа дельта-модулятора в устойчивом режиме адаптации к амплитуде входного сигнала. Аналогично при наличии в входном сигнале значительного числа выбрбсов происходит непрерывное уменьшение состояния реверсивного счетчика 29 импульсами с выхода формирователя 8 импульсов. При уменьшении состояния счетчика 29 до некоторого минимального значения SMHH, заданного на входах 35 элемента 31 сравнения, на выходе последнего появляется сигнал, запрещающий дальнейшее уменьшение состояния счетчика 29 через элемент ЗАПРЕТ 28, т.е. предотвращает обнуление счетчика 29 и обеспечивается работа дельта-модулятора в устойчивом режиме адаптации к амплитуде входного сигнала без учета амплитуды выбросов.

В других режимах работы дельта-модулятора выходной сигнал блока 18 принимает промежуточное значение между минимальным и максимальным значениями Змин, Змакс, заданными на входах 35 и 34 блока 18.

Таким образом, на первом выходе 24 устойчиво работающего дельта-модулятора формируется одноразрядная дельта-последовательность, соответствующая входному аналоговому сигналу, а на втором и третьих выходах 25 и 26 формируется сигнал, соответствующий знаку и модулю входного сигуала дельта-модулятора с точностью до заданного дискрета. Преобразование входного аналогового сигнала в дельтакод осуществляется всегда в режиме максимального сигнала за счет непрерывной адаптации амплитуды выбросов входного сигнала к номинальному значению, что позволяет повысить точность дельтамодулятора и максимизировать выходное соотношение сигнал-шум. Уровень ограничения выбросов может быть изменен изменением коэффициента деления делителя 17 частоты, на время существования которых на дельта-выходе формируется код - чередующаяся из нулей и единиц импульсная последовательность, что соответствует ограничению входного сигнала на номинальном уровне от максимального, а на импульсно-кодовомодулированных выходах - сигнал, соответствующий указанному ограничению. Увеличение томности дельта-модулятора позволяет резко увеличить качественные показатели адаптивных корреляционно-измерительных систем для идентификации образов.

Позтому введение в известное устройство блоков 17-20 с соответствующими связями и соответствующее выполнение блока 18 реверсивного счета позволяет увеличить точность дельта-модулятора и максимизировать выходное соотношэние сигнал шум при преобразовании входного аналогового сигнала с нестационарными выбросами.

Формула изобретения 1. Дельта-модулятор по авт.св. Мг 1448411, отличающийся тем, что, с цепью повышения точности дельта-модулятора, е него введены делитель частоты, блок реверсивного счета, блок деления и перемножитель, подключенный первым входом и выходом между выходом управляемого инвертора и первым входом компаратора, вход делителя частоты подключен к выходу генератора тактовых импульсов, выход делителя частоты соединен с первым входом

блока реверсивного счета, второй вход которого подклк чен к выходу ч|)ормирователя импульсов, а третьи и четвертые входы являются соответственно первыми и вторыми

входами задания пределов входного сигнала, выходы блока реверсивного счета соединены с вторыми входами перемножителя и входами делителя блока деления, входы делимого которого подключены к выходам реверсивного счетчика, выходы блока деления являются третьими выходами дельта-модулятора.

2. Дельта-модулятор поп.1,отличающ и и с я тем, что блок реверсивного счета

содержит реверсивный счетчик, первый и второй элементы сравнения, первый и второй злементы ЗАПРЕТ, разрешающие входы которых являются соответственно первым и вторым входами блока, первые

входы первого и второго элементов сравнения - соответственно третьими и четвертыми входами блока, выходы первого и второго элементов сравнения соединены с запрещающими входам одноименных элементов ЗАПРЕТ, выходы которых соединены соответственно с суммирующим и вычитаюч|| м входами реверсивного счетчика. выхо/рЙ которого подключены к вторым входам эл 4ентов сравнения и являются выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1987 |

|

SU1448411A1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Дельта-модулятор | 1989 |

|

SU1649666A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

| Цифровой фильтр | 1990 |

|

SU1758836A1 |

| Дельта-модулятор | 1986 |

|

SU1345349A2 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

Изобретение относится к автоматике и вычислительной технике. Его использование при построении адаптивных корреляционно-измерительных систем для идентификации образов позволяет повысить точность дельта-модулятора. Последний содержит компаратор 1 знака, управляемый инвертор 2, генератор 3 тактовых импульсов, компаратор 4, реверсивный счетчик 5, шифратор 6, преобразователь 1 код-напряжение,- формирователь 8 импульсов, счетный триггер 9, элемент 10 ЗАПРЕТ, элемент И 11, элемент И 12 задержки, элемент ИЛИ 13, D-триггеры 14, 15 и элемент 16 ИСКЛЮЧАЮЩЕЕ ИЛИ. Положительный эффект обеспечивается благодаря введению делителя 17 частоты, блока 18 реверсивного счета, перемножителя 19 и блока 20 деления. 1 з.п. ф-лы, 2 ил.

| Дельта-модулятор | 1987 |

|

SU1448411A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-01-30—Публикация

1990-03-29—Подача