ся выходами для подключения соответственно к первому и второму модулирующим входам однополосного модулятора с квадратурными каналами устройства.

4. Устройство rio п. 1, отличающееся тем, что, с целью упрощения устройства без увеличения уровня собственных шумов

квантования, между выходом однополосного модулятора с квадратурными каналами и опорным входом фазового детектора включен делитель частоты, причем отношение частотьг задающего генератора к частоте входного сигнала устррйства равно коэффициенту деления делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2581646C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2567002C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2582331C1 |

| ГЛОБАЛЬНО ЛИНЕАРИЗОВАННАЯ СИСТЕМА СИНХРОНИЗАЦИИ | 2014 |

|

RU2554535C1 |

| Устройство фазовой автоподстройки частоты | 1988 |

|

SU1663768A1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2566813C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2595629C1 |

| Тригонометрический функциональный преобразователь | 1978 |

|

SU771683A1 |

| Устройство выделения опорного напряжения из сигнала, манипулированного по фазе | 1975 |

|

SU1338070A1 |

| Устройство для демодуляции фазоманипулированных сигналов | 1983 |

|

SU1184107A1 |

1. УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ, содержащее подстраиваемый генератор, соединенные последовательно фазовый детектрр, опорный вход которого соединен с выходом подстраиваемого генератора, петлевой фильтр и компаратор уровня, реверсивный счетчик, входы управления которого подключены к выходам компаратора уровня, индикатор наличия входного сигнала, выход которого соединен с входом блокировки реверсивного счетчика, и первый цифроаналоговый преобразователь, отличающееся тем, что, с целью увеличения быстродействия путем увеличения интервала времени до появления перескоков фазы после пропадания входного сигнала, подстраиваемый генератор выполнен в виде последовательно соединенных задающего генератора и однопол ос но го модулятор а с квадратурными каналами,между выходами реверсивного счетчика и одним модули- рующим входом однополосного модулятора с квадратурными каналами включены последовательно блок определения синуса и косинуса аргумента 2я-, где ZK (,2,..., N - текущее значение кода реверсивного счетчика; N - емкость реверсивного счетчика, и второй цифроаналоговый преобразователь, а первый цифроаналоговый преобразователь включен между другим выходом блока определения синуса и косинуса аргумента 2я- и другим модулирующим входом однополосного модулятора с квадратурными каналами, между выходом петлевого фильтра и счетным входом реверсивного счетчика включен преобразователь модуля напряжения в частоту, между входом индикатора наличия входного сигнала и сигнальным входом фазового детектора включен переключатель, другой вход которого подключен к общей шине, а управляющий вход подключен к выходу индикатора наличия входного сигнала, второй вход компаратора уровня подключен к общей шине. 2.Устройство по п. 1, отличающееся тем, что блок определения синуса и косинуса аргумента 2л% выполнен в виде постоянного запоминающего устройства (ПЗУ), причем адресные входы и выходы ПЗУ являются входами и выходами блока определения синуса и косинуса аргумента 2л соответственно. I 3.Устройство по п. I, отличающееся тем, что блок определения синуса и косину(Л са аргумента 2л- и первый и второй цифроаналоговый преобразователи выполнены в виде резистивного делителя, вход которого подключен к выходу источника опорного напряжения, выходы соединены с входами первого коммутатора, первый выход которого подключен к первому входу второго и к второму входу третьего коммутаторов, второй О5 выход первого коммутатора подключен к втоа рому входу второго и к первому входу третьего коммутаторов, первый и второй выходы оо второго коммутатора подключены соответственно к первому и второму входам первого дифференциального усилителя, первый и второй выходы третьего коммутатора подключены соответственно к первому и второму входам второго дифференциального усилителя, входы управления второго и третьего коммутаторов объединены и являются входами для подключения к выходам двух старших разрядов реверсивного счетчика устройства, входы управления первого коммутатора являются входами для подключения к выходам остальных разрядов реверсивного счетчика, а выходы первого и второго дифференциальных усилителей являют

1

Изобретение относится к радиотехнике и может быть использовано в составе приемных устройств различного назначения, работающих в условиях запирания сигнала или воздействия организованных помех.

Известно устройство фазовой автоподстройки частоты, содержащее подстраиваемый генератор, фазовый детектор, фильтр нижних частот, в котором на время запирания входного сигнала удерживается напряжение, равное управляющему напряжению в момент начала запирания 1.

Однако при наличии щумов данное устройство не удерживает фазу синхросигнала с достаточной точностью, что приводит к значительному набегу фазовой ощибки за время запирания и к скачкам фазы после окончания запирания.

Наиболее близким к предложенному по технической сущности является устройство фазовой автоподстройки частоты, содержащее подстраиваемый генератор, соединенные последовательно фазовый детектор, опорный вход которого соединен с выходом подстраиваемого генератора, петлевой фильтр и компаратор уровня, реверсивный счетчик, входы управления которого подключены к выходам компаратора уровня, индикатор наличия входного сигнала, выход которого соединен с входом блокировки реверсивного счетчика, и первый цифроаналоговый преобразователь 2.

Однако известное устройство не обеспечивает ликвидации перескоков фазы после пропадания входного сигнала при реальных значениях, тактовых частот и длительностях замираний, т. е. имеет относительно малый интервал времени до появления перескоков фазы после пропадания входного сигнала.

Цель изобретения - увеличение быстродействий путем увеличения интервала времени до появления перескоков фазы после пропадания входного сигнала.

Поставленная цель достигается тем, что в устройстве фазовой автоподстройки частоты, содержащем подстраиваемый генератор, соединенные последовательно фазовый детектор,

опорный вход которого соединен с выходом подстраиваемого генератора, петлевой фильтр и компаратор уровня, реверсивный счетчик, входы управления которого подключены к выходам компаратора уровня, индикатор наличия входного сигнала, выход которого соединен с входом блокировки реверсивного счетчика, и первый цифроаналоговый преобразователь, подстраиваемый генератор выполнен в виде последовательно соединенных задающего генератора и однополосного модулятора с квадратурными каналами, между выходами реверсивного счетчика и одним модулирующим входом однополосного модулятора с квадрратурными каналами включены последовательно блок определения синуса и косинуса аргумента 2л-, где 2к(, ,2,..., N) -текущее значение кода реверсивного счетчика, N - емкость реверсивного счетчика, и второй цифроаналоговый преобразователь, а первый цифроаналоговый преобразователь включен между другим выходом блока определения синуса и косинуса аргумента 2я- и другим модулирующим входом однополосного модулятора с квадратурными каналами, между выходом петлевого фильтра и счетным входом реверсивного счетчика включен преобразователь модуля напряжения в частоту, между входом индикатора наличия входного сигнала и сигнальным входом фазового детектора включен переключатель, другой вход которого подключен к общей щине, а управляющий вход подключен к выходу индикатора наличия входного сигнала, второй вход компаратора уровня подключен к общей щине.

Блок определения синуса и косинуса аргумента 2л-| выполнен в виде постоянного запоминающего устройства (ПЗУ), причем адресные входы и выходы ПЗУ. являются входами и выходами блока определения синуса и косинуса аргумента 2л-| -соответственно.

Блок определения синуса и косинуса аргумента 2л- и первый и второй цифроаналоговые преобразователи выполнены в виде резистивного делителя, вход которого

подключен к выходу источника опорного напряжения, выходы соединены с входами первого коммутатора, первый выход которого подключен к первому входу второго и второму входу третьего коммутаторов, второй выход первого коммутатора подключен к второму входу второго и к первому входу третьего коммутаторов, первый и второй выходы второго коммутатора подключены соответственно к первому и второму входам первого дифференциального усилителя, первый и второй выходы третьего коммутатора подключены соответственно к первому и втому входам второго дифференциального усилителя, входы управления второго и третьего коммутаторов объединены и являются входами для пoдкvlючeния к выходам двух старших разрядов реверсивного счетчика устройства, входы управления первого коммутатора являются входами для подключения к выходам остальных разрядов реверсивного счетчика, а выходы первого и второго дифференциального усилителей являются выходами для подключения соответственно к первому и второму модулирующим входам однополосного модулятора с квадратурными каналами устройства.

С целью упрощения устройства без увеличения уровня собственных шумов квантования между выходом однополюсного модулятора с квадратурными каналами и опорными входом фазового детектора включен делитель частоты, причем отношения частоты задающего генератора к частоте входного сигнала устройства равно коэффициенту деления делителя частоты.

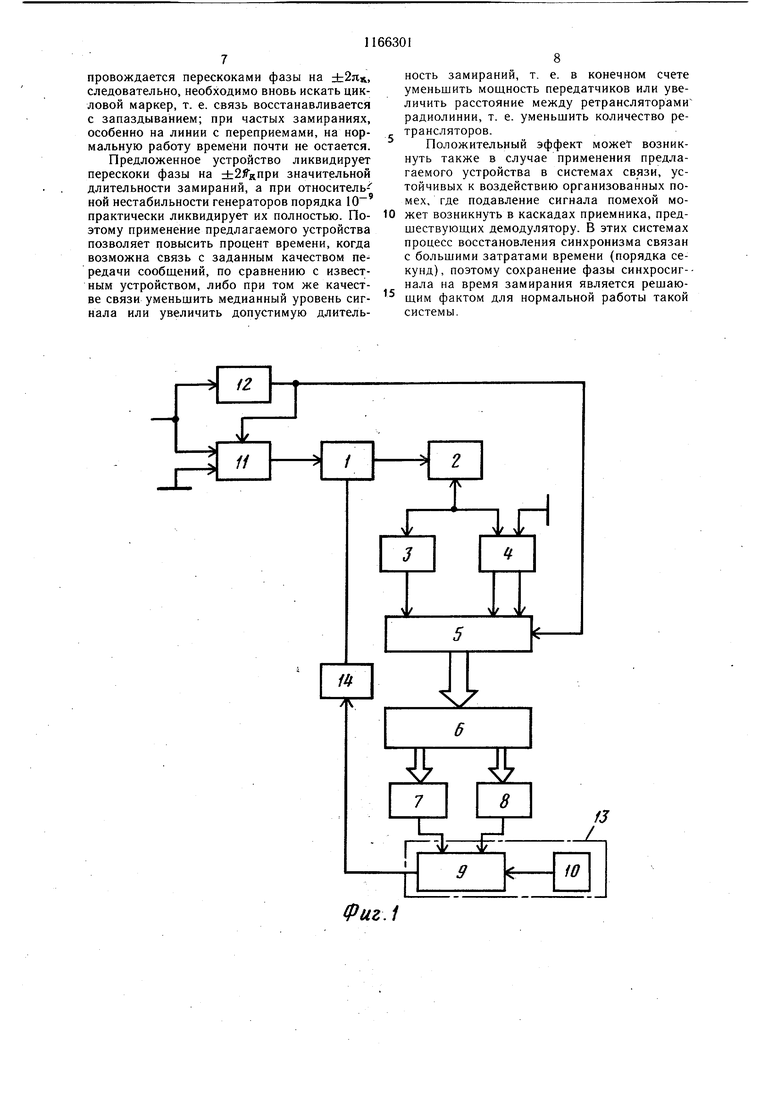

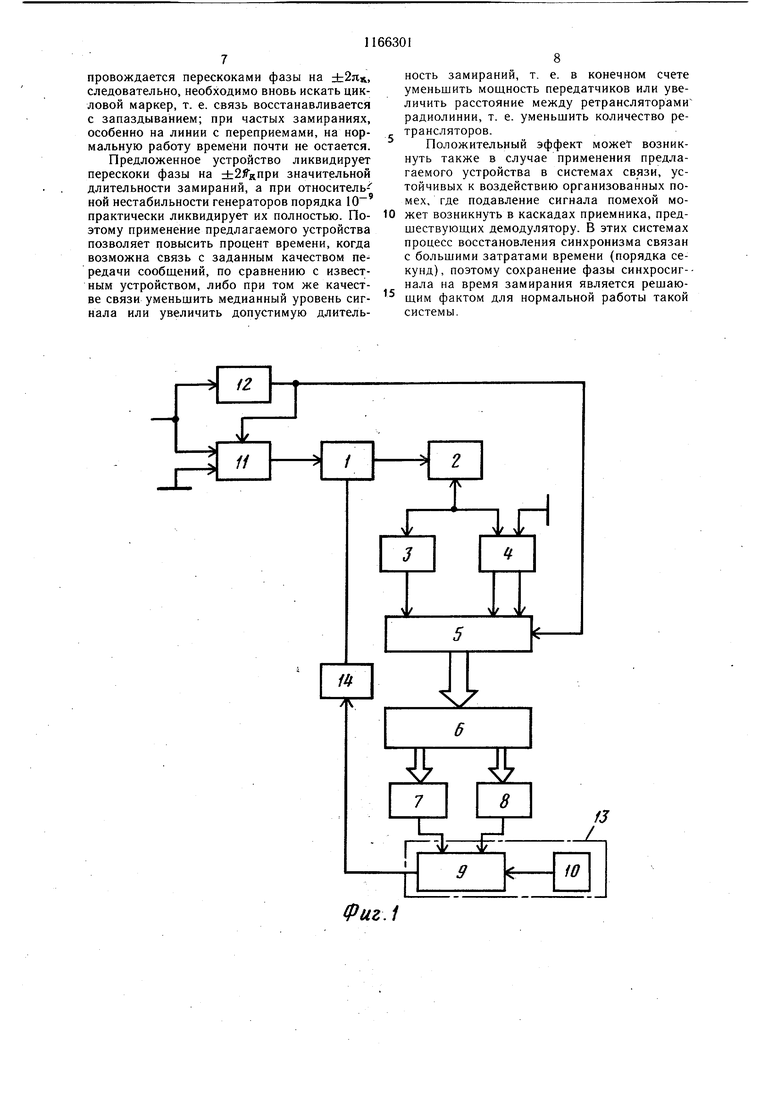

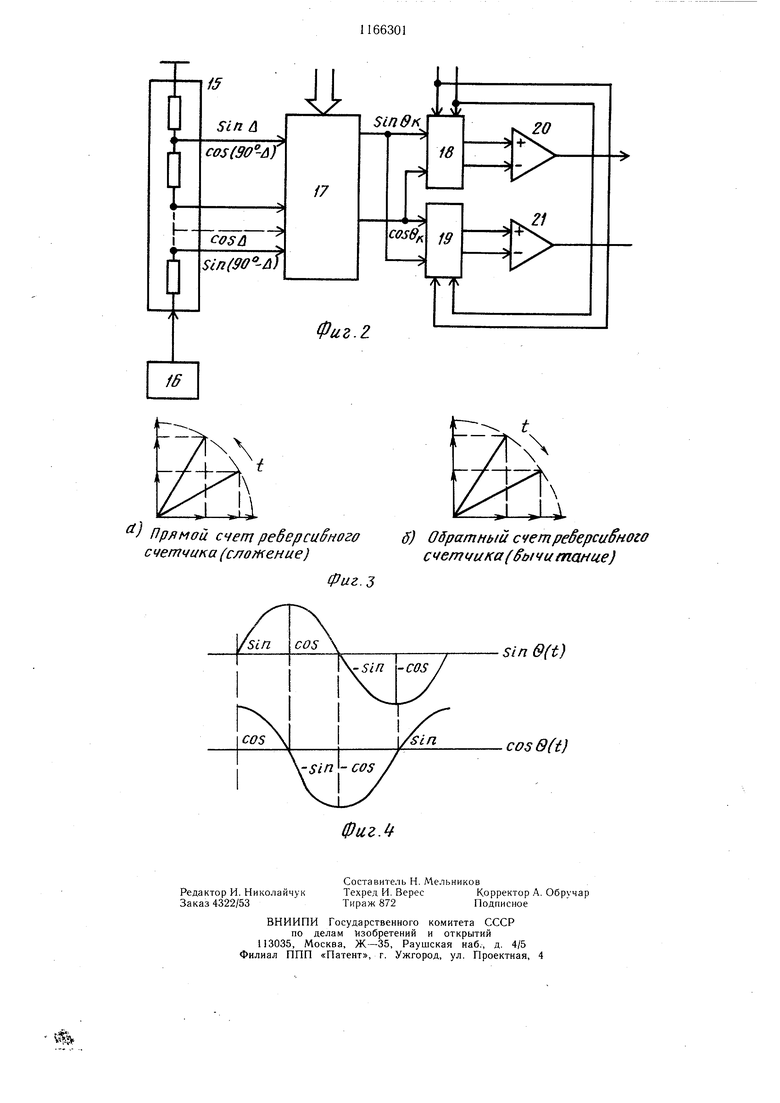

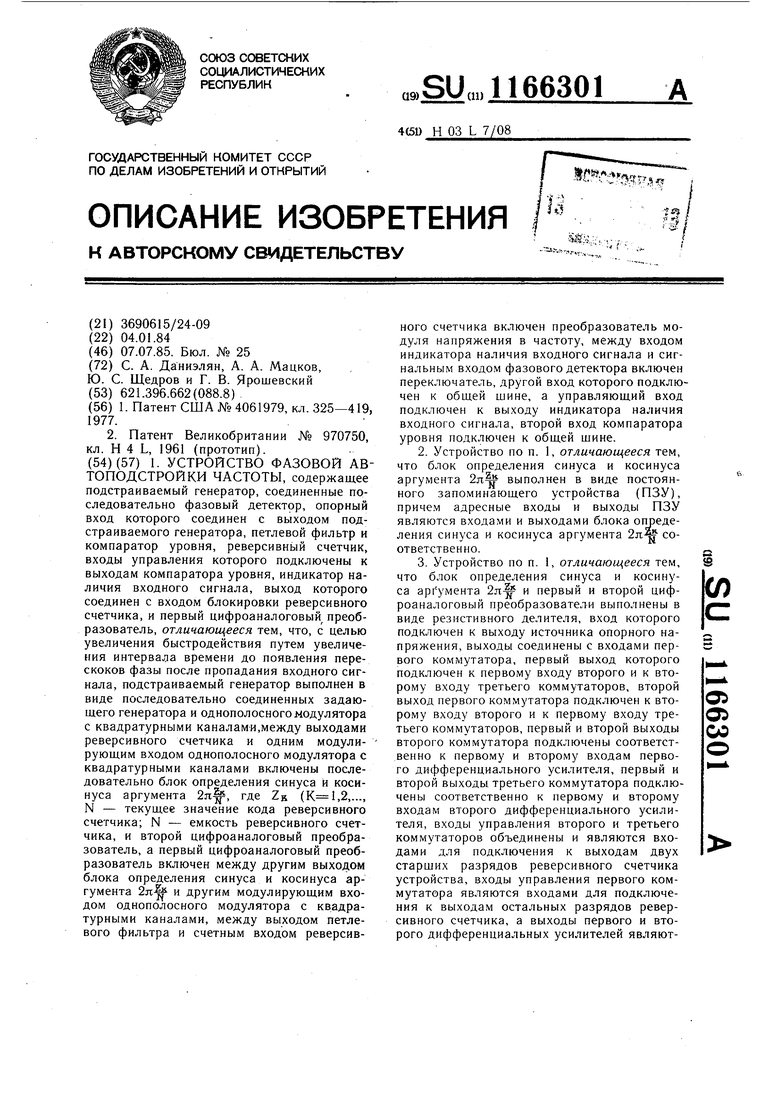

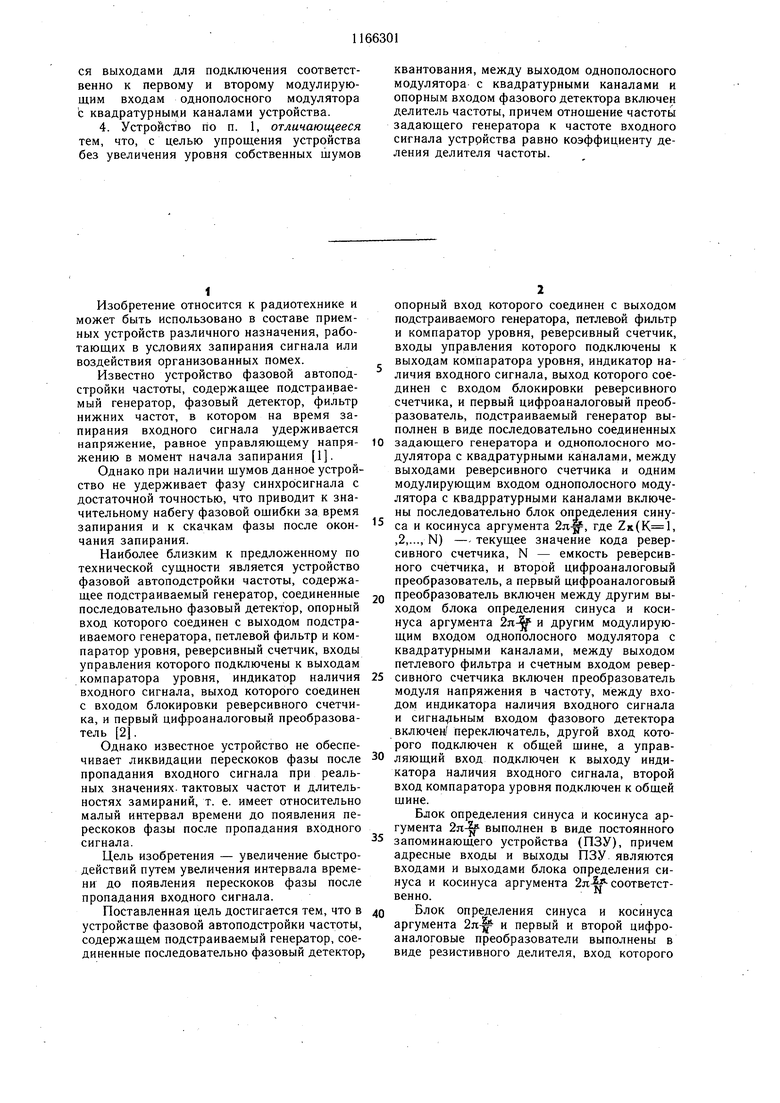

На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 - пример выполнения блока определения синуса и косинуса аргумента 2ли первого и второго цифроаналоговых преобразователей; на фиг. 3 - векторные диаграммы, поясняющие работу предложенного устройства; на фиг. 4 - порядок коммутации второго и третьего коммутаторов.

Устройство фазовой автоподстройки частоты (ФАПЧ) содержит фазовый детектор 1, петлевой фильтр 2, преобразователь 3 модуля напряжения в частоту, компаратор 4 уровня, реверсивный счетчик 5, блок 6 определения синуса и косинуса аргумента 2л-|р, первый 7 и второй 8 цифрроаналоговые преобразовате.ли-, однсиолосный модулятор 9 с квадратурными каналами, задающий генератор 10, переключатель 11, индикатор 12 наличия входного сигнала, подстраиваемый ге ператор 13 и делитель 14 частоты.

Блок 6 опрределения синуса и косинуса аргумента и первый 7 и второй 8 цифроаналоговые преобразователи содержат резистивный делитель 15, источник 16 опорного напрряжения, первый 17, второй 18 и третий 19 коммутаторы, первый 20 и второй 21 дифференциальные усилители.

iTOiicrBO работает следую1цим образом.

K,(i:.ui пег замираний, на выходе индикат()я. 12 отсутствует напряжение, переключо.кмь II соединяет вход устройств-а с сигпу. входо.м фазового детектора 1, а рев(Пси8Н1 |{1 счетчик 5 разблокирован. Тогда, КУК обычно в системах ФАПЧ, напряжение на выходе фазового детектора 1 пропорционально фазовой ошибке системы и содержит также шумовую компоненту. Это напряжение передается петлевым фильтром 2 и подается на выходе преобразователя 3 и компаратора 4 уровня.

И.мпульсы с выхода преобразователя 3 подаются на счетный вход, а с выхода компаратора 4 - на входы управления реверсивного счетчика 5. Таким образом, скорость счета реверсивного счетчика 5 определяется модулем, а направление счета - знаком напряжения на выходе петлевого фильтра 2, т. е. модулем и знаком фазовой ошибки ФАПЧ. Максимальной величине модуля напряжения на выходе пет.чового фильтра 2 соответствует наибольшая частота на выходе преобразователя 3, а нулю напряжения - пулевая частота.

Блок 6 ставит в соответствие кодам ZK на выходе реверсивного счетчика 5 коды Ук- з1п2л- на одном и у со52л-| на другом своих выходах, а первый 7 и второй 8 цифроаналоговые преобразователи преобразуют эти коды в аналоговые напряжения.

Напряжение частотой wo с выхода задающего генератора 10 подается на вход однополосиого модулятора 9, на модулирующие входы которого с первого 7 и второго 8 цифроаналоговых преобразователей подаются напряжения

Улп Asin2.Ti Asin0B.; Ук11 Асо52л- Асо5вк.

Однополосный модулятор выполпен так, что, еслп задающий генераторр 10 дает напряжение sinwot, то на выходе однополосного моду.:1ятора 9 напряжение x(t)a/l sinwot cos(-)K(t) 4-а/1 cos(oi)tsiner t) fisin(o,,t + (-)K(t).

При работе реверсивного счетчика 5 в режиме сложения коды ZR на его выходе и, следовательно, HK последовательно увеличиваются, а при работе в режиме вычитания - уменьшаются. Соответствующие последовательные по времени положения вектора x(t) показаны па фиг. За. б.

Так как скорость счета реверсивного счетчикг: 5 определяется частотой f преобразователя ;). то. обозначая .Ti/N, получаем, пренебрегая эффектами квантованпя по ампл11т -;1е и времени,

eK(t)±qfl; x(4)Bsin(fon±qt)t,

где знак «плюс соответствует режиму сложения реверсивного счетчика 5, а «минус - режим вычитания. Таким образом, частота напряжения на выходе однополосного модулятора 9 пропорциональна модулю и соответствует по знаку напряжению на выходе петлевого фильтра 2, т. е. величине фазовой ошибки ФАПЧ. Следовательно, при отсутствии замираний предлагаемое устройство работает как обычная система ФАПЧ. Пусть напряжение сигнала на выходе устройства упало ниже порогового уровня, т. е. началось замирание. После обнаружения этого индикатором 12 на его выходе появляется напряжение, которое блокирует реверсивный счетчик 5 и перебрасывает переключатель 11, который соединяет сигнальный вход фазового детектора 1 с общей шиной. Тогда напряжение на выходе фазового детектора 1 становится равным нулю, напряжение на выходе петлевого фильтра 2 падает к нулю со скоростью, которая определяется структурой и постоянными времени петлевого фильтра 2, на выходе заблокированного реверсивного счетчика 5 «застывает некоторый код Zxo,соответствующий моменту блокировки to. Поэтому на выходе однополосного модулятора 9 в момент to x(to)Bsin(ooto+eK(t) и, если расстройка по частоте между задающим генератором 10 устройства и генератором передающей станции (не показан) QB(O-0)0, а фазовая ошибка ф(t)фo, то на время замирания фазовая ошибка (p3(t)QH(t-to)+9o, т. е. допустимое время замирания определяется только долговременной нестабильностью частот указанных генераторов. В качестве этих генераторов могут использоваться либо прецизионные кварцевые (о/ 2-10-), либо атомные (() стандарты частоты. При этом время разбега фаз этих генераторов на 180°, когда появляется возможность перескоков фазы на ±2л, составляет величину порядка 0,5Х Х10®-0,5-10 тактов, что даже при тактовых частотах порядка мегагерц дает допустимую длительность замираний от сотен миллисекунд и выше. После окончания замирания индикатор 12 обнаруживает появление напряжения сигнала на своем входе, на его выходе напряжение исчезает, переключатель 1 соединяет вновь сигнальный вход фазового детектора 1 с входом устройства, реверсивный счетчик 5 разблокируется, и устройство начинает сводить к нулю фазовую ошибку, набежавшую за время замирания, как обычная система ФАПЧ. При этом желательно обеспечить апериодический характер переходного процесса, что достигается выбором величины коэффициента демпфирования . Возможно совместное выполнение блока 6 и первого 7 и второго 8 цифроаналоговых преобразователей по схеме фиг. 2. При этом, резистивный делитель 15 подключен, к источнику 16 опорного напряжения. Выходы резистивного делителя 15 соединены с входами первого коммутатора 17, первый выход которого подключен к первому входу второго коммутатора 18 и второму входу третьего коммутатора 19, а второй выход - к второму входу второго коммутатора 18 и к первому входу третьего коммутатора 19. Первый и второй выходы второго коммутатора 18 подключены к первому и второму входам первого дифференциального усилителя 20, а первый и второй выходы третьего коммутатора 19 подключены к первому и второму входам второго дифференциального усилителя 21. Выходы двух старших разрядов реверсивного счетчика 5 соединены с входами управления второго 18 и третьего 19 коммутаторов, а выходы остальных разрядов - с входами управления первого коммутатора 17. Выходы первого 20 и второго 21 дифференциальных усилителей соединяются с модулируюш,ими входами однополосного модулятора 9. Напряжения на выходах резистивного делителя 15 равны отсчетам sin хц от О до 90° (cos XK от 90 до 0°). Порядок коммутации показан на фиг. 4. Количество отсчетов модулирующего сигнала, т. е. разрядность реверсивного счетчика 5, определяется допустимой дискретностью регулирования фазы, т. е. допустимыми собственными шумами квантования. Так, например, если шаг изменения вк желательно иметь порядка 11°, достаточно 32 отсчетов, а шаг регулировки 1,4° требует 256 отсчетов на период. Количество отсчетов может быть уменьшено в М раз, если частоту задающего генератора 10 выбрать равной Mf,, где ft - тактовая частота, а между выходом однополосного модулятора 9 и опорным входом фазового детектора 1 включить делитель 14 частоты с коэффициентом деления М. Разрядность блока 6, очевидно, не может быть меньше разррядности реверсивного счетчика 5. То же справедливо и для первого 7 и второго 8 цифроаналоговых преобразователей. Для улучшения работы предлагаемого устройства желательно, как и в случае обычной ФАПЧ, нормализовать уровень смеси сигнала и шума на его входе с помощью предвключенных каскадов с АРУ или полосового ограничителя. Таким образом, предлагаемое устройство ликвидирует перескоки фазы при больших длительностях замираний, если стабильность задающего генератора 10 высока. Технико-экономический эффект изобретения состоит в следующим. Во время замирания связи нет, поэтому абоненту безразлично, что происходит в это время в устройствах радиолинии. Когда замирание окончилось, в радиолиниях с известным устройством начинается восстановление синхронизации, которое сопровождается перескоками фазы на ±2я&, следовательно, необходимо вновь искать цикловой маркер, т. е. связь восстанавливается с запаздыванием; при частых замираниях, особенно на линии с переприемами, на нормальную работу времени почти не остается. Предложенное устройство ликвидирует перескоки фазы на значительной длительности замираний, а при относительной нестабильности генераторов порядка практически ликвидирует их полностью. Поэтому применение предлагаемого устройства позволяет повысить процент времени, когда возможна связь с заданным качеством передачи сообщений, по сравнению с известным устройством, либо при том же качестве связи уменьшить медианный уровень сигнала или увеличить допустимую длительФиг. 1

ность замираний, т. е. в конечном счете уменьшить мощность передатчиков или увеличить расстояние между ретрансляторами радиолинии, т. е. уменьшить количество ретрансляторов.

Положительный эффект может возникнуть также в случае применения предлагаемого устройства в системах связи, устойчивых к воздействию организованных помех, где подавление сигнала помехой может возникнуть в каскадах приемника, предшествующих демодулятору. В этих системах процесс восстановления синхронизма связан с большими затратами времени (порядка секунд), поэтому сохранение фазы синхросиг-нала на время замирания является решающим фактом для нормальной работы такой системы.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4061979, кл | |||

| Водяной двигатель | 1921 |

|

SU325A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент Великобритании № 970750, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-07-07—Публикация

1984-01-04—Подача