1

Изобретение относится к автоматике и вычислительной технике и предназначено для автоматического контроля электрического монтажа блоков электронной аппаратуры.

Целью изобретения является сокращение аппаратурных затрат.

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - 5 - соответственно функциональные схемы первого формирователя сигналов управления, блока анализа изменения, формирователя циклов, второго формирователя сигналов управления.

Устройство содержит (фиг. 1) коммутаторы I и 2, измеритель 3, блок 4 стимулирующих воздействий, блок 5 ручного управления, счетчик 6, блок 7 сравнения, первый-8 формирователь сигналов управления, генератор 9 тактовых импульсов, блок 10 регистрации.

.2

первьй 11, второй 12, четвертый 13, третий 14 и пятый 15 элементы ИЛИ, элемент 16 задержки, блок 17 анализа измерения, формирователь 18 циклов, дешифратор 19, шифратор 20, второй 21 формирователь сигналов управления и блок 22 памяти, содержащий накопитель 23, элемент 24 задержки и счетчик адреса 25.

Первый 8 формирователь сигналов управления (фиг. 2) содержит элементы 26 - 28 задержки, элементы .И 29- 38, формирователь 39 импульса, элементы ИЛИ 46-45, триггеры 46-50, элемент НЕ 51, входы 52-58 и выходы 59- 62.

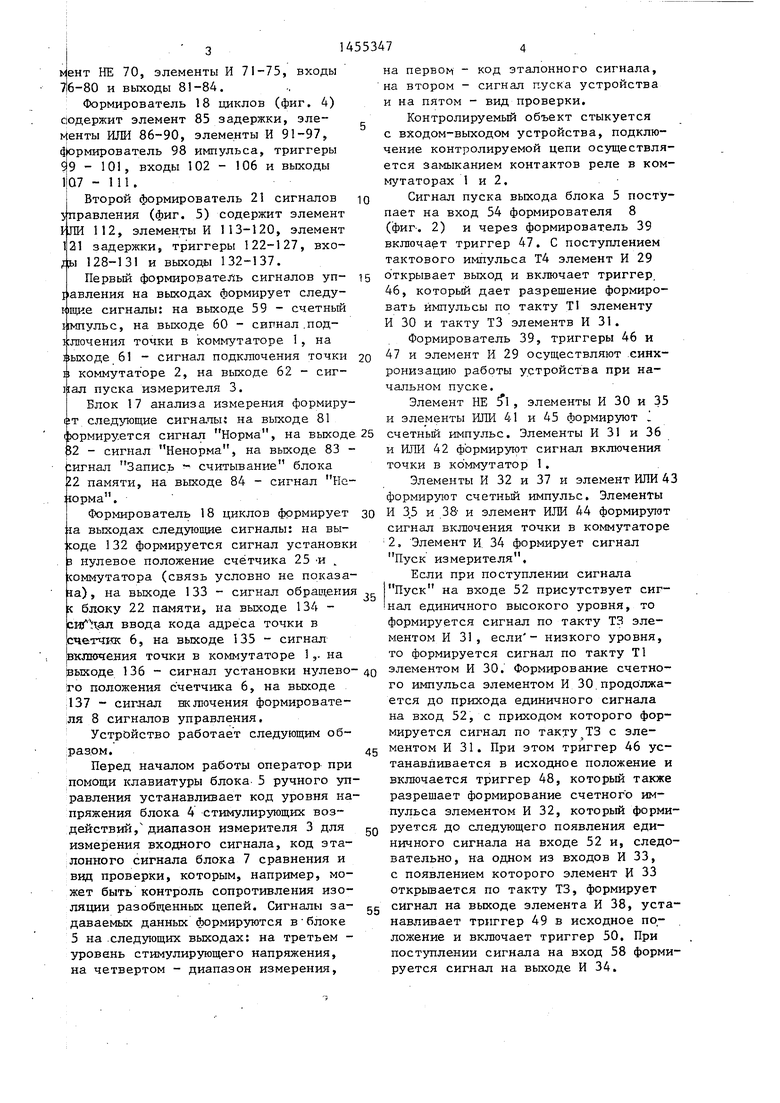

Блок 17 анализа измерения (фиг. 3), содержит элемент 63 задержки, формирователи 64 и 65 импульса, элементы ИЛИ 66 и 67, триггеры 68 и 69, элеi 01 01

00 4ib

М

мент НЕ 70, элементы И 71-75, входы и выходы 81-84.

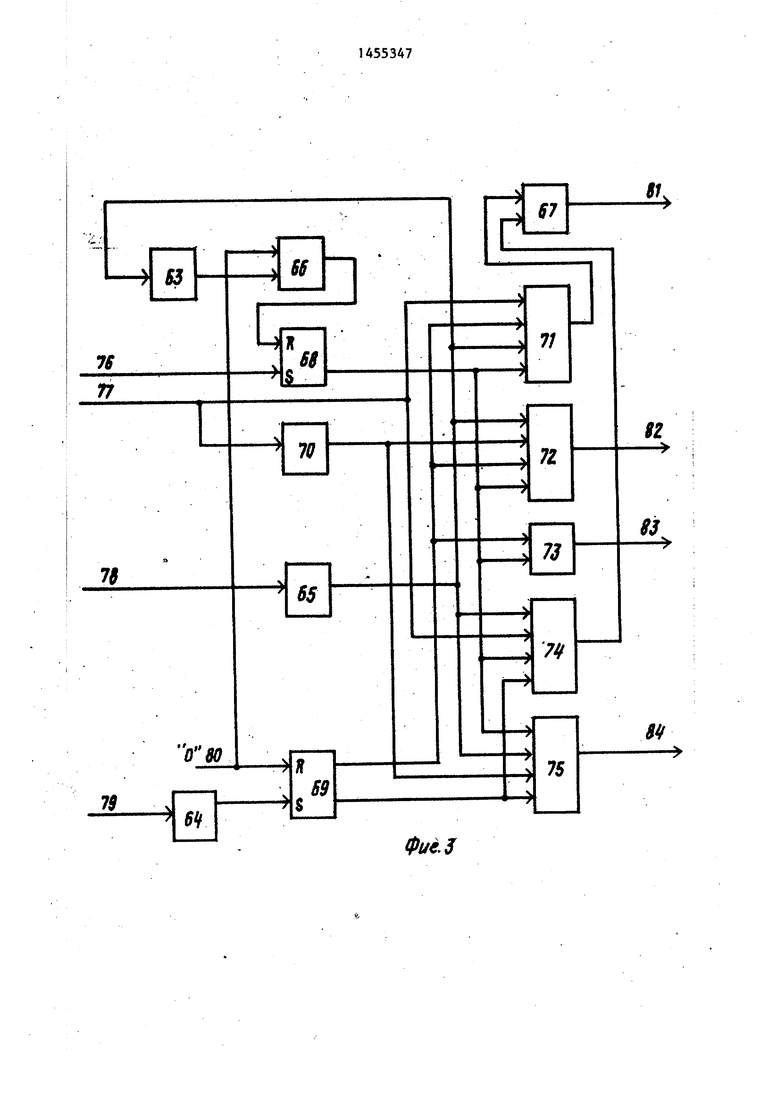

Формирователь 18 циклов (фиг, 4) аодержит элемент 85 задержки, эле- Иенты ИЛИ 86-90, элементы И 91-97, формирователь 98 импульса, триггеры 9 - 101, входы 102 - 106 и выходы 1|07 -111.

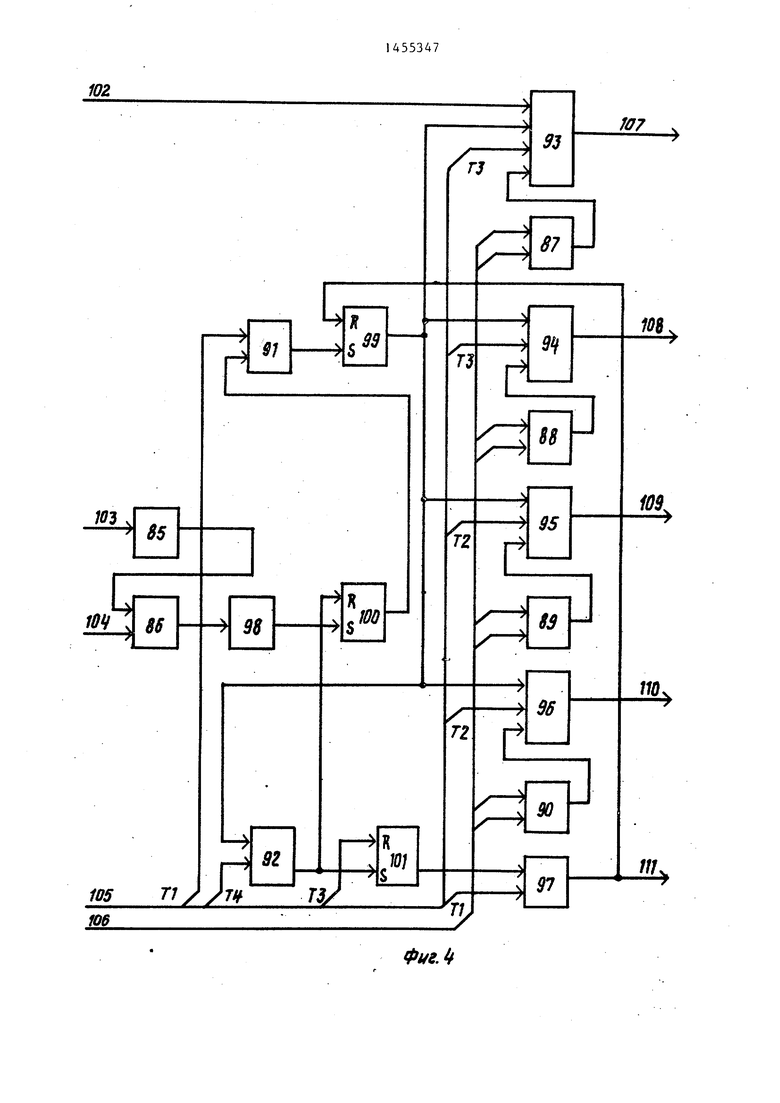

Второй формирователь 21 сигналов фтравления (фиг. 5) содержит элемент I-JM 112, элементы И 113-120, элемент 121 задержки, триггеры 122-127, вхо- 4ы 128-13 и выходы 132-137.

Первьй формирователь сигналов уп- 1|авления на выходах формирует следу- шщие сигналы: на выходе 59 - счетньш 1гмпульс, на выходе 60 - сипнал .под- 1:л1очения точки в коммутаторе 1 , на з(ыходе 6 - сигнал подключения точки и коммутат оре 2, на выходе 62 - сигнал пуска измерителя 3.

Блок 17 анализа измерения формируЭлемент НЕ 1 , элементы И 30 и 35 и элементы ИЛИ 41 и 45 формируют i

следующие сигнаты: на выходе 81

(Ьормиру.ется сигнал Норма, на выходе 25 счетньй импульс. Элементы И 31 и 36

32 - сигнал Ненорма, на выходе 83 - и ИЛИ 42 формируют сигнал включения

:игнап Запись - считывание блока

12 памяти, на выходе 84 - сигнал Нсточки в кбммутатор 1.

Элементы И 32 и 37 и элемент ИЛИ 43 формируют счетньй импульс. Элементы Формирователь 18 циклов формирует ЗО И 3.5 и 38- и элемент ИЛИ 44 формирзпот

:юрма

на первом код эталонного сигнала, на втором - сигнал п-уска устройства и на пятом - вид проверки.

Контролируемый объект стыкуется с входом-выходом устройства, подключение контролируемой цепи осуществляется Замыканием контактов реле в коммутаторах 1 и 2.

Сигнал пуска выхода блока 5 поступает на вход 54 формирователя 8 (фиг-. 2) и через формирователь 39 включает триггер 47. С поступлением тактового импульса Т4 элемент И 29

Открывает выход и включает триггер. 46, который дает разрешение формировать импульсы по такту TI элементу И 30 и такту ТЗ элементв И 31.

Формирователь 39, триггеры 46 и

47 и элемент И 29 осуществляют .синхронизацию работы устройства при начальном пуске.

Элемент НЕ 1 , элементы И 30 и 35 и элементы ИЛИ 41 и 45 формируют i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство для симметрирования токов трехфазных четырехпроводных сетей | 1990 |

|

SU1758773A1 |

| Устройство для анализа ритма сердца | 1986 |

|

SU1553049A1 |

| Устройство для контроля металлизированных переходов печатной платы | 1985 |

|

SU1308955A1 |

| Устройство для контроля межслойных переходов печатной платы | 1980 |

|

SU947793A1 |

| Устройство автоматизированного контроля | 1987 |

|

SU1525680A2 |

Изобретение относится к автоматике и вь1числительной технике и предназначено для автоматического контроля электрического монтажа блоков электронной аппаратуры. Целью изобретения является сокращение аппаратурных затрат устройства. Цель достигается тем, что в устройство, содержа- - щее два коммутатора, измеритель, блок стимулирующих воздействий, блок ручного управления, блок сравнения, блок регистрации, блок памяти, счетчик, три элемента ИЛИ, дещифратор, генератор тактовых импульсов, элемент задержки и два формирователя сигналов управления, введены формирователь циклов, блок анализа измерения, два элемента ИЛИ и шифратор. 2 з.п. ф-лы, 5 ил.

сигнал включения точки в коммутаторе 2, Элемент И 34 формирует сигнал Пуск измерителя.

Если при поступлении сигнала Пуск на входе 52 присутствует сиг1с блоку 22 памяти, на выходе 134 - нал единичного высокого уровня, то ввода кода адреса точки в формируется сигнал по такту ТЗ эле- счетчик 6, на выходе 135 - сигнал ментом И 31, если - низкого уровня, |вкл1(иения точки в коммутаторе 1,- на то формируется сигнал по такту Т1 выходе 136 - сигнал установки нулево-40 элементом И 30. Формирование счетно:ia выходах следующие сигналы: на вы- соде 132 формируется сигнал установки 3 нулевое положение счётчика 25 И . юммутатора (связь условно не показа- яа), на выходе 133 - сигнал обращения

го импульса элементом И 30.продолжается до прихода единичного сигнала на вход 52, с приходом которого формируется сигнал по тактуДЗ с элементом И 31. При этом триггер 46 устанавливается в исходное положение и включается триггер 48, который также разрешает формирование счетного импульса элементом И 32, который формируется до следующего появления единичного сигнала на входе 52 и, следовательно, на одном из входов И 33, с появлением которого элемент И 33 открьшается по такту ТЗ, формирует сигнал на выходе элемента И 38, устанавливает триггер 49 в исходное по- ложение и включает триггер 50. При пост:,Т1лении сигнала на вход 58 формируется сигнал на выходе И 34.

Зго положения счетчика 6, на выходе 137 - сигнал включения формирователя 8 сигналов управления.

Устройство работает следующим об- ;раз.ом.

Перед началом работы оператор при помощи клавиатуры блока- 5 ручного управления устанавливает код уровня напряжения блока 4 стимулирующих воздействий, диапазон измерителя 3 для измерения входного сигнала, код эталонного сигнала блока 7 сравнения и вид проверки, которым, например, может быть контроль сопротивления изоляции разобщенных цепей. Сигналы за- даваемых данных формируются вблоке 5 на .следующих выходах: на третьем - Зфовень стимулирующего напряжения, на четвертом - диапазон измерения.

нал единичного высокого уровня, то формируется сигнал по такту ТЗ эле- ментом И 31, если - низкого уровня, то формируется сигнал по такту Т1 элементом И 30. Формирование счетного импульса элементом И 30.продолжается до прихода единичного сигнала на вход 52, с приходом которого формируется сигнал по тактуДЗ с элементом И 31. При этом триггер 46 устанавливается в исходное положение и включается триггер 48, который также разрешает формирование счетного импульса элементом И 32, который формируется до следующего появления единичного сигнала на входе 52 и, следовательно, на одном из входов И 33, с появлением которого элемент И 33 открьшается по такту ТЗ, формирует сигнал на выходе элемента И 38, устанавливает триггер 49 в исходное по- . ложение и включает триггер 50. При пост:,Т1лении сигнала на вход 58 формируется сигнал на выходе И 34.

Элементы И 35 - 38 управляются выходами элементов ИЛИ 41 - 44, входы которых являются входом 57 вида проверки. Это позволяет при необходимости исключить формирование сигналов на любом выходе 59-62.

В блоке 17 (фиг. 3) в исходном положении триггер 68 на выходе имеет сигнал низкого нулевого уровня, а триггер 69 - на прямом выходе высокий единичный уровень. Сигнал на входе 76 включает триггер 68, который дает разрешение на все элементы И 71хода 111 поступает на вход 56 форми рователя 8 и включает следующий цик контроля.

g В формирователе 21 триггер 122 сигналом Сброс устанавливается по установочному входу в исходное поло жение, при котором на выходе имеет сигнал единичного значения и дает 10 разрешение элементу И 114 сформировать импульс на выходе 132 при поступлении сигнала на вход 128. Триг геры 123-127 устанавливаются в исхо ное положение сигналом сброса (на

75, которые формируют выходные сигна-15 фиг., связь условно не показана).

лы. На вход 77 поступает сигнал результата сравнения кодов. Сигнал высокого уровня формируется, когда измеряемый сигнал находится в пределах нормы, сигнал низкого уровня - когда сигнал измерения не соответствует норме. При поступлении на вход 78 сигнала конца измерения на одном из выходов элементов И 71 и 72 формиру- -ется сигнал Норма или Ненорма. Сигнал на входе 79 включает триггер 69, который закрьшает элементы И 71 и 72 и открьшает элементы И 74 и 75. На выходе элемента И 74 формируетпри этом выходы всех триггеров имею сигнал низкого уровня нулевого знач ния.

Элементы ИЛИ 112 и И 113 и тригге 20 ры 123 и 124 осуществляют синхронизацию по входу 128. При поступлении сигнала на вход 128 элемент И 114 формирует сигнал на выходе 132, вклю чается узел синхронизации и по такту 25 Т1 через элемент И 113 включается

триггер 124, который разрешает форми ровать сигналы по такту Т2 элементу И 115, по такту ТЗ элементу И 116, по такту Т4 элементу И 117. Сигнал

ся сигнал Норма, на выходе элемен- 30 по выходу 135 осуществляет сброс

та И 75 - Ненорма. Сигнал Норма с выходов элементов И 71 и 74 через элемент ИЛИ 67 поступает на выход 81. Элемент И 73 формирует сигнал высокого уровня при положении триггера 69 в исходном положении и соответствует режиму записи.

В формирователе 18 (фиг. 4) элемент 85 задержки, элемент ИЛИ 86, элемент И 91, формирователь 98 импульса осуществляют синхронизацию работы устройства от сигнала по концу измерения: Норма - Ненорма, Сигнал Норма поступает на вход 104, сигнал Ненорма - на вход 103. При поступлении одного из этих сигналов после синхронизации по такту Т1 включается триггер 99 и разрешает формировать управляющие сигналы по такту

триггеров 122 и 123 и включает триггер 125, который дает разрешение формировать импульс по такту Т1 элементу И 118, выход которого является

35 выходом 136. Сигнал с выхода элемента И 118 устанавливает в исходное положение триггер I24 и включает триггер 126, который дает разрешение формировать импульс элементу И 119.

40 При поступлении импульса на вход 131 на выходе элемента И I19 формируется сигнал, который поступает на выход 137.

Триггер 126 сбрасывается в исход45 ное положение сигналом по входу 131 через элемент 121 задержки. Триггер 127 включается сигналом по входу 130 разрешая формировать импульс элементу И 120 по сигналу на входе 131.

ТЗ.элементам И 93 и 94 и по такту Т2 50 Сигнал с выхода элемента И 120 через

элементам И 95 и 96. Формирование сигналов каждого выхода зависит от сигнала, установленного на выходах элементов ИЛИ 87-90, входы которых управляются сигналом с входа 106 и зависит от вида проверки. Работа формирователя 18 заканчивается формированием элементом И 97 по такту Т2 сигнала Конец цикла, которьш с выэлемент ИЛИ 112 включает триггер,123 и после синхронизации осуществляется следукяцее формирование сигналов управления на выходах 133-137. Сигнал 55 на выходе 132 формируется только при наличии сигнала общего сброса устройства.

Сигнал Пуск поступает с выхода блока 5 ручного управления на вход

хода 111 поступает на вход 56 формирователя 8 и включает следующий цикл контроля.

В формирователе 21 триггер 122 сигналом Сброс устанавливается по установочному входу в исходное положение, при котором на выходе имеет сигнал единичного значения и дает разрешение элементу И 114 сформировать импульс на выходе 132 при поступлении сигнала на вход 128. Триггеры 123-127 устанавливаются в исходное положение сигналом сброса (на

фиг., связь условно не показана).

при этом выходы всех триггеров имеют сигнал низкого уровня нулевого значения.

Элементы ИЛИ 112 и И 113 и тригге- ры 123 и 124 осуществляют синхронизацию по входу 128. При поступлении сигнала на вход 128 элемент И 114 формирует сигнал на выходе 132, включается узел синхронизации и по такту Т1 через элемент И 113 включается

триггер 124, который разрешает формировать сигналы по такту Т2 элементу И 115, по такту ТЗ элементу И 116, о такту Т4 элементу И 117. Сигнал

по выходу 135 осуществляет сброс

30 по выходу 135 осуществляет сброс

триггеров 122 и 123 и включает триггер 125, который дает разрешение формировать импульс по такту Т1 эле менту И 118, выход которого является

35 выходом 136. Сигнал с выхода элемента И 118 устанавливает в исходное положение триггер I24 и включает триггер 126, который дает разрешение формировать импульс элементу И 119.

40 При поступлении импульса на вход 131 на выходе элемента И I19 формируется сигнал, который поступает на выход 137.

Триггер 126 сбрасывается в исход45 ное положение сигналом по входу 131 через элемент 121 задержки. Триггер 127 включается сигналом по входу 130, разрешая формировать импульс элементу И 120 по сигналу на входе 131.

50 Сигнал с выхода элемента И 120 через

элемент ИЛИ 112 включает триггер,123, и после синхронизации осуществляется следукяцее формирование сигналов управления на выходах 133-137. Сигнал 55 на выходе 132 формируется только при наличии сигнала общего сброса устройства.

Сигнал Пуск поступает с выхода блока 5 ручного управления на вход

71

54 формирователя 8. При этом на выходе 59 формируется счетньй импульс, а на выходе 60 - сигнал подключения точки в коммутаторе I. .

Формирование счетного импульса ил сигнала подключения точки зависит от уровня сигнала, который поступает на вход 52 с элемента ИЛИ 13..

Низкий (нулевой) уровень сигнала формирует счетньй импульс, а высокий сигнал подключения точки Уровень сигнала управления на выходе элемента ШШ : 13 зависит от состояния выходов дешифратора 19,„вход которого и адресные входы коммутаторов 1 и 2 подключены к выходу счетчика 6, который задает код адреса контролнруемой цепи.

Другой вход дешифратора 19 подклто к выходу шифратора 20. Количество выходов шифратора и номера выходо соответствуют адресу точек задаваемого счетчиком 6. Шифратор 20 может быть представлен как кодирующее устройство для соответствующего, объекта контроля и вьшолнено в виде электрической цепи,:распаянной на разъеме, последняя точка которой подключена к источнику сигнала разрешения. Сигналы разрешения имеются только на тех выходах шифратора 20, номера которых соответствуют номерам Точек объекта контроля, которые подлежат контролю,

При совпадении кода адреса на выходе счетчика 6 и сигнала разрешения на выходе шифратора 6 открывается соответствующий выход дешифратора 19, который разрешает формирование сигнала подключения точки в коммутатора 1 или 2.

При закрытом дешифраторе 19 формируется счетный импульс, который с выхода 59 поступает на счетный вход счетчика 6 и устанавливает следующий адрес.. Смена адреса происходит до появления на выходе дешифратора 19 сигнала разрешения. При этом на выходе 60 формируется сигнал подключения точки, который через элемент ИЛИ 11 поступает на .вход коммутатора 1, а на выходе 59 вновь формируется счетньй импульс, осуществляя поиск следу кнцей контролируемой точки.

При появлении сигнала разрешения на входе 52 формируется сигнал на выходе 61, который дает разрешение подключения точки в коммутаторе 2.

8

Q 5

0

0

45

30

Кроме того, сигнал с выхода 61 поступает на элемент 16 задержки, с выхода которого через вход 58 формирует сигнал пуска измерителя на выходе 57. Время задержки должно обеспечить работу реле в коммутаторах 1 и 2.

Сигнал пуска измерителя поступает на вход измерителя 3 и на вход 76 блока 17 и готовит его к приему сигнала на входе 78 Конец измерения, который поступает с выхода измериае- ля 3.

Измеряемый сигнал с выхода коммутатора 2 постзттает на вход измерителя 3, после измерения преобразуется в код и устанавливается на его информационном выходе, который подключен к входу блока 7 сравнения, на другой вход которого поступает код эталонного сигнала. Результат сравнения в виде сигнала высокого или низкого уровня поступает на вход 77 блока 17, который по сигналу Конец измерения 25 формирует сигнал Норма или Ненорма. Сигнал Норма с выхода 85 поступает на вход 104 формирователя 18 и формирует на выходах 107-110 сигналы Включить (Отключить) точку казвдьй из- которых управляется видом проверки, сигнал которого поступает на вход 106 с выхода блока 5.

Сигнал Ненорма формируется на выходе 82 и поступает на вход пятого элемента ШШ 15 и вход 103 формирователя 18.

На выходе элемента ИЛИ 15 формируется сигнал обращения к блоку 22 памяти, по которому в накопитель 23 записывается начальньй адрес неис- - правностей цепи, который поступает на информационньй вход с счетчика 6.

Кроме того, сигнал с выхода элемента ИЛИ 15 через элемент 24 задержки поступает на счетньй вход счетчи - ка 25, добавляет к текущему адресу единицу для подготовки следующей ячейки накопителя 23 к записи..Сигнал Ненорма, кото.рьй поступает на вход 103 формирователя 18, осуществляет формирование сигналов управления коммутаторами 1 и 2. На выходе 111 сигнал Конец цикла поступает на вход 56 формирователя 8 и включа- g ет следующий цикл работы устройства.

Описанньй режим осуществляет nojfCK цепи с низкой изоляцией групповым методом. При формировании сигнала на втором выходе счетчика 6 происходит

35

0

переключение режима. На этом этапе контроля осуществляется поиск второй точки неисправной цепи. Сигнал конечного адреса, сформированный на втором выходе счетчика 6, переключает в блоке 5 режим и устанавливает следующий вид проверки, в блоке 17 переключает формирование сигнала Ненорма на выход 84, а на выходе 83 устанавливается сигнал, соответствующий режиму чтения в блоке 22 памяти, и по входу 128 включается формирователь 21. При этом на выходе 132 формируется сигнал установки счетчика 25 в нулевое положение, что соответствует адресу первой ячейки накопителя 23.

На выходе 133 формируется сигнал обращения к блоку 22, по которому информация, записанная в первой ячейке, считывается и устанавливается на выходе блока 22 памяти. Сигналом с выхода 134 информация с выхода блока 22 памяти вводится в счетчик 6. На выходе 135 формируется сигнал Включить точку в коммутаторе 1. Кроме того, этот сигнал через элемент ИЛИ 14 включает блок 10 регистрации. По сигналу Конец печати по входу 131 включается формирователь 21 и на выходе 137 формируется сигнал включения формирователя 8. Поиск второй точки в неисправной цепи начинается с пер30 причем вход-выход второго коммутатора соединен с входом-выходом устройства для подключения к входу-выходу объекта контроля, первьй выход счетчика соединен с информационными вхового адреса, для чего счетчик 6 уста- 35 Дами дешифратора, блока памяти и бло- навливается в нулевое положение сигналом Сброс, который формируется на выходе 136 формирователя 21.

Сигнал Ненорма, который формируется на выходе 84, указьшает адрес 40 второй точки неисправной цепи. Адрес фиксируется блоком 10 регистрации. Кроме того, сигнал Ненорма с выхода 84 поступает на вход 130 для под- .. .

готовки приема сигнала Конец печати 45 вторыми входами первого и второго по входу 131, при поступлении которо- элементов ИЛИ, а тактовым входом и го формируются сигналы на выходах 133-137 и работа устройства продолжается до чтения ячейки с нулевой инка регистрации и адресными входами первого и второго коммутаторов, первые управляющие входы которых соединены соответственно с выходами первого и второго элементов ИЛИ., а вторые управляющие входы - соответственно -с первым и вторым выходами формирователя циклов, третьим и четвертым выходами соединенного соответственно с

формацией, которая обеспечивает останов.

Формула изобретения

пятым выходом - соответстве шо с выходом генератора тактовых импульсов и входом начала цикла первого форми- 50 рователя сигналов управления, третий выход которого подключен к входу элемента задержки, а четвертый выход - к входам пуска измерителя и блока анализа измерений, входы конца измепятым выходом - соответстве шо с ходом генератора тактовых импульс и входом начала цикла первого фор 50 рователя сигналов управления, тре выход которого подключен к входу э мента задержки, а четвертый выход к входам пуска измерителя и блока анализа измерений, входы конца изм

рического монтажа, содержащее первьй коммутатор, вход-выход которого является входом-выходом устройства для подключения к входам-выходам объекта

соответственно с вторыми выходами измерителя и счетчика, информа1даон ным входом соединенного с выходом блока памяти, разрешающий вход и

1455347

10

контроля, второй коммутатор, выходом соединенный с информационным входом измерителя, блок стимулирующих воз- действий, блок сравнения, первый и второй информационные входы которого подключены соответственно к первым выходам блока ручного управления и измерителя, первьй и второй формирователи сигналов управления, тактовые входы которых соединены с выходом ге- нератора тактовых импульсов, счетчик, три элемента РШИ, дешифратор, блок памяти, блок регистрации и элемент

задержки, причем первьй, второй и третий выходы первого формирователя сигналов управления подключены соответственно к счетному входу счетчика и первым входам первого и второго

элементов ИЛИ, первый выход второго формирователя сигналов управления соединен с первым вхоцом третьего элемента ИПИ, выходом подключенного к входу пуска блока регистрации,

отличающееся тем, что, с целью сокращения аппаратурных затрат устройства, в него введены блок анализа измерения, формирователь циклов, шифратор и два элемента ИЛИ,

причем вход-выход второго коммутатора соединен с входом-выходом устройства для подключения к входу-выходу объекта контроля, первьй выход счетчика соединен с информационными вхоДами дешифратора, блока памяти и бло-

Дами дешифратора, блока памяти и бло-

.. .

вторыми входами первого и второго элементов ИЛИ, а тактовым входом и

ка регистрации и адресными входами первого и второго коммутаторов, первые управляющие входы которых соединены соответственно с выходами первого и второго элементов ИЛИ., а вторые управляющие входы - соответственно -с первым и вторым выходами формирователя циклов, третьим и четвертым выходами соединенного соответственно с

вторыми входами первого и второго элементов ИЛИ, а тактовым входом и

пятым выходом - соответстве шо с выходом генератора тактовых импульсов и входом начала цикла первого форми- рователя сигналов управления, третий выход которого подключен к входу элемента задержки, а четвертый выход - к входам пуска измерителя и блока анализа измерений, входы конца измеРений и режима которого соединены

соответственно с вторыми выходами измерителя и счетчика, информа1даон- ным входом соединенного с выходом блока памяти, разрешающий вход и

ripynna выходов дешифратора соединены фответственно с выходом шиф1)атора li группой входов четвертого элемента ЦПИ, выходом подключенного к разреша- нщему входу первого формирователя сигналов управления, входы включения, ггуска и строба пуска измерителя которого соединены соответственно с вто- выходами второго формирователя сигналов управления, блока ручного управления и выходом элемента задерж- iM, вход питания nepBoi-o коммутатора соединен через блок стимулирующих поздействий .с третьим выходом блока ; учного управления, вход режима и четвертый выход которого подключены соответственно к второму выходу счет- 1ика и входу настройки измерителя, а пятый выход - к входам В1ада проверки первого формирователя сигналов управления и формирователя циклов, входы режима и первый и второй входы состояния которого подключены соответстрого соединен через формирователь импульса с выходом первого элемента ИЛИ, а вход сброса - с выходом второго элемента И и установочным входом третьего триггера, вход сброса которого подключен к тактовому входу формирователя, второй вход второго элемента И соединен с выходом первого 10 триггера и вторыми входами с третьего по шестой элементов И, выходы которых являются соответственно третьим, четвертым, вторым и первым выходами формирователя, а третьи входы 15 соединены соответственно с выходаьш второго - пятого элементов ИЛИ, входы которых соединены с соответствую ющими разрядами входа вида проверки формирователя, четвертый вход третье- 20 го элемента И является входом режима формирователя, выход третьего триггера соединен с вторым входом седьмого элемента И, выход которого является пятым выходом формирователя и соеди1венно к выходу блока сравнения и пер- 25 ней с входом сброса первого триггера, вому и второму выходам блока анализа первьй и второй входы первого злемеи- измерения, вход состояния и второй и та ИЛИ соединены соответственно с третий выходы которого соединены соответственно с выходом блока сравне30

ния, первым входом пятого элемента ИЛИ и входом режима блока памяти, а четвертый выход - с вторым входом третьего элемента ИЛИ и входом состояния второго формирователя сигналов управления, входы режима и пуска ко- торого подключены соответственно к I выходу блока регистрации и второму ; выходу счетчика, а третий, четвертый, I пятый и шестой выходы - соответствен- но к стробирующему входу и входу 40 сброса счетчика, второму входу пятого элемента ИЛИ и входу сброса блока памяти, входом обращения соединенного с выходом пятого элемента ИЛИ, первый выход второго формирователя дб сигналов управления соединен с третьим входом первого элемента ИЛИ,

первым входом состояния формирователя и через элемент за:держки - с вторым входом состояния формирователя.

первого, второго, четвертого и пято-второго и пятого элементов И, выход

го элементов И и через второй форми-второго элемента ИЛИ соединен с пер- рователь импульса - с входом конца «ькодом блока, второй вход первоизмереиия блока, четвертые входы пер-го элемента ИЛИ и вход сброса второго

вого и четвертого элементов И соеди-триггера соединены с шиной нулевого

йены с входом состояния блока и черезпотенциала.

Stof

Ifut.t

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-30—Публикация

1987-06-10—Подача