мирования- второго счетчика, входом вычитания второго счетчика, входом синхронизации второго счетчика, входом синхронизации второго входного регистра, входом синхронизации первого буферного регистра, входом синхронизации второго буферного регистра и входом синхронизации регистра результата, вторые входы сумматоров по модулю два с второго по п-й (п-раз рядность аргумента) первой и второй групп соединены с выходами соответственно с первого по (п-1)-й тех же групп.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Интерполятор | 1986 |

|

SU1405074A1 |

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Устройство для вычисления сумм парных произведений | 2019 |

|

RU2711731C1 |

| Цифровой Т-генератор функций | 1987 |

|

SU1423999A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММ ПАРНЫХ ПРОИЗВЕДЕНИЙ | 1992 |

|

RU2012041C1 |

УСТРОЙСТВО ИНТЕРПОЛЯЦИИ, содержащее первый и второй счетчики, первый и второй входные регистры, блок памяти, первый буферный регистр и блок управления, выходы первого и второго счетчиков соединены с адресным входом блока памяти, причем блок управления содержит группу элементов И, счетчик адреса, триггер и элемент И, отличающееся тем, что, с целью повышения быстродействия, в него введены второй буферный регистр, две группы сумматоров по модулю два, три коммутатора, матричный умножитель и регистр результата, выход которого соединен с выходом устройства и информационными входами первого и второго буферных регистров, выходы которых соединены с первыми информационными входами соответственно первого и второго коммутаторов, вторые информационные входы которых соединены соответственно с входом логического нуля устройства и выходами сумматоров по модулю два первой группы, выход блока памяти соединен с первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходами сумматоров по модулю два второй группы, выходы первого и второго входных регистров соединены с третьими информационными входами соответственно второго и третьего коммутаторов и первыми входами соответствующих разрядов сумматоров по модулю два соответственно первой н второй групп, вторые входы сумматоров по модулю два соединены с входом логической единицы устройства и четвертым информационным входом третьего коммутатора, информационные входы первых счетчика и входного регистра соединены с входом первого аргумента устройства, вход второго аргумента которого соединен с информационными входами вторых счетчика и входного регистра, выходы с первого по третий коммутаторов соединены с входами соответственно коэффициента первого и второго сомножителей матричного умножиI теля, выход которого соединен с информационным входом регистра результата, причем (Л в блок управления введены узел памяти и генератор импульсов, выход которого соединен с первым входом элемента И, выход которого соединен со счетным входом счетчика адреса и первыми входами элементов И группы, вторые входы которых соединены с выходами соответствующих разрядов первой группы выходов узла памя ти, адресный вход которого соединен с выходом счетчика адреса, вход устаСХ) новки в «О которого соединен с входом установки в «1 триггера и входом запуска о устройства; выход готовности которого соединен с инверсным выходом триггера, прямой выход и вход установки в «О которого соединены соответственно с вторым входом элемента И и выходом старшего разряда второй группы выходов узла памяти, выходы второй группы узла памяти соединены с управляющими входами с первого по третий коммутаторов, выходы с первого по десятый элементов И группы соединены соответственно с входом суммирования первого счетчика, входом синхронизации первого счетчика, входом синхронизации первого входного регистра, входом сум

Изобретение предназначено для использования в качестве аппаратного расширителя в микропроцессорных системах и может найти применение в приборостроении, управляющих и информационно-измерительных системах.

Цель изобретения - повышение быстродействия.

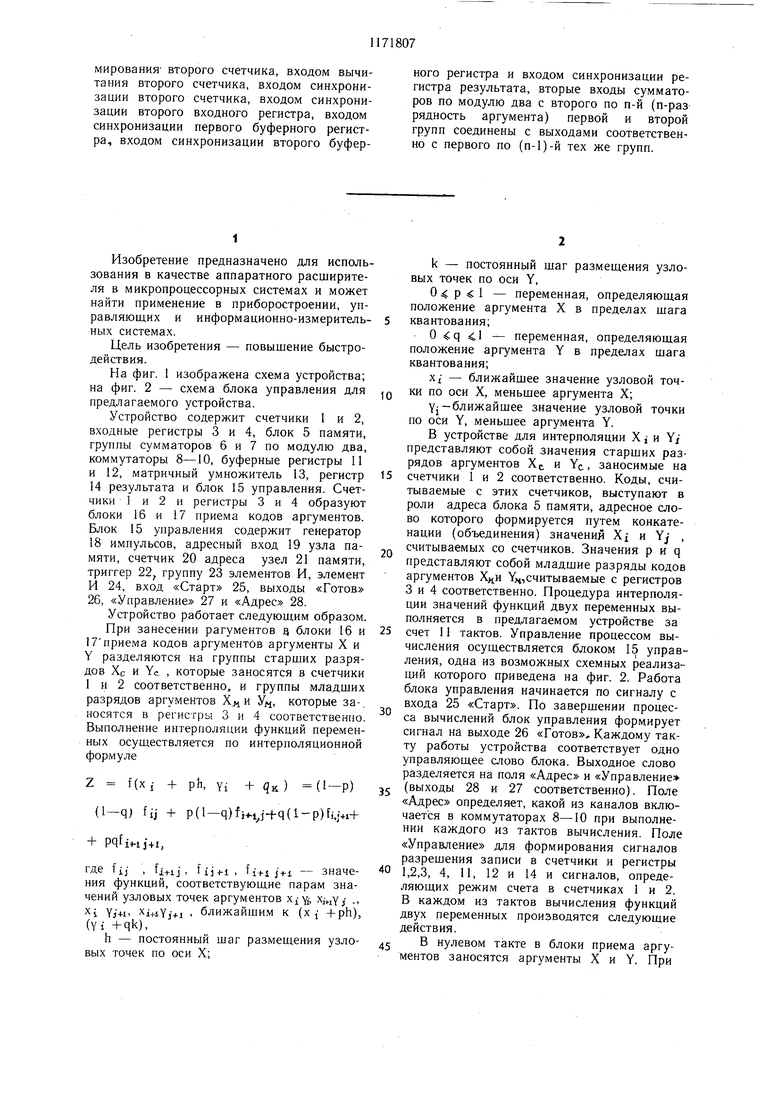

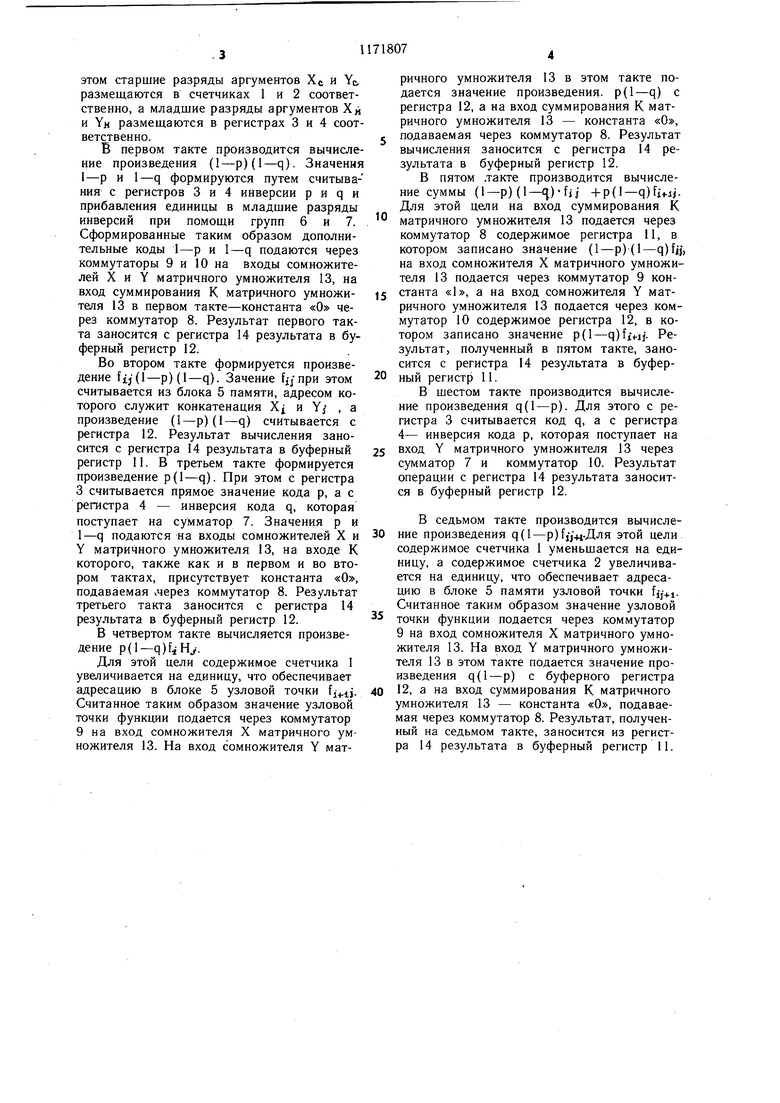

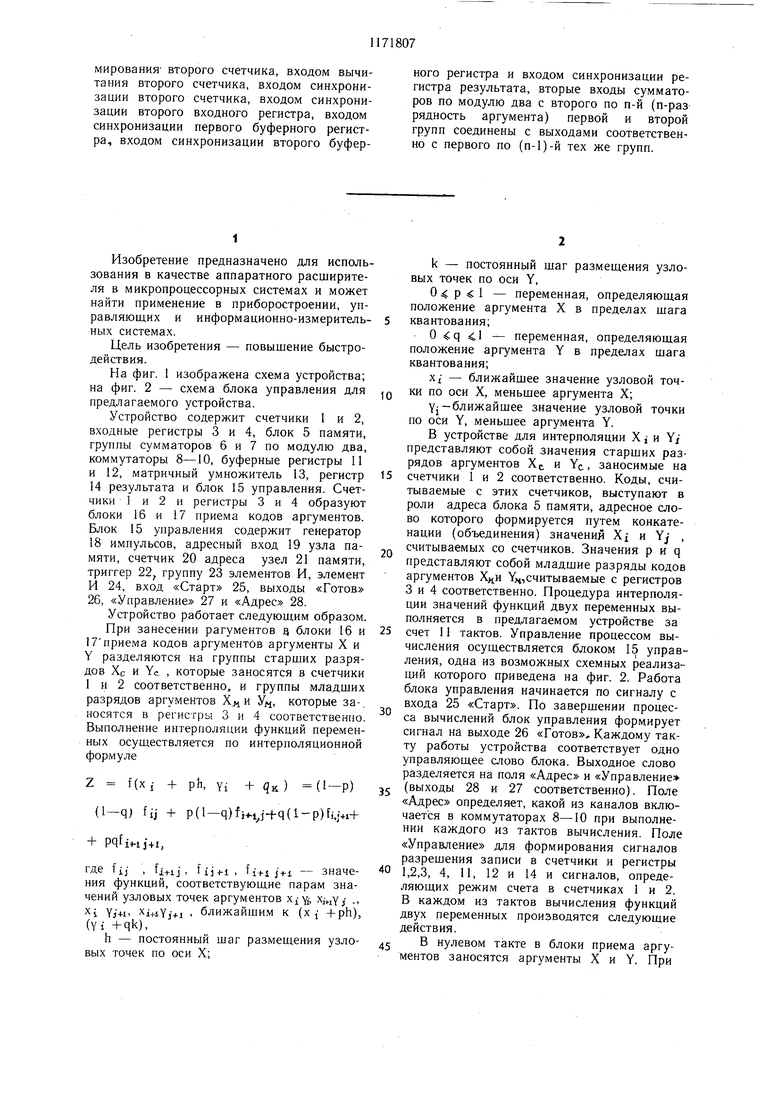

На фиг. 1 изображена схема устройства; на фиг. 2 - схема блока управления для предлагаемого устройства.

Устройство содержит счетчики I и 2, входные регистры 3 и 4, блок 5 памяти, группы сумматоров 6 и 7 по модулю два, коммутаторы 8-10, буферные регистры 11 и 12, матричный умножитель 13, регистр 14 результата и блок 15 управления. Счетчики 1 и 2 и регистры 3 и 4 образуют блоки 16 и 17 приема кодов аргументов. Блок 15 управления содержит генератор 18 импульсов, адресный вход 19 узла памяти, счетчик 20 адреса узел 21 памяти, триггер 22, группу 23 элементов И, элемент И 24, вход «Старт 25, выходы «Готов 26, «Управление 27 и «Адрес 28.

Устройство работает следуюш1им образом.

При занесении рагументов g блоки 16 и 17приема кодов аргументов аргументы X и Y разделяются на группы старших разрядов Хс и Ye , которые заносятся в счетчики I и 2 соответственно, и группы младших разрядов аргументов Х и У, которые за-, носятся в регистры 3 и 4 соответственно. Выполнение интерполяции функций переменных осуществляется по интерполяционной формуле

Z f(x j + рЬ, Yi + к) (1-Р) (1-q) fjj + р(1-q)(l-p)f4+t+ + Pqfmj-n,

где fij , i-i-ij , , fi-fijVi - значения функций, соответствующие парам значений узловых точек аргументов , x,viYj - i Yj+t. xirfYj i ближайшим к (x j +ph),

(Yi +qk)h - постоянный шаг размещения узловых точек по оси X;

k - постоянный шаг размещения узловых точек по оси У,

О р 1 - переменная, определяющая положение аргумента X в пределах шага квантования;

О q 4.1 - переменная, определяющая положение аргумента У в пределах шага квантования;

Xi - ближайшее значение узловой точки по оси X, меньшее аргумента X;

у--ближайшее значение узловой точки по оси У, меньшее аргумента У.

В устройстве для интерполяции Xj и У/ представляют собой значения старших разрядов аргументов Xt и УС , заносимые на 5 счетчики 1 и 2 соответственно. Коды, считываемые с этих счетчиков, выступают в роли адреса блока 5 памяти, адресное слово которого формируется путем конкатенации (объединения) значений Х| и У , считываемых со счетчиков. Значения р и q представляют собой младшие разряды кодов аргументов Ум,считываемые с регистров 3 и 4 соответственно. Процедура интерполяции значений функций двух переменных выполняется в предлагаемом устройстве за 5 счет 11 тактов. Управление процессом вычисления осуществляется блоком 15 управления, одна из возможных схемных реализаций которого приведена на фиг. 2. Работа блока управления начинается по сигналу с входа 25 «Старт. По завершении процесса вычислений блок управления формирует сигнал на выходе 26 «Готов, Каждому такту работы устройства соответствует одно управляющее слово блока. Выходное слово разделяется на поля «Адрес и «Управление 5 (выходы 28 и 27 соответственно). Поле «Адрес определяет, какой из каналов включается в коммутаторах 8-10 при выполнении каждого из тактов вычисления. Поле «Управление для формирования сигналов разрешения записи в счетчики и регистры 0 1,2,3, 4, 11, 12 и 14 и сигналов, определяющих режим счета в счетчиках 1 и 2. В каждом из тактов вычисления функций двух переменных производятся следующие действия.

5 В нулевом такте в блоки приема аргументов заносятся аргументы X и У. При этом старшие разряды аргументов Хс и YC, размещаются в счетчиках 1 и 2 соответственно, а младшие разряды аргументов Х и YK размеш,аются в регистрах 3 и 4 соответственно. Б первом такте производится вычисление произведения (1-р)(1-q). Значения 1-р и 1-q формируются путем считывания с регистров 3 и 4 инверсии р и q и прибавления единицы в младшие разряды инверсий при помоши групп 6 и 7. Сформированные таким образом дополнительные коды 1-р и 1-q подаются через коммутаторы 9 и 10 на входы сомножителей X и Y матричного умножителя 13, на вход суммирования К матричного умножителя 13 в первом такте-константа «О через коммутатор 8. Результат первого такта заносится с регистра 14 результата в буферный регистр 12. Во втором такте формируется произведение ftj(l-р)(1-q). Зачение fj/npH этом считывается из блока 5 памяти, адресом которого служит конкатенация Х и У/ , а произведение (1-р)(1-q) считывается с регистра 12. Результат вычисления заносится с регистра 14 результата в буферный регистр П. В третьем такте формируется произведение р(1-q). При этом с регистра 3 считывается прямое значение кода р, а с регистра 4 - инверсия кода q, которая поступает на сумматор 7. Значения р и 1-q подаются на входы сомножителей X н У матричного умножителя 13, на входе К которого, также как и в первом и во втором тактах, присутствует константа «О, подаваемая хчерез коммутатор 8. Результат третьего такта заносится с регистра 14 результата в буферный регистр 12. В четвертом такте вычисляется произведение р(1-q)f.jH. Для этой цели содержимое счетчика 1 увеличивается на единицу, что обеспечивает адресацию в блоке 5 узловой точки . Считанное таким образом значение узловой точки функции подается через коммутатор 9 на вход сомножителя X матричного умножителя 13. На вход сомножителя У матричного умножителя 13 в этом такте подается значение произведения. р(1-q) с регистра 12, а на вход суммирования К матричного умножителя 13 - константа «О, подаваемая через коммутатор 8. Результат вычисления заносится с регистра 14 результата в буферный регистр 12. В пятом .такте производится вычисление суммы (1-р)(1-)fij +р{1-q)ft -ijДля этой цели на вход суммирования К матричного умножителя 13 подается через коммутатор 8 содержимое регистра 11, в котором записано значение (1-р)(1-q)fij, на вход сомножителя X матричного умножителя 13 подается через коммутатор 9 константа «1, а на вход сомножителя У матричного умножителя 13 подается через коммутатор 10 содержимое регистра 12, в котором записано значение р(1-q)fi4ii. Результат, полученный в пятом такте, заносится с регистра 14 результата в буферный регистр 11. В шестом такте производится вычисление произведения q(l-р). Для этого с регистра 3 считывается код q, а с регистра 4- инверсия кода р, которая поступает на вход У матричного умножителя 13 через сумматор 7 и коммутатор 10. Результат операции с регистра 14 результата заносится в буферный регистр 12. В седьмом такте производится вычисление произведения q(l-p)f5/44-Для этой цели содержимое счетчика 1 уменьшается на единицу, а содержимое счетчика 2 увеличивается на единицу, что обеспечивает адресацию в блоке 5 памяти узловой точки fjj4.j. Считанное таким образом значение узловой точки функции подается через коммутатор 9 на вход сомножителя X матричного умножителя 13. На вход У матричного умножителя 13 в этом такте подается значение произведения q(l-р) с буферного регистра 12, а на вход суммирования К матричного умножителя 13 - константа «О, подаваемая через коммутатор 8. Результат, полученный на седьмом такте, заносится из регистра 14 результата в буферный регистр 11.

| Устройство для аппроксимации функций | 1980 |

|

SU934481A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Интерполятор поверхности | 1980 |

|

SU942040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-07—Публикация

1984-03-20—Подача