Изобретение относится к автоматике и вычислительной технике, предназначено для ввода информации от датчиков импульсных и статических сигналов в системах управления и может быть использовано при построении контроллеров ввода битовой информации в функционально ориентированных микропроцессорных системах обработки информации и управления, проектируемых с учетом следующих основных принципов [1] : программного (микропрограммного) управления; модульного построения; магистрального обмена информацией; наращивания вычислительной мощности.

Обычно такая система содержит модуль ядра системы, образованный схемой синхронизации и начальной установки, микропроцессором (или однокристальной ЭВМ) и комбинированной памятью (ОЗУ+ПЗУ+РПЗУ), модули функционально ориентированных контроллеров и модемов для ввода-вывода информации в процессе взаимодействия системы с внешними объектами (пультом оператора, датчиками событий в объекте управления, исполнительными устройствами, смежными системами и т. п. ), блок питания и системную магистраль для обмена информацией между модулями (конструктивно и функционально законченными составными частями системы) - см., например, [2], [3].

При включении аппаратуры ее составные части приводятся в рабочее состояние (сбрасываются в начальное состояние, тестируются, инициализируются и т. п.) самостоятельно или под управлением ядра системы с помощью контроллера ввода битовой информации, через который в ядро проходит информация о готовности (исправности) внутренних и внешних устройств и битовая информация в виде импульсных и статических сигналов, причем вся или часть битовой информации через данный контроллер может непосредственно вводиться в смежные системы.

К импульсным сигналам относятся те, для которых, по крайней мере, определены их минимальная и максимальная (конечная) длительность, а к статическим - сигналы, которые после установления могут сохранять свое состояние неопределенно долго. Например, после выставления сигналы готовности исправных устройств остаются неизменными до выключения аппаратуры, а нажатие оператором на пульте кнопки вызывает появление сигнала, длительность которого в среднем составляет 40 мс [4].

Импульсные сигналы разных каналов ввода (здесь и далее имеются в виду каналы связи, образованные выходами датчиков сигналов, проводными линиями связи и выходами каналов, являющихся входами устройства для ввода информации) могут существенно отличаться друг от друга по уровню помех и временным параметрам. В этой связи порог обнаружения изменения сигнала для каждого типа датчика обычно подбирается экспериментально и лежит, например, для контактных датчиков в пределах от 5 до 50 [5]. Это обнаружение производится обычно с помощью преобразования временного интервала в код по классическому методу последовательного счета [6].

Поскольку линии связи каналов ввода имеют значительную длину (до десятков и сотен метров), а сигналы разных каналов могут значительно отличаться друг от друга по параметрам, то создание простого высоконадежного контроллера для помехоустойчивого ввода битовой информации в смежные системы и ядро является актуальной технической задачей, так как от качества ввода данной информации зависит качество функционирования аппаратуры в целом.

Решение данной задачи возможно созданием контроллера на основе устройства для ввода информации со структурой, инвариантной к типу системной магистрали. В этой связи в составе контроллера можно выделить генератор импульсов, инвариантное к типу системной магистрали устройство для ввода информации в смежные системы и ядро и устройство управления обменом информацией со смежными системами и ядром, содержащее в общем случае приемопередатчики кодов и сигналов, прерыватель, дешифратор адресного обращения с магистрали, блок памяти для интерпретации информации каналов ввода (для передачи ее во внешние системы и/или в ядро по прерываниям, соответствующим изменениям сигналов состояний датчиков каналов ввода), буферный регистр или стек типа FIFO на несколько вводимых в ядро слов (см., например, [7]). и блок управления для обеспечения взаимосвязанной работы всех составных частей контроллера. В таком контроллере структура устройства управления обменом в значительной степени варьируема и определяется связями со смежными системами и типом системной магистрали (UNIBUS, Q-BUS, IEEE796, ISA, VME и т.п.), а структура устройства для ввода информации практически не зависит от типа системной магистрали и предназначена для обеспечения возможности ввода от каждого канала требуемого количества информации в смежные системы и а ядро с высокой помехоустойчивостью.

Известно, по крайней мере, три типа устройств для ввода информации, причем первый [8 - 11] и второй [12 - 14] типы узкоспециализированы и предназначены для обеспечения помехоустойчивого ввода информации с клавиатуры (механической или сенсорной) и датчиков двоичного кода измеряемой величины (угла, перемещения, температуры и т.п.) соответственно, а устройства третьего типа, предназначенные для ввода информации от датчиков импульсных и потенциальных сигналов, например [15 - 17], имеют ограниченные функциональные возможности, поскольку не обеспечивают помехоустойчивый одновременный ввод информации в смежные системы и в ядро.

Известно устройство [17] , содержащее коммутатор сигналов состояний датчиков каналов ввода, образованный собственно коммутатором и управляемым преобразователем уровня, для обеспечения функционирования от сигналов с четырьмя типами уровней (корпус - разрыв, ТТЛ, 27В - разрыв, КМОП - определены по ГОСТ 18977-79), генератор импульсов, счетчик, два блока памяти, шифратор, согласующий коммутатор, регистр и элемент И.

В процессе функционирования устройство [17] анализирует сигнал каждого канала по трем временным выборкам с программируемой частотой для каждого канала. В этой связи при разрешении прерывания устройство для каждого канала в текущем окне трех выборок может выдать в ядро системы сообщение или о принятии помехи, либо об обнаружении изменения сигнала с порогом, равным "двум".

Поскольку порог обнаружения в устройстве [17] одинаков для всех каналов ввода (равен двум), а каналы, как правило, имеют разные характеристики (см., например, [5]), то устройство [17] в общем случае не сможет обеспечить помехоустойчивый ввод информации в ядро системы от всех каналов.

Из известных технических решений наиболее близким к предлагаемому является устройство для ввода информации [15], содержащее генератор импульсов с двумя выходами (т.е. блок синхронизации), счетчик, коммутатор сигналов состояний датчиков каналов ввода, блоки памяти, управляющие блоками памяти дешифраторы адреса (каждый из них образован двумя дешифраторами, триггером, двумя группами элементов И и счетчиком), и выходы каналов ввода, связанные через коммутатор с информационными входами блоков памяти, вход импульса записи и адресный вход каждого из которых связан через свой управляющий дешифратор адреса соответственно с одним из выходов блока синхронизации и с кодовым адресным входом коммутатора, соединенным с кодовым выходом счетчика, счетный вход которого соединен с другим выходом блока синхронизации.

В процессе функционирования устройства [15] блок синхронизации формирует на своих выходах две не совпадающие во времени последовательности импульсов. По первой последовательности импульсов производится изменение содержимого счетчика и передача через коммутатор на информационные входы всех блоков памяти битового сигнала выбранного канала ввода, а с помощью второй последовательности импульсов происходит запись битовой информации в определенные ячейки блоков памяти согласно выбранным алгоритмам функционирования управляющих дешифраторов адреса.

Таким образом, в устройстве [15] производится циклически во времени перенос битовой информации со всех каналов ввода в соответствующие битовые ячейки блоков памяти.

Если в дальнейшем в аппаратуре использование информации блоков памяти толерантно к кратковременным сбоям (например, эта информация используется для индикации и контроля), то применение простого устройства [15] вполне целесообразно. Однако при потреблении этой информации для управления динамичным технологическим процессом, сбои в переносе информации каналов в блоки памяти могут привести к нежелательным (непредсказуемым) последствиям, т.е. в подобных ситуациях использование устройства [15] практически становится неприемлемым.

Следовательно, устройство [15] имеет ограниченную область использования, что обусловлено его низкой помехоустойчивостью, поскольку процессы изменения информации в каналах ввода асинхронны процессам ее переноса в блоки памяти.

Предлагаемым изобретением решается задача расширения области использования устройства и обеспечение его помехоустойчивости комплексно как за счет выставления максимального из допустимых порога обнаружения изменения сигнала состояния датчика для каждого канала ввода, так и с помощью автоматического устранения сбоев при хранении текущих результатов функционирования устройства.

Для достижения этого технического результата в устройство для ввода информации, содержащее блок памяти, счетчик, коммутатор сигналов состоянии датчиков каналов ввода, блок синхронизации и выходы каналов ввода, являющиеся информационными входами коммутатора, кодовый адресный вход которого соединен с кодовым выходом счетчика, счетный вход которого соединен с первым выходом блока синхронизации, введены дополнительный блок памяти, дополнительный счетчик, четыре элемента И-НЕ, компаратор, блок управления, тактовый вход, соединенный с тактовым входом блока синхронизации, вход сброса, соединенный с входами сброса счетчика и блоков синхронизации и управления, адресный кодовый выход номера канала ввода, первые импульсный и информационный выходы соответственно импульса записи и бита фильтрованного состояния датчика канала для ввода в смежные системы, вторые импульсный и информационный выходы соответственно импульса обнаружения изменения состояния и бита состояния датчика канала для ввода в ядро, и выход сигнала готовности, причем кодовый выход счетчика соединен дополнительно с адресным кодовым выходом номера канала ввода устройства, с адресным кодовым входом блока памяти и с входами младших разрядов адреса дополнительного блока памяти, входы старших разрядов адреса которого соединены с дополнительным кодовым выходом счетчика, являющимся старшим его кодовым выходом, кодовый выход дополнительного блока памяти соединен с первым информационным входом компаратора, второй информационный вход компаратора соединен с информационным входом дополнительного счетчика и с кодовым информационным выходом блока памяти, кодовый вход которого соединен с кодовым выходом дополнительного счетчика, выход коммутатора соединен с первым входом первого элемента И-НЕ, выход которого соединен с первыми входами второго и третьего элементов И-НЕ, первый выход блока синхронизации дополнительно соединен со стробирующим входом выбора блока памяти и с вторыми входами первого и второго элементов И-НЕ, первый информационный вход блока управления соединен с выходом третьего элемента И-НЕ и с первым входом четвертого элемента И-НЕ, второй вход которого соединен с выходом второго элемента И-НЕ, а выход соединен с вторым входом третьего элемента И-НЕ, битовый информационный выход блока памяти соединен с вторым информационным входом блока управления, третий информационный вход которого соединен с выходом компаратора, битовый выход дополнительного блока памяти соединен с управляющим входом блока управления, первый импульсный вход которого соединен выходом переполнения счетчика, счетный вход дополнительного счетчика соединен с вторым выходом блока синхронизации, третий и четвертый выходы которого соединены соответственно с входами стробов чтения и передачи данных для записи блока памяти, пятый и шестой выходы блока синхронизации соединены соответственно с вторым и с третьим импульсными входами блока управления, первый и второй импульсные выходы которого соединены соответственно с входами сброса и установки дополнительного счетчика, вход импульса записи блока памяти соединен с первым импульсным выходом устройства и с третьим импульсным выходом блока управления, четвертый импульсный выход которого является вторым импульсным выходом устройства, битовый информационный вход блока памяти соединен с первыми информационными выходами блока управления и устройства, вторым информационным выходом устройства является второй информационный выход блока управления, третий информационный выход которого является выходом сигнала готовности устройства.

Авторам не известны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение дополнительного блока памяти, дополнительного счетчика, четырех элементов И-НЕ, компаратора, блока управления, снабженного восемью входами (сброса, тремя информационными, одним управляющим и тремя импульсными) и семью выходами (четырьмя импульсными и тремя информационными), тактового входа, входа сброса, адресного кодового выхода номера канала ввода, первых импульсного и информационного выходов импульса записи и бита фильтрованного состояния датчика для ввода в смежные системы, являющиеся соответственно третьим импульсным и первым информационным выходами блока управления, вторых импульсного и информационного выходов импульса обнаружения изменения состояния и бита этого состояния датчика канала для ввода в ядро системы, являющихся соответственно четвертым импульсным и вторым информационным выходами блока управления и выхода сигнала готовности устройства, являющегося третьим информационным выходом блока управления) предлагаемого устройства, позволяющих ему комплексно обеспечить помехоустойчивый ввод информации в смежные системы и/или в ядро системы.

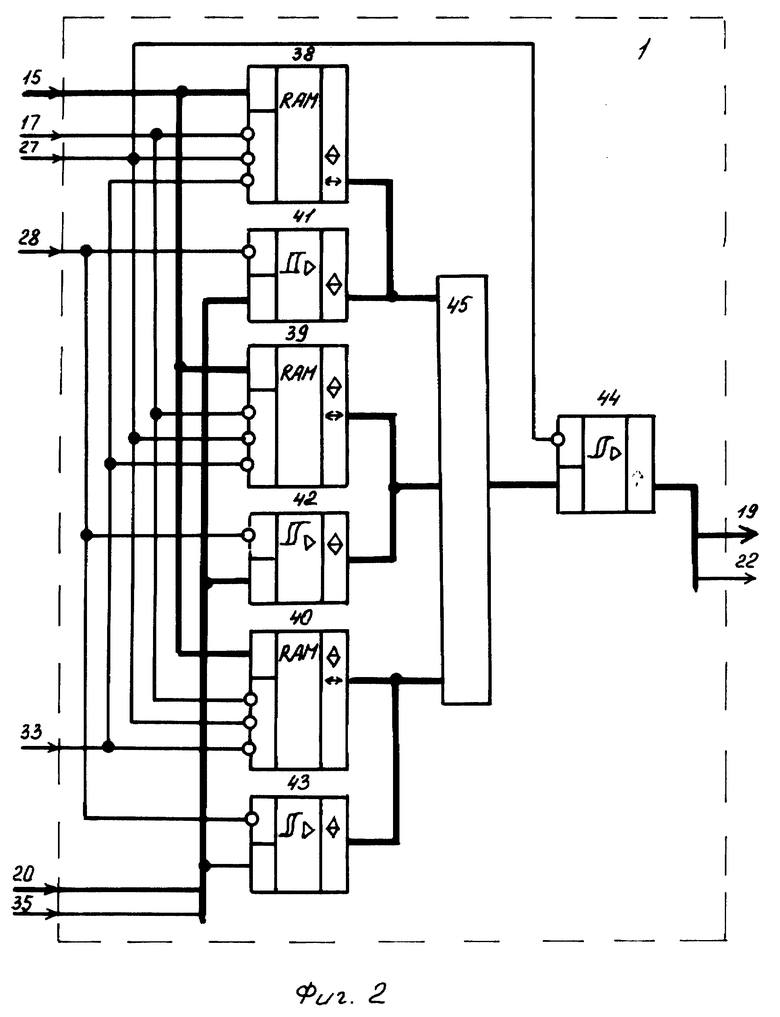

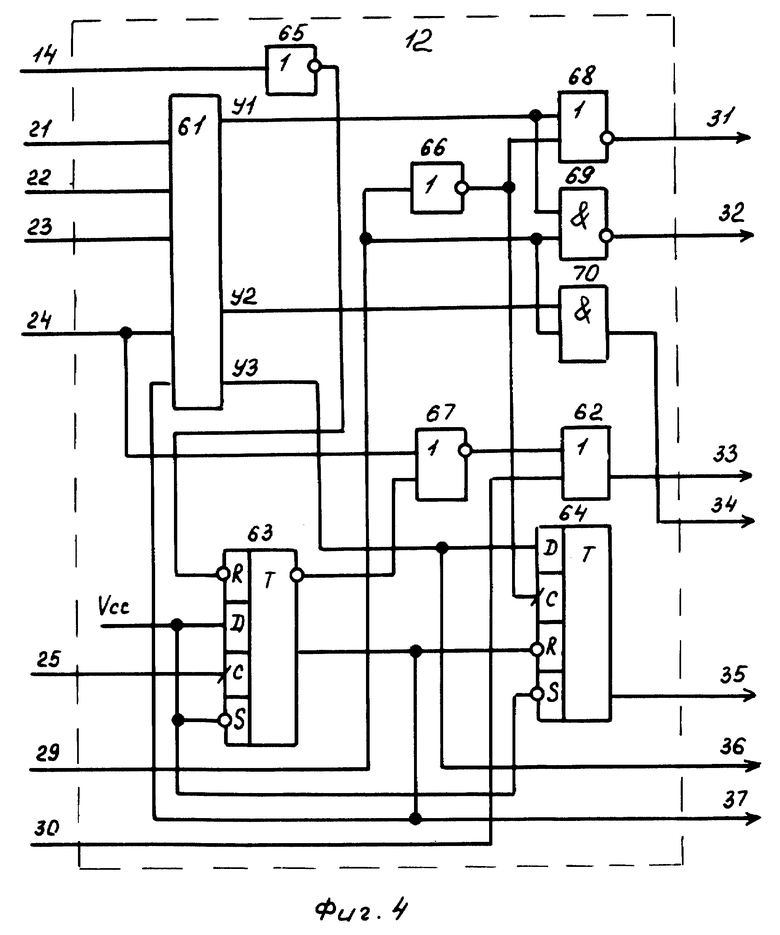

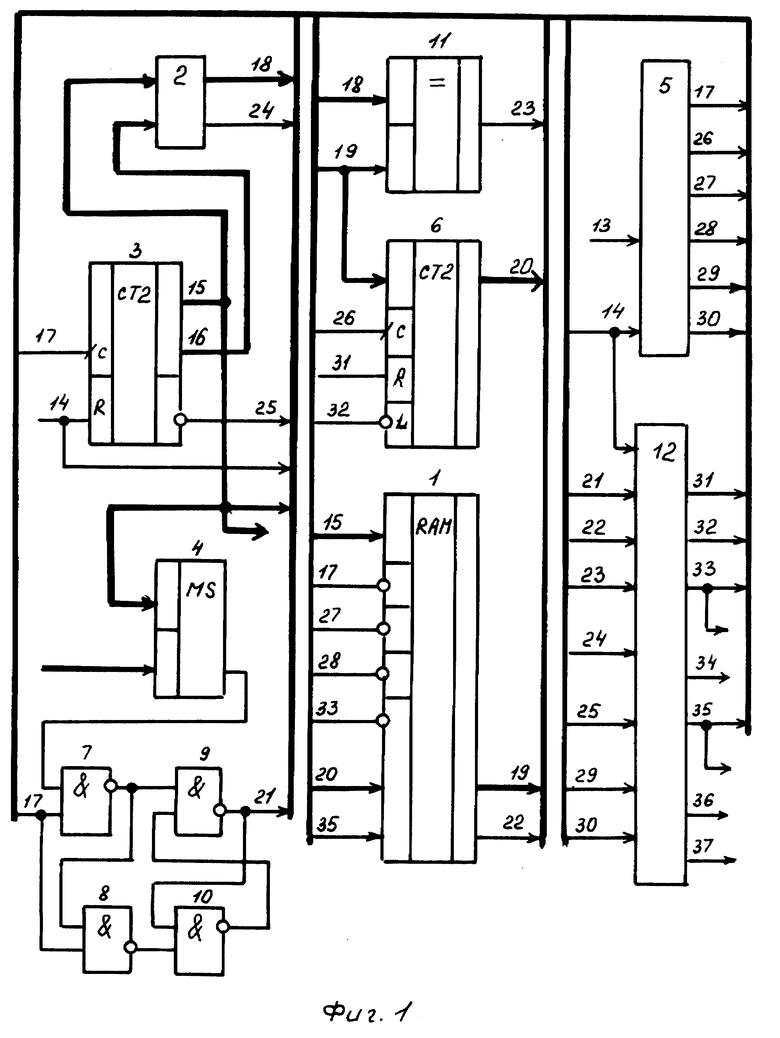

На фиг. 1 - 4 приведена функциональная схема устройства для ввода информации при реализации его, в частности, для 64-х каналов ввода на элементной базе интегральных схем (ИС) серии 1533, ИС программируемой памяти, например, 541 РТ1, 541 РТ2 (или 556РТ4, 556РТ7) и ИС оперативной памяти, например, 537РУ9А: на фиг.5 приведены временные диаграммы, поясняющие работу устройства в процессе функционирования во времени.

Устройство для ввода информации (фиг. 1) содержит блок 1 памяти, дополнительный блок 2 памяти, счетчик 3, коммутатор 4 сигналов состояний датчиков каналов ввода, блок 5 синхронизации, дополнительный счетчик 6, первый 7, второй 8, третий 9 и четвертый 10 элементы И-НЕ, компаратор 11, блок 12 управления, тактовый вход 13, соединенный с тактовым входом блока 5, вход 14 сброса, соединенный со входами сброса счетчика 3 и блоков 5 и 12, адресный кодовый выход номера канала ввода, соединенный с кодовым входом 15 счетчика 3, с адресными кодовыми входами блока 1 памяти и коммутатора 4 и с входами младших разрядов адреса блока 2 памяти, входы старших разрядов адреса которого соединены с дополнительным кодовым выходом 16 счетчика 3, являющегося его старшим кодовым выходом, выходы каналов ввода, являющиеся информационными входами коммутатора 4, выход которого соединен с первым входом первого элемента И-НЕ 7, выход которого соединен с первыми входами второго 8 и третьего 9 элементов И-НЕ, первый выход 17 блока 5 соединен с стробирующим входом выбора блока 1 памяти, со счетным входом счетчика 3 и с вторыми входами первого 7 и второго 8 элементов И-НЕ, кодовый выход 18 блока 2 памяти соединен с первым информационным входом компаратора 11, второй информационный вход которого соединен с информационным входом дополнительного счетчика 6 и с информационным кодовым выходом 19 блока 1 памяти, информационный кодовый вход которого соединен с информационным выходом 20 дополнительного счетчика 6, первый информационный вход блока 12 соединен с выходом 21 третьего элемента И-НЕ 9 и с первым входом четвертого элемента И-НЕ 10, второй вход которого соединен с выходом второго элемента И-НЕ 8, а выход - с вторым входом третьего элемента И-НЕ 9, информационный битовый выход 22 блока 1 памяти соединен с вторым информационным входом блока 12 управления, третий информационный вход которого соединен с выходом 23 компаратора 11, битовый выход 24 блока 2 памяти соединен с управляющим входом блока 12, первый импульсный вход которого соединен с выходом 25 переполнения счетчика 3, счетный вход дополнительного счетчика 6 соединен с вторым выходом 26 блока 5,третий 27 и четвертый 28 выходы которого соединены соответственно с входами стробов чтения и передачи данных для записи блока 1 памяти, пятый 29 и шестой 30 выходы блока 5 соединены соответственно с вторым и с третьим импульсными входами блока 12, первый 31 и второй 32 импульсные выходы которого соединены соответственно с входами сброса и установки дополнительного счетчика 6, вход импульса записи блока 1 памяти соединен с третьим импульсным выходом 33 блока 12, являющимся первым импульсным выходом устройства, вторым импульсным выходом которого является четвертый импульсный выход 34 блока 12, информационный битовый вход блока 1 памяти соединен с первым информационным выходом 35 блока 12, являющимся первым информационным выходом устройства, вторым информационным выходом которого является второй информационный выход 36 блока 12, третий информационный выход 37 которого является выходом сигнала готовности устройства.

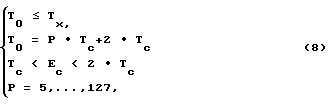

Для автоматического устранения сбоев при хранении текущих результатов функционирования устройства блок 1 памяти (фиг. 2) выполнен как оперативное запоминающее устройство с мажоритарным резервированием, используемое обычно /18/ в высоконадежных вычислительных управляющих системах, и содержит первый, второй и третий оперативные запоминающие элементы 38, 39 и 40 (каждый из них выполнен на основе ИС 537РУ9А), первый, второй, третий и четвертый управляемые буферные передатчики 41, 42, 43 и 44 (каждый из них выполнен в виде ИС 1533АП5), группу 45 из восьми мажоритарных элементов (реализована на трех ИС 1533АП3), адресный кодовый вход 15, соединенный с адресными входами элементов 38 - 40, стробирующий вход 17 выбора, соединенный с входами выбора элементов 38 - 40, вход 27 строба чтения, соединенный c входами разрешения выходов элементов 38-40 и передатчика 44, вход 28 строба передачи данных для записи, соединенный с входами разрешения выходов передатчиков 41-43, вход 33 импульса записи, соединенный с входами управления записью информации в элементы 38-40, информационный байтовый вход, образованный кодовым и битовым входами 20 и 35 соответственно и связанный через передатчики 41, 42 и 43 соответственно с информационными входами-выходами элементов 38, 39 и 40, соединенными соответственно с первым, вторым и третьим информационными кодовыми входами группы 45 мажоритарных элементов, информационный выход которой связан через передатчик 44 с информационным байтовым выходом блока 1 памяти, образованным кодовым и битовым выходами 19 и 22 соответственно.

Блок 2 памяти можно реализовать, например, на одной ИС 541 РТ2 (или 556РТ7). Счетчики 3 и 6 могут быть выполнены на трех и двух ИС 1533 ИЕ7 соответственно. Коммутатор 4 при функционировании от сигналов одного ТТЛ уровня может быть выполнен на основе девяти ИС 1533 КП15, а для обеспечения работы устройства по сигналам нескольких типов уровней, определенных, например, по ГОСТ 18977-79, в качестве коммутатора следует использовать его техническую реализацию, примененную в /17/ и дополненную блоком памяти (одной ИС 541РТ1 или 556РТ4) для формирования по коду адреса адреса 3-разрядного кода управления преобразователем уровней.

Компаратор 11 может быть выполнен на основе двух ИС 1533СП1.

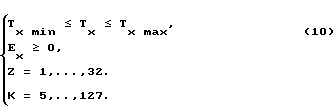

Блок 5 синхронизации (фиг.3) реализован на ИС серии 1533 для работы по импульсам тактовой частоты 8192 кГц на входе 13 и содержит счетчик 46, пять элементов И-НЕ 47-51, элемент НЕ 52, три элемента ИЛИ-НЕ 53-55, два элемента ИЛИ 56 и 57 и три программных контакта 58-60, причем тактовый вход 13 и вход 14 сброса блока 5 соединены со счетным и сбросовым входами счетчика 46 соответственно, первый выход 17 соединен с выходом первого элемента И-НЕ 47, с первыми входами элементов ИЛИ-НЕ 53-55 и с первым входом первого элемента ИЛИ 56, второй выход 26 соединен с выходом второго элемента И-НЕ 48 и с первым входом третьего элемента И-НЕ 49, третий выход 27 соединен с выходом первого элемента ИЛИ 56, четвертый выход 28 соединен с выходом третьего элемента И-НЕ 49 и с первым входом второго элемента ИЛИ 57, выход нулевого (младшего) разряда счетчика 46 соединен с вторым входом первого элемента ИЛИ-НЕ 53 и с первым входом четвертого элемента И-НЕ 50, второй вход которого соединен с выходом первого разряда счетчика 46 и с третьим входом первого элемента ИЛИ-НЕ 53, выход которого соединен с первым входом второго элемента И-НЕ 48, выход второго разряда счетчика 46 соединен с вторыми входами элементов 48, 54, 56, с первым входом пятого элемента И-НЕ 51 и с входом элемента НЕ 52, выход которого соединен с вторым входом третьего элемента ИЛИ-НЕ 55, выходы третьего и четвертого разрядов счетчика 46 соединены с первым и вторым входами первого элемента И-НЕ 47, третий вход которого соединен с контактом 58, который соединен пайкой или с контактом 59, соединенным с выходом пятого разряда счетчика 46 либо с контактом 60, соединенным с шиной логической "1" (например, шиной цепи питания +5В), выход четвертого элемента И-НЕ 50 соединен с третьим входом второго элемента ИЛИ-НЕ 54 и с вторым входом пятого элемента И-НЕ 51, выход которого соединен с вторым входом второго элемента ИЛИ 57, второй вход третьего элемента И-НЕ 49 соединен с выходом третьего элемента ИЛИ-НЕ 55, выходы вторых элементов ИЛИ-НЕ 54 и ИЛИ 57 являются соответственно пятым 29 и шестым 30 выходами блока 5.

Возможный вариант реализации блока 12 управления (фиг.4) содержит формирователь 61 логических функций, выполненный, например, на одной ИС 541 РТ1 (или 556РТ4), элемент ИЛИ 62, триггеры 63 и 64, элементы НЕ 65 и 66, элементы ИЛИ_ НЕ 67 и 68, элемент И-НЕ 69 и элемент И 70, причем вход 14 сброса через элемент НЕ 65 соединен с входом сброса триггера 63, информационный и установочный входы которого соединены с установочным входом триггера 64 и с шиной логической "1", первый 21, второй 22 и третий 23 информационные входы блока 12 соединены с входами первых трех аргументов формирователя 61, вход четвертого аргумента которого соединен с первым входом элемента 67 и с управляющим входом 24 блока 12, первый выход формирователя 61 соединен с первыми входами элементов 68 и 69, выходы которых являются первым и вторым импульсными выходами 31 и 32 блока 12, первый импульсный вход 25 которого соединен с тактовым входом триггера 63, инверсный выход триггера 63 соединен с вторым входом элемента 67, второй выход формирователя 61 соединен с первым входом элемента 70, второй импульсный вход 29 блока 12 соединен с входом элемента 66 и с вторыми входами элементов 69 и 70, выход элемента 66 соединен с вторым входом элемента 68 и с тактовым входом триггера 64, выход элемента 67 соединен с первым входом элемента 62, второй вход которого соединен с третьим импульсным входом 30 блока 12, третьим и четвертым импульсными выходами 33 и 34 которого являются выходы элементов 62 и 70 соответственно, прямой выход триггера 64 является первым информационным выходом 35 блока 12, второй информационный выход 36 которого соединен с третьим выходом формирователя 61 и с информационным входом триггера 64, вход сброса которого соединен с входом пятого аргумента формирователя 61 и с прямым выходом триггера 63, являющимся третьим информационным выходом 37 блока 12.

Описание работы устройства ведется с помощью системы положений и обозначений, сформулированных в следующих пунктах.

1. Используется модифицированный язык описания Булевых (логических) функций - ABEL, в котором операторы "Конъюнкции", "Дизъюнкции", "Инверсии" и "ИСКЛЮЧАЮЩЕЕ ИЛИ" имеют обозначения "& ", "#". "!" и "$" соответственно. Например, y= !X1$!X2 означает операцию ИСКЛЮЧАЮЩЕЕ ИЛИ над двумя инверсными переменными.

2. Коды адреса на выходах 15 и 16 счетчика 3 обозначим через K15A= A0A1A2A3A4A5 и K16A= A6A7A8A9A10 соответственно, где A0 младший, а A10 старший биты 11-разрядного счетчика 3.

3. На выходах 18, 19 и 20 соответствующих составных частей устройства формируемые семиразрядные коды данных обозначим через K18D, K19D и K20D соответственно.

4. Формируемые на выходах соответствующих составных частей устройства битовые сигналы обозначим с помощью букв "x" и "y" (например, X21-бит выборки состояния датчика обрабатываемого канала ввода, формируемый на выходе 21 элемента 9 И-НЕ; y3=x36 - функция, формируемая на третьем выходе формирователя 61, являющемся вторым информационным выходом 36 блока 12), а импульсные с помощью записей "C... или !C...", например, прямой C29 и инверсный ! C26 синхросигналы, вырабатываются соответственно на выходах 29 и 26 блока 5 согласно фиг. 5.

5. Под фронтом или спадом любого сигнала (прямого или инверсного) понимается смена логического уровня этого сигнала с "0" в "1" или с "1" в "0" соответственно - см. фиг.5.

6. Под сигналом (прямым или инверсным) понимается появление на временной оси "единичного" значения этого сигнала. Например, появление и снятие сигнала !C17 означает, что на соответствующих участках временной оси t!C17=0 и ! C17=1 соответственно - см. фиг.5.

С учетом принятой системы положений и обозначений опишем сначала назначение и функционирование отдельных составных частей устройства, а затем его работу в целом с помощью временных диаграмм фиг.5.

Блок 1 памяти с используемой емкостью 64 байта предназначен для хранения битовых фильтрованных сигналов состояний X22 датчиков всех каналов и текущих кодов K19D многоканального преобразования временных интервалов сигналов состояний датчиков всех каналов в код по методу последовательного счета. Функционирование блока 1 (фиг. 2) организовано по сигналам !C17 выбора, !C27 строба чтения, !C28 строба передачи данных для записи и импульсу !C33 записи так, что в процессе его функционирования можно выделить три режима: хранение при ! C17=1: чтение по адресу K15A информации "K19D и X22" при !C17=!C27=0; запись по адресу K15A информации "K20D и X35" при !C17=!C28=0 по импульсу ! C33 записи.

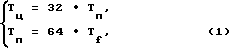

Одиннадцатиразрядный счетчик 3 предназначен для формирования импульсов ! C25 переполнения, кода K15A=A0A1A2A3A4A5 (где A0 - младший бит кода) адреса (номера) канала ввода и текущего кода K18A=A5A7A8A9A10 номера обработки каналов ввода в течение цикла Tц:

где Tf - период частоты следования импульсов !C17;

Tn - длительность прохода адресов всех каналов ввода.

В процессе функционирования счетчик 3 по сигналу C14 фиксируется в состоянии "0. ..0", при отсутствии сигнала C14 содержимое счетчика 3 увеличивается на единицу младшего разряда по каждому фронту сигнала !C17. При переполнении счетчик 3 формирует сигнал !C25, совпадающий на временной оси с одним из импульсов !C17.

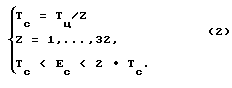

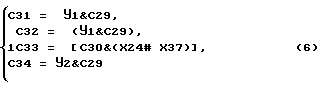

Блок 2 памяти, емкостью 2048 байт, предназначен для формирования по кодам K15A и K1SA для каждого канала ввода кода K1SD числового порога "P" обнаружения изменения сигнала состояния датчика канала ввода и управляющего битового сигнала X24, с помощью которого осуществляется преобразование в код длительности сигнала состояния датчика канала ввода по методу последовательного счета с максимальной ошибкой Ec и временным квантом Tc, оцениваемым согласно выражениям

В этой связи с помощью управляющего бита X24 каждый канал ввода в течение Tц может быть опрошен от одного до 32 раз так, что для соответствующих каналов ввода при Z=32 бит X24=1 независимо от значения кода K16A, а при Z= 1. ..,31 бит X24=1 только при определенных значениях кода K1SA. Это основано на том, что при работе счетчика 3 по фронтам сигнала !C17 в течение Tц биты A6, A7, A8, A9 и A10 переходят из "0" в "1" в разное время 16, 8, 4, 2 и 1 раз соответственно. Поэтому при Z < 32 блок 2 формирует для каждого канала ввода бит X24=1 в течение цикла равномерно (32 делится на Z без остатка) или квазиравномерно (32 делится на Z с остатком) Z раз как сумму состояний переходов из "0" в "1" соответствующих битов кода K1SA. Например, для конкретного канала ввода при Z=31 бит X24=1 при всех значениях кода K16A, кроме значения K16A = 11111, а при Z=17 сигнал X24=1 при K16A= 0XXXX (т.е. IS раз, где X - означает "0" или "1" в соответствующих битах кода K1SA) и при K16A= 11110 (т.е. всего один раз).

Коммутатор 4 предназначен для выбора в течение !C17=1 сигнала состояния датчика канала ввода по коду K15A адреса (номера) канала ввода.

Элементы И-НЕ 7-10 функционируют как триггер-защелка, с которого в течение !C17=0 снимается бит X21 выборки анализируемого сигнала состояния датчика, выбранного коммутатором 4 в течение !C17=1.

Дополнительный семиразрядный счетчик 6 предназначен для формирования в течение !C17=0 по импульсам C31 (или !C32) и !C26 текущего результата преобразования длительности сигнала состояния датчика канала ввода в код K20D с помощью кода K190. Это осуществляется при !C17=0 так, что сначала формируется импульс C31 (или ! C32) сброса в "0...0" (или установки в состояние K20D= K19D) счетчика 6. После этого на счетчик 6 поступает счетный импульс ! C26, по фронту которого содержимое счетчика 6 увеличивается на единицу младшего разряда и далее при X24=1 записывается в блок 1 памяти по импульсу ! C33.

Компаратор 11 постоянно сравнивает коды K18D и K19D и формирует бит X23 согласно выражениям

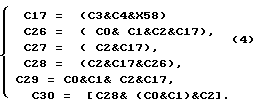

Блок 5 синхронизации по сигналу C14 сбрасывается, а при C14=0 по тактовым импульсам ! C13 частоты 8192 КГц формирует шесть регулярных последовательностей импульсов !C17, !C26, !C27, !C28, !C29 и !C30 с частотой следования f= 256 КГц (или f=128 КГц) при замкнутых контактах 58 и 60 (или 58 и 59), т. е. при X58=1 (или X58=C5}. На основании фиг. 3 и 5 функционирование блока 5 при C14=0 можно описать полностью сводкой формул

где C0,...,C5 - формируемые счетчиком 46 сигналы разрядных цифр.

Блок 12 управления (фиг. 4) предназначен для формирования четырех импульсных сигналов C31, !C32, !C33 и C34 и трех информационных сигналов X35 (фильтрованного запоминаемого сигнала состояния датчика). X36=Y3 (фильтрованного текущего сигнала состояния датчика) и сигнала X37, готовности устройства.

Функционирование блока 12 осуществляется по сигналу C14 сброса, трем информационным сигналам X21, X22 и X23, управляющему сигналу X24 и по трем импульсным сигналам !C25, C29 и !C30.

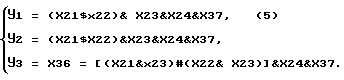

В процессе работы по импульсу C14 триггер 63 сбрасывается и вырабатывает сигнал X37= 0, а далее при C14=0 по фронту сигнала !C25 триггер 63 устанавливается и выставляет сигнал X37=1 готовности устройства. В целом функционирование блока 12 определяется работой формирователя 61, функционирующего согласно табл. 1 истинности. Данный формирователь 61 можно выполнить, например, на одной ИС 541 РТ1 (или 556РТ4), либо на обычных логических элементах, вырабатывающих функции Y1, Y2 и Y3 по формулам

С учетом (5) формирование блоком 12 импульсных сигналов описывается формулами

Кроме того, по спаду каждого импульса C29 триггер 64 устанавливается в состояние X35=X36, определяемое в этот момент времени сигналом Y3=X36.

Из (5) и (6) следует, что при (X24 # !X37)=0 в устройстве выполняется фиктивный такт функционирования, поскольку в этом случае импульсы !C33 и C34 не вырабатываются и содержимое блока 1 памяти сохраняется (см. п.2 табл. 1).

С учетом изложенного выше при X24 # !X37 = 1 (см. в табл. 1 п.1, п.3-п. 10) в процессе функционирования устройства в целом при !C17=0 можно выделить три режима его работы P1, P2 и P3 (фиг.5), причем в каждом из режимов сначала по спаду импульса C29 триггер 64 устанавливается в состояние X35=Y3 (где Y3 = X36 определен в табл. 1), а затем сформированная с помощью импульсов C31 (или !C32) и !C26 информация "K20D и X35" записывается по импульсу !C33 в память блока 1 по адресу K15A обрабатываемого канала ввода.

В этой связи выполнение режимов P1, P2 и P3 отличается только формированием счетчиком 6 кода K20D и формированием в P3 импульса C34.

Режиму P1 в табл.1 соответствуют п.1, п.3, п.6, п.7 и п.10. В этом режиме формируется код K20D=1000000 так, что сначала по импульсу C31 счетчик 6 сбрасывается, а затем по фронту импульса !C26 его содержимое увеличивается на единицу младшего разряда.

Режиму P2 в табл. 1 соответствуют п.4 и п.5. В этом режиме в процессе чтения из памяти блока 1 кода K19D при !C27=0 формируется код

K20D=K19D+1000000 (7)

так, что сначала по импульсу !C32 в счетчик 6 записывается код K19D. а затем по фронту импульса !C26 содержимое счетчика 6 увеличивается на единицу младшего разряда.

Режиму P3 в табл.1 соответствуют п.8 и п.9. Именно в режиме P3 формируется импульс C34 изменения сигнала состояния датчика обрабатываемого по адресу K15A канала ввода, а код K20D формируется в P3 так же, как и в режиме P1.

Таким образом, механизм обнаружения изменения состояния датчика каждого канала ввода состоит в подсчете в режиме P2 до заданного числа (P-1) совпадающих выборок X21 (где P - порог, определенный кодом K18D), в противном случае в режиме P1 происходит установка в исходное состояние и все начинается сначала. Поэтому обнаружение изменения сигнала состояния датчика некоторого канала ввода, отмечаемое формированием импульса C34, произойдет только в том случае, если для данного канала последовательно выполняются (P-1) раз режим P2, а затем выполняется всего один раз режим P3.

В процессе функционирования устройства по текущему коду K15A адреса и импульсам ! C33 записи в смежные системы может быть передана фильтрованная информация (бит X35) состояния каждого канала ввода, а по импульсам C34 в ядро системы может быть передана информация об изменении состояния датчика любого канала ввода, адресуемого кодом K15A. Кроме того, сигнал X37 может быть заведен на один из входов коммутатора 4, чтобы сообщить в ядро системы о готовности устройства по переходу бита X37 из "0" в "1".

Для обеспечения помехоустойчивости устройства для каждого обнаруживаемого сигнала с минимальной длительностью Tx должен быть выставлен временной порог обнаружения To, определенный выражениями

где Tc и Ec - определены в (2);

P - числовой порог обнаружения, определяемый кодом K18D.

В табл. 2 приведены временные параметры функционирования устройства, определенные с использованием (8).

Из (2), (8) и табл.2 следует, что в общем случае при заданном Tx должны быть определены целые числа Z и P в процессе решения следующей задачи целочисленного линейного программирования.

Задано линейное уравнение

Tx-(P+2)•Tц/Z=Ex, (9)

определяющее одновременно целевую функцию Ex при ограничениях

В процессе решения задачи ((9), (10)) для каждого конкретного Tx требуется определить целые числа Z и P, минимизирующие целевую функцию Ex при максимальном значении P из числа допустимых в (8).

Задача ((9), (10)) решается методом направленного перебора не более, чем за два шага следующим образом:

- на первом шаге определяется целое число

P1=entTx/Tn, (11)

где ent - оператор выделения целой части числа;

при P1 ≤ 129 искомыми решениями являются

в противном случае переходят ко второму шагу:

- на втором шаге ищется максимальное число

P2=entP1/Zi≤129, (13)

где варьируемой переменной является Zi= 1...,31.

На основании (10), (11) и (13) из множества (1,...,31) находим число Z и порог P= P2-2.

Таким образом, данное устройство позволяет обеспечить помехоустойчивый ввод битовой информации как в смежные системы, так и в ядро комплексно, т.е. с помощью как обнаружения изменения сигнала состояния каждого канала ввода по максимальному порогу из числа допустимых, так и автоматического устранения сбоев при хранении в блоке 1 памяти текущих результатов функционирования устройства.

Литература

1. Ушкар М.Н. Микропроцессорные устройства в радиоэлектронной аппаратуре /Под ред. Б. Ф, Высоцкого - М.: Радио и связь, 1988. - 128 с.: "Принципы построения микропроцессорных средств", с. (5-12).

2. Каган Б. М. , Сташин В. В. Основы проектирования микропроцессорных устройств автоматики - М.: Энергоатомиздат, 1987. - 304 с.: "Типичная структура микропроцессорного устройства (системы)" - с. (11-14).

3. Микроэлектронные устройства автоматики/А.А. Сазонов, А.Ю. Лукичев, В. Т. Николаев и др. Под ред. А.А. Сазонова. - М.: Энергоатомиздат, 1991 г. -384 с.: "Программируемый контроллер" - с. (253 - 259).

4. Краус М., Кучбах Э., Вошни О.-Г. Сбор данных в управляющих вычислительных системах. Пер. с нем. - М.: Мир. 1987. - 294 с.: "Устройства ввода данных", с. (83-87).

5. Проектирование цифровых устройств на однокристальных микроконтроллерах / В.В. Сташин, А.В. Урусов, О.Ф. Мологонцева. - М.: Энергоатомиздат, 1990. -224 с.: "Ввод информации с датчиков", с. (128-139).

6. Гитис Э. И. , Пискулов Е.А. Аналого-цифровые преобразователи. - М.: Энергоатомиздат. 1981. -360 с. : "Методы построения преобразователей временного интервала в код", с. (140- 158).

7. Рафикузаман М. Микропроцессоры и машинное проектирование микропроцессорных систем: в 2-х кн. Кн. 2. Пер. с англ. - М.: Мир, 1988. - 288 с.: "8279/8279-5-программируемый интерфейс клавиатуры и дисплея" - с.(288 - 245).

8. Авт. св. 1049891, G 06 F 3/02, СССР. Устройство для ввода информации /П.И.Бородин, Д.Н. Дудин и В.П. Сединкин - Опубл. 1983. Бюл. N 39.

9. А.с. 1080131, G 06 F 3/02, СССР. Устройство для ввода информации/" А. Н.Мурашко. -Опубл. 1984. Бюл.N 10.

10. А. с. 10895167, G 06 F 3/02, Устройство для ввода информации / В.В. Топилин. Опубл. 1984, Бюл. N16.

11. А. с. 1105883, G 06 F 3/02, СССР. Устройство для ввода информации / Ю.В.Морозов и В.А.Задорин. -Опубл. 1984. Бюл. N28.

12. А. с. 614434, М. Кл2 G 06 F 3/04, СССР. Устройство для сбора информации от дискретных датчиков / М.М.Сухомлинов, П.А.Волошин и др. - Опубл. 1978, Бюл.N25.

13. А.с. 746439. М. Кл2 G 05 B 23/02, G 06 F 15/46, СССР. Устройство для сбора данных от двухпозиционных датчиков / Б.А.Калиничев. Опубл. 1980. Бюл. N25.

14. А.с. 1109731, G 06 F 3/04, СССР. Устройство для сбора информации от дискретных датчиков/В.М.Быков и В.И.Гоносков. Опубл. 1984. Бюл. N31.

15. ПРОТОТИП, А.с. 1086420, G 06 F 3/00, СССР. Устройство для ввода информации / В.А. Сечкин и В. И. Юлдашев. Опубл. 1984. Бюл. N 14.

16. А. с. 1087979, G 06 F 3/04. СССР. Устройство для ввода информации / М.Н.Голованов, В.Р.Дума, Г.Л.Левин, Ю.Н.Родин. Опубл.1984. Бюл. N15.

17. А. с. 1540544, G 06 F 13/00, СССР. Устройство для сопряжения электронной вычислительной машины с дискретными датчиками / Ю.В.Крюков и А.В. Кузнецов. Опубл. 1988.

18. Огнев И. В., Сарычев К.Ф. Надежность запоминающих устройств. - М.: Радио и связь. 1988. - 224 с.: "Мажоритарное резервирование запоминающих устройств" - с. 155,156.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| КОММУТАТОР ЦИФРОВЫХ СИГНАЛОВ | 1999 |

|

RU2159006C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2344543C1 |

Изобретение относится к автоматике и вычислительной технике, предназначено для ввода информации от датчиков импульсных и статических сигналов в системах управления и может быть использовано, например, при построении контроллеров ввода битовой информации в функционально ориентированных микропроцессорных системах обработки информации и управления. Техническим результатом является расширение области использования устройства и обеспечение его помехоустойчивости за счет выставления максимального из допустимых порога обнаружения изменения сигнала состояния датчика для каждого канала ввода и за счет автоматического устранения сбоев при хранении текущих результатов функционирования устройства. Для этого устройство содержит блоки памяти, счетчики, коммутатор сигналов состояний датчиков каналов ввода, блок синхронизации, элементы И - НЕ, компаратор, блок управления. 2 табл., 5 ил.

Устройство для ввода информации, содержащее блок памяти, счетчик, коммутатор сигналов состояний датчиков каналов ввода, блок синхронизации и выходы каналов ввода, являющиеся информационными входами коммутатора, кодовый адресный вход которого соединен с кодовым выходом счетчика, счетный вход которого соединен с первым выходом блока синхронизации, отличающееся тем, что в него введены дополнительный блок памяти, дополнительный счетчик, четыре элемента И-НЕ, компаратор, блок управления, тактовый вход, соединенный с тактовым входом блока синхронизации, вход сброса, соединенный с входами сброса счетчика и блоков синхронизации и управления, адресный кодовый выход номера канала ввода, первые импульсный и информационный выходы соответственно импульса записи и бита фильтрованного состояния датчика канала для ввода в смежные системы, вторые импульсный и информационный выходы соответственно импульса обнаружения изменения состояния и бита состояния датчика канала для ввода в ядро системы, и выход сигнала готовности, причем кодовый выход счетчика соединен дополнительно с адресным кодовым выходом номера канала ввода устройства, с адресным кодовым входом блока памяти и с входами младших разрядов адреса дополнительного блока памяти, входы старших разрядов адреса которого соединены с дополнительным кодовым выходом счетчика, являющимся старшим его кодовым выходом, кодовый выход дополнительного блока памяти соединен с первым информационным входом компаратора, второй информационный вход компаратора соединен с информационным входом дополнительного счетчика и с кодовым информационным выходом блока памяти, кодовый информационный вход которого соединен с кодовым выходом дополнительного счетчика, выход коммутатора соединен с первым входом первого элемента И-НЕ, выход которого соединен с первыми входами второго и третьего элементов И-НЕ, первый выход блока синхронизации дополнительно соединен с стробирующим входом выбора блока памяти и с вторыми входами первого и второго элементов И-НЕ, первый информационный вход блока управления соединен с выходом третьего элемента И-НЕ и с первым входом четвертого элемента И-НЕ, второй вход которого соединен с выходом второго элемента И-НЕ, а выход соединен с вторым входом третьего элемента И-НЕ, битовый информационный выход блока памяти соединен с вторым информационным входом блока управления, третий информационный вход которого соединен с выходом компаратора, битовый выход дополнительного блока памяти соединен с управляющим входом блока управления, первый импульсный вход которого соединен с выходом переполнения счетчика, счетный вход дополнительного счетчика соединен с вторым выходом блока синхронизации, третий и четвертый выходы которого соединены соответственно с входами стробов чтения и передачи данных для записи блока памяти, пятый и шестой выходы блока синхронизации соединены соответственно с вторым и с третьими импульсными входами блока управления, первый и второй импульсные выходы которого соединены соответственно с входами сброса и установки дополнительного счетчика, вход импульса записи блока памяти соединен с первым импульсным выходом устройства и с третьим импульсным выходом блока управления, четвертый импульсный выход которого является вторым импульсным выходом устройства, битовый информационный вход блока памяти соединен с первыми информационными выходами блока управления и устройства, вторым информационным выходом устройства является второй информационный выход блока управления, третий информационный выход которого является выходом сигнала готовности устройства, причем блок памяти является блоком оперативной памяти с мажоритарным резервированием и содержит первый, второй и третий оперативные запоминающие элементы, первый, второй, третий и четвертый управляемые буферные передатчики, группу мажоритарных элементов, адресный кодовый вход, соединенный с адресными входами оперативных запоминающих элементов, стробирующий вход, соединенный с входами выбора оперативных запоминающих элементов, вход строба передачи данных для записи, соединенный с входами разрешения выходов первого, второго и третьего буферных передатчиков, вход строба чтения, соединенный с входами разрешения выходов оперативных запоминающих элементов и четвертого буферного передатчика, вход импульса записи, соединенный с входами записи оперативных запоминающих элементов, кодовый и битовый входы, связанные через первый, второй и третий буферные передатчики соответственно с информационными входами-выходами первого, второго и третьего оперативных запоминающих элементов, соединенными соответственно с первым, вторым и третьим информационными кодовыми входами группы мажоритарных элементов, информационный выход которой связан через четвертый буферный передатчик с кодовым и битовым выходами блока памяти.

| Устройство для ввода информации | 1982 |

|

SU1086420A1 |

| Устройство для ввода информации | 1985 |

|

SU1280600A1 |

| Устройство для ввода информации | 1985 |

|

SU1260934A1 |

| Устройство для ввода информации от двухпозиционных датчиков | 1990 |

|

SU1691827A1 |

| US 3787820 A, 20.01.1974 | |||

| JP 54074640 A, 14.06.1979. | |||

Авторы

Даты

2000-11-27—Публикация

1999-05-20—Подача