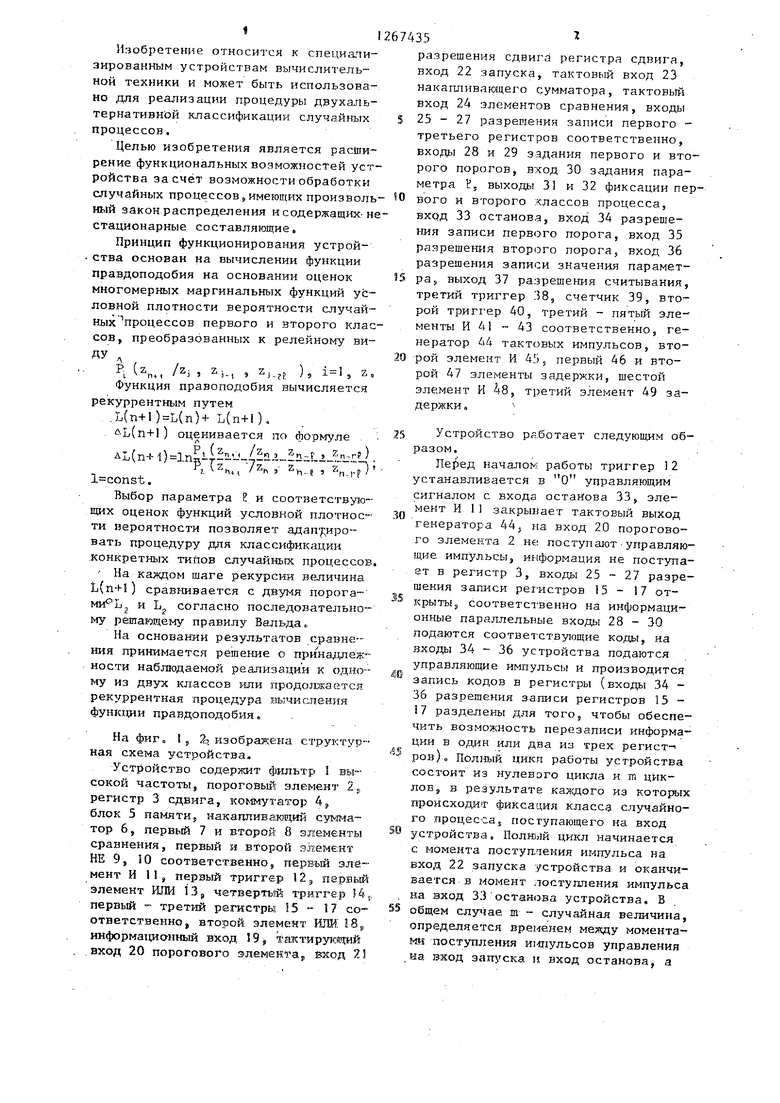

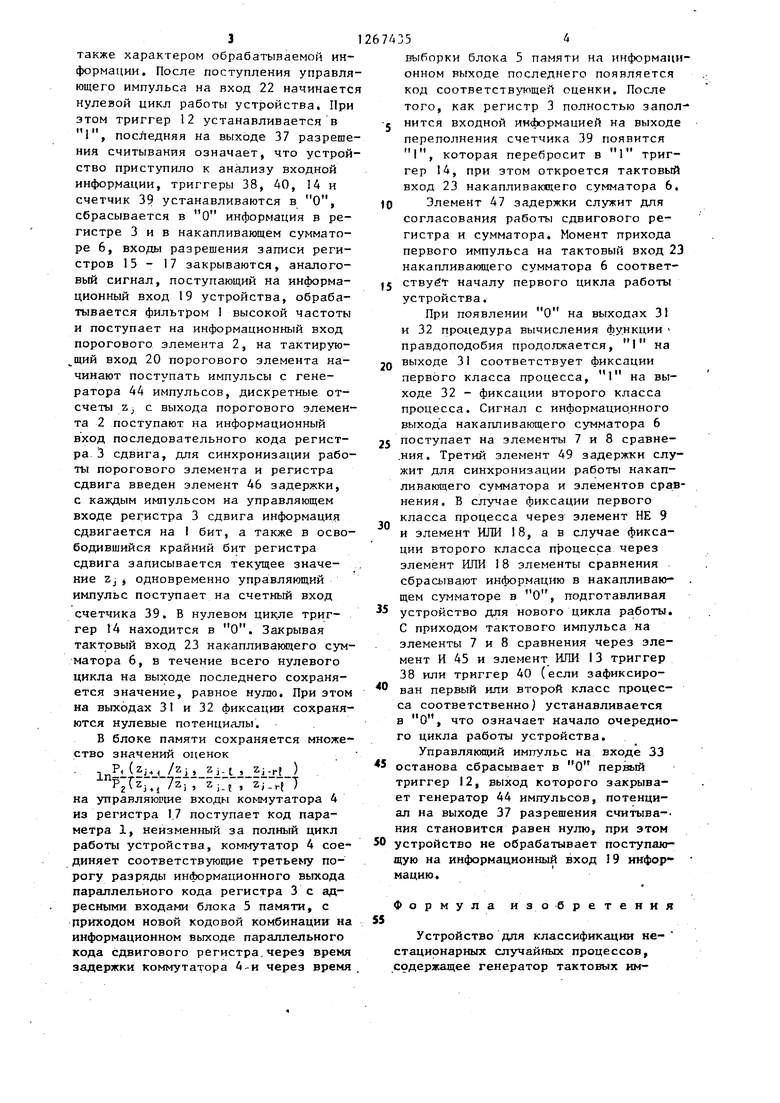

Изобретение относится к специализированным устройствам вычислительной техники и может быть использовано для реализации процедуры двухальтернативной классификации случайных процессов. Целью изобретения является расширение функциональных возможностей устройства за счёт возможности обработки случайных процессов J имеющих произволь ный закон распределения и содержащих-не стационарные составляющие, Принцип функционирования устройства основан на вычислении функции правдоподобия на основании оценок многомерных маргинальных функций условной плотности вероятности случайных процессов первого и второго клас сов, преобразованных к релейному виДУ . 1 п, i-i ьгР. ) i 9 Функция правоподобия вычисляется рекуррентным путем .L(n+l)L(n)+ L(n+l). . L(n+l) оценивается по формуле . (1 Р| 2,„, , /2„ J Zf,.f , ) AL(n-H)lnUii.-,, , Ъ-е 5 п-Г l const. Выбор параметра . и соответствующих оценок функций условной плотности вероятности позволяет адаприро-вать процедуру для классификации .конкретных типов случайных процессов На каждом шаге рекурсии в 1личина L(n-H ) сравнивается с двумя порогами Ь и L согласно последовательному решающему правилу Вальда. На основании результатов сравнения принимается решение о прина утежности наблюдаемой реализации к одному из двух классов или продолжается рекуррентная процедура вычисления функции правдоподобия. На фиг, IP 2 изображена структурная схема устройства. Устройство содержит фильтр I высокой частоты, пороговьй элемент 2,, регистр 3 сдвига, коммутатор 4, блок 5 памяти, накапливающий сумматор 6, первый 7 и второй 8 элементы сравнения, первый и второй элемент НЕ 9, 50 соответственно, первъш элемент И 11, первый триггер 12, первый элемент ИЛИ 13, четвертый триггер 14 первый - третий регистры 15 17 соответственно, второй элемент ИЛИ 18 информа1шсрнный вход 19 г1ктирук 1дий вход 20 порогового элемента вход 2 5 азрешения сдвига регистра сдвига, вход 22 запуска, тактовый вход 23 накапливающего сумматора, тактовый вход 24 элементов сравнения, входы 25 - 27 разрешения записи первого третьего регистров соответственно, входы 28 и 29 задания первого и второго порогов, вход 30 задания параметра Н, выходы 31 и 32 фиксации первого и второго классов процесса, вход 33 останова, вход 34 разрешения записи первого порога, вход 35 разрешения второго порога, вход 36 разрешения записи значения параметра j выход 37 разрешения считывания, третий триггер 38, счетчик 39, второй триггер 40, третий - пятый эле- менты ИД - 43 соответственно, генератор 44 тактовых импульсов, второй элемент И 45; первый 46 и второй 47 элементы задержки, шестой элемент И 48, третий элемент 49 задержки , Устройство работает следующим образом. Перед началом работы триггер 2 устанавливается в О управляющим сигналом с входа останова 33, элемент И I1 закрывает тактовый выход генератора 44, па вход 20 порогового элемента 2 не поступают-управляюрдие импульсы, информация не поступает в регистр 3, входы 25 - 27 разрешения записи регистров 15 - 17 открыты, соответственно на информационные параллельные входы 28-30 подаются соответствующие коды, на входь 34 - 36 устройства подаются управляющие импульсы и производится запись кодов в регистры (входы 34 36 разрешения записи регистров 15 17 разделены для того, чтобы обеспечить возможность перезаписи информации в один или два из трех регист-i ров)в Полный цикл работы устройства состоит из нулевого цикла и m циклов, в результате калодого из которых происходит фиксация класс случайного процесса, поступающего на вход устройства. Полнз й цикл начинается с момента поступления импульса на вход 22 запуска устройства и оканчивается в момент лостутшения импульса на вход 33останова устройства. В общем слуше m - случайная величина, определяется временем между моментаг-ш поступления иютульсов управления на вкод защска и вход останова, а

3

также характером обрабатываемой информации. После поступления управляющего импульса на вход 22 начинаетс нулевой цикл работы устройства. При этом триггер 12 устанавливается в 1, последняя на выходе 37 разрешения считывания означает, что устройство приступило к анализу входной информации, триггеры 38, 40, 14 и счетчик 39 устанавливаются в О, сбрасывается в О информация в регистре 3 и в накапливающем сумматоре 6, входы разрешения записи регистров 15 - 17 закрываются, аналоговый сигнал, поступающий на информационный вход 19 устройства, обрабатывается фильтром 1 высокой частоты и поступает на информационный вход порогового элемента 2, на тактирую щий вход 20 порогового элемента начинают поступать импульсы с генератора 44 импульсов, дискретные отсчеты Zj с выхода порогового элемента 2 поступают на информационный вход последовательного кода регистра. 3 сдвига, для синхронизации работы порогового элемента и регистра сдвига введен элемент 46 задержки, с каждым импульсом на управляющем входе регистра 3 сдвига информация сдвигается на I бит, а также в освободившийся крайний бит регистра сдвига записывается текущее значение Zj, одновременно управляющий импульс поступает на счетный вход счетчика 39, В нулевом цикле три1- гер 14 находится в О. Закрывая тактовый вход 23 накапливающего сумматора 6, в течение всего нулевого цикла на выходе последнего сохраняется значение, равное нулю. При этом на выходах 31 и 32 фиксации сохраняются нулевые потенциалы.

В блоке памяти сохраняется множество значений оценок

In- . JL- i-J-L ,, , z;.e , Zj.,( 7

на управляющие входы коммутатора 4 из регистра 1.7 поступает код параметра 1, неизменный за полный цикл работы устройства, коммутатор 4 соединяет соответствующие третьему порогу разряды информационного вьпсода параллельного кода регистра 3 с адресными входами блока 5 памяти, с приходом новой кодовой комбинации на информационном выходе параллельного кода сдвигового регистра.через время задержки коммутатора 4-и через время

674354

выборки блока 5 памяти на информационном выходе последнего появляется код соответствующей оценки. После того, как регистр 3 полностью запол5 нится входной информацией на выходе переполнения счетчика 39 появится 1, которая перебросит в 1 триггер 14, при этом откроется тактовый вход 23 накапливающего сумматора 6. О Элемент 47 задержки служит для согласования работы сдвигового регистра и сумматора. Момент прихода первого импульса на тактовый вход 23 накапливакнцего сумматора 6 соответ15 ствуёт началу первого цикла работы устройства.

При появлении О на выходах 3} и 32 процедура вычисления функции правдоподобия продолжается, 1 на 20 выходе 31 соответствует фиксации первого класса процесса, 1 на выходе 32 - фиксации второго класса процесса. Сигнал с информацио.нного выхода накапливающего сумматора 6 25 поступает на элементы 7 и 8 сравне.ния. Третий элемент 49 задержки служит для синхронизации работы накапливающего сумматора и элементов сравнения. В случае фиксации первого класса процесса через элемент НЕ 9 и элемент ИЛИ 18, а в случае фиксации второго класса процесса через элемент ИЛИ 18 элементы сравнения сбрасывают информацию в накапливающем сумматоре в О, подготавливая J5 устройство для нового цикла работы. С приходом тактового импульса на элементы 7 и 8 сравнения через элемент И 45 и элемент ИШ1 13 триггер 38 или триггер 40 (если зафиксиро ван первый или второй класс процесса соответственно устанавливается в О, что означает начало очередного цикла работы устройства.

Управляющий импульс на входе 33 5 останова сбрасывает в О первый триггер 12, выход которого закрывает генератор 44 импульсов, потенциал на выходе 37 разрешения считыва-ния становится равен нулю, при этом 50 устройство не обрабатывает поступающую на информационный вход 19 информацию.

Формула изобретения

Устройство для классификации нестационарных случайных процессов, содержащее генератор тактовых импульсов, первый триггер, три элемента задержки, три регистра, регистр сдвига, два элемента ИЛИ, накапливающий сумматор, три элемента И, причем выход генератора тактовых импульсов соединен с первым входом первого элемента И, второй вход которого соединен с прямым выходом nejpBoго триггера, выход первого элемента И соединен с входом первого элемента задержки о тличающееся тем, что, с целью расширения функциональных возможностей устройства за счет возможности обработки случайных процессов, именяцих произвольный закон распределения и содержащих нестационарные составлякнцие, в него введены фильтр высокой частоты пороговьг элемент, коммутатор, блок памяти, два элемента сравнения, два элемента НЕ, второй, третий, четвертый триггеры, cчeтчиk и четвертый, пятый, шестой элементы И, причем вход фильтра высокой частоты является информационным входом устройства, выход фильтра высокой частоты соединен с входом порогового элемента, выход которого соединен с входом последовательного кода регисчрра сдвига, выход параллельного кода которого соединен с информационным входом коммутатора, выход которого соеданен с адресным входом блока памяти„ выход которого соединен с первым входом накапливакнцего сумматора g, Bxojdp параллельного кода первого ре-, гистра является входом задания первого порога устройства, вход п 1рал-. лельного кода второго регистра является входом заданного второго порога устройства, вход параллельного кода третьего регистра является входом задания параметра Е устройства,, выход третьего регистра соединен с управляющим входЭм коммутатора, вы, ходы первого и второго регистров соединены с первыми входами соответственно первого и второго элементов сравнения, вторые входы которых соединены с выходом накапливающего сумматора, выход первого элемента сравнения соединен с входом первого) элемента НЕ и йервым входом второго элемента И, выход второго элемента сравнения соединен с входом- второго элемента НЕ, входом установки в 1 второго триггера и первым,входом первого элемента ИЛИ, выход которого

ра, входы установки в О счетчика, четвертого триггера, регистра сдвига, второй вход второго элемента ИЛИ третий вход первого элемента ИЛИ являются входом запуска устройства, первый вход третьего элемента И является входом разрешения записи первого порога устройства, первый вход четвертого элемента И является входом разрешения записи второго порога устройства, первый вход пятого элемента И является входом разрешения записи значения параметра устройства, вход установки в О первого триггера является входом остановки устройства, инверсный выход первого триггера соединен с вторьми входами третьего, четвертого и пятого элементов И, выходы которых соединены с входами разрешения записи соответственно первого, второго и третьего регистров, выход первого элемента И соединен с тактовым входом порогового элемента, выход первого элемента задержки соединен с входом разрешения сдвига регистра сдвига, со счетным входом счетчика и через второй элемент задержки - с первым входом шестого элемента И, выход переполнения счетчика соединен с входом установки в 1 четнертого триггера, прямой выход которого соединен с вторым входом шестого элемента И, выход которого соединен с тактовым входом Нс1капливаю1цего су 1матора и через третий элемент задержки с тактовыми входами первого и второго элементов сравнения, прямой выход первого триггера является выходом разрешения считывания рез.ультата устройства,, прямой выход третьего триггера является выходом фиксации первого класса процесса устройства, прямой выход второго триггера является вьзходом фиксации второго класса процесса устройства. соединен с входом сЬроса накапливающего сумматора, выход первого элемента НЕ соединен с входом установки в 1 третьего триггера и вторым входом первого элемента ИЛИ, выход второго элемента НЕ соединен с вторым входом второго элемента И, вы- . ход Kotoporo соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом установки в. О второго и третьего триггеров, вход установки в 1 первого тригге

Iput 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для классификации нестационарных случайных процессов | 1987 |

|

SU1462358A1 |

| Устройство для определения законов распределения вероятностей | 1984 |

|

SU1188753A2 |

| Устройство для статистической идентификации | 1988 |

|

SU1608693A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Устройство для вычисления математического ожидания | 1986 |

|

SU1322315A1 |

| Статистический анализатор | 1989 |

|

SU1631557A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для ввода информации | 1987 |

|

SU1522189A1 |

| Устройство для вычисления полиномов | 1984 |

|

SU1233140A1 |

Изобретение относится к специализированным устройствам вычислительной техники. Цель изобретения расширение функциональных возможностей устройства за счет возможности обр аботки случайных процессор имеющих произвольный закон распределения и содержащих нестационарные составляющие. Принцип функционирования устройства основан на вычислении функции правдоподобия на основании оценок многомерных маргиналыалх функций плотности условной вероятности случайных процессов первого и второго классов, преобразованных к релейному виду. С этой целью дополнительно введеШ) фильтр юлсокой частоты, блок памяти, логические элементы. Функция правдоподобия вычисляется рекурентно, текуинй результат накапливается на выходе сумматора, на S каждом шаге сравнивается с порогам, и на основании сравиения наблюдаемая реализация относится к одному из двух классов либо продолжается рекуррентная процедура вычислвимя функции правдоподобия. 2 ил. Од 4 со сл

| Устройство для анализа распреде-лЕНий СлучАйНыХ пРОцЕССОВ | 1979 |

|

SU830399A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения момента изменения свойств случайного процесса | 1980 |

|

SU888133A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1985-06-13—Подача