ли частота переключения п ячеек (т.е. первая тактовая частота) синхронна с периодом входного сигнала, то в какой-либо из п ячеек накапливаются положительные максимальные значения сигнала, в другой (отстоящей на п/2) накапливаются отрицательные максимальные значения. Когда этот набор переключается на считывание, то при последовательном опросе ячеек воспроизводится синусоидальная кривая. Точность ее воспроизведения зависит от числа п. Первая тактовая частота определяет резонансную частоту цифрового фильтра трез тТ1/т, Вторая тактовая частота определяет полосу пропускания цифрового фильтра Af тТ2. Синхронизация процессов накопления, считывания, записи в блок памяти и выдачи на выход осуществляется блоком управления.

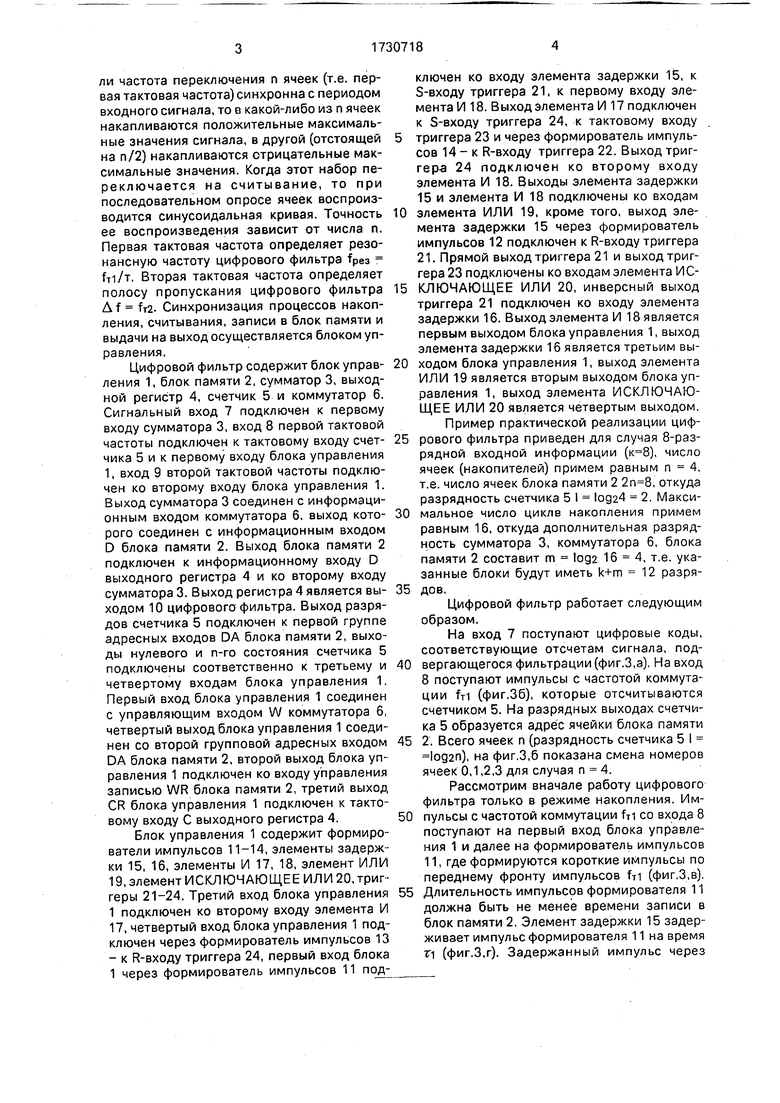

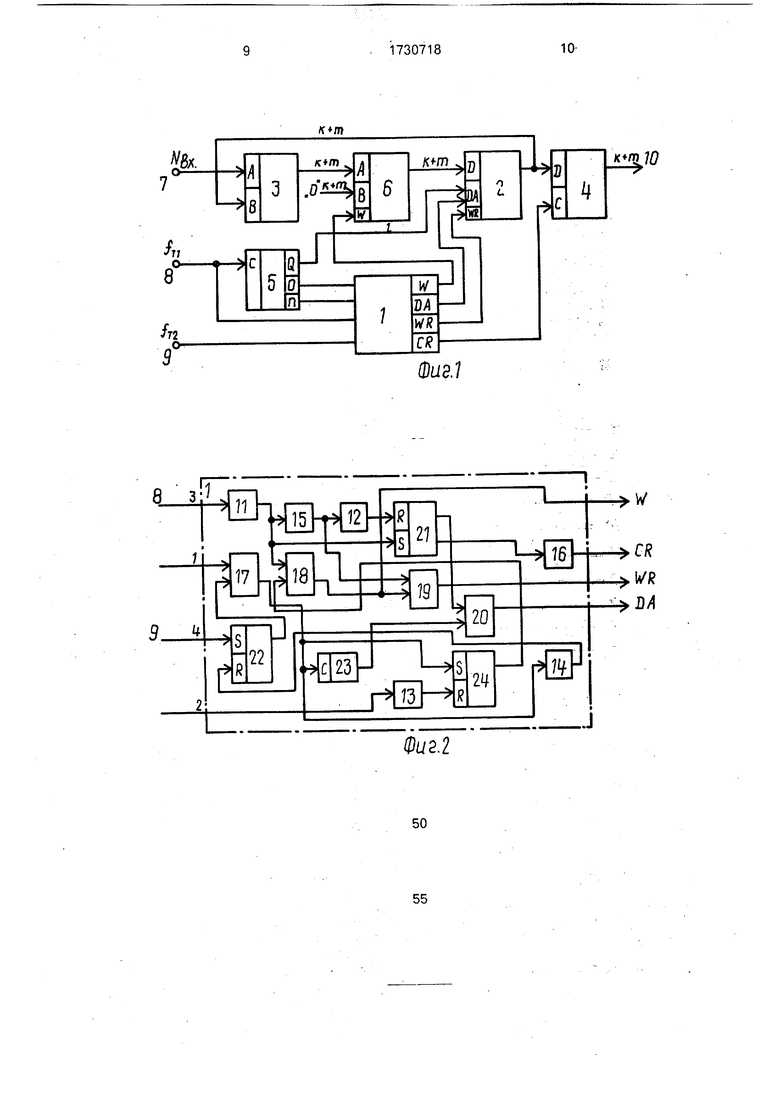

Цифровой фильтр содержит блок управления 1, блок памяти 2, сумматор 3, выходной регистр 4, счетчик 5 и коммутатор 6. Сигнальный вход 7 подключен к первому входу сумматора 3, вход 8 первой тактовой частоты подключен к тактовому входу счетчика 5 и к первому входу блока управления 1, вход 9 второй тактовой частоты подключен ко второму входу блока управления 1. Выход сумматора 3 соединен с информационным входом коммутатора 6, выход которого соединен с информационным входом D блока памяти 2. Выход блока памяти 2 подключен к информационному входу D выходного регистра 4 и ко второму входу сумматора 3. Выход регистра 4 является выходом 10 цифрового фильтра. Выход разрядов счетчика 5 подключен к первой группе адресных входов DA блока памяти 2, выходы нулевого и п-го состояния счетчика 5 подключены соответственно к третьему и четвертому входам блока управления 1. Первый вход блока управления 1 соединен с управляющим входом W коммутатора 6, четвертый выход блока управления 1 соединен со второй групповой адресных входом DA блока памяти 2, второй выход блока управления 1 подключен ко входу управления записью WR блока памяти 2. третий выход CR блока управления 1 подключен к тактовому входу С выходного регистра 4.

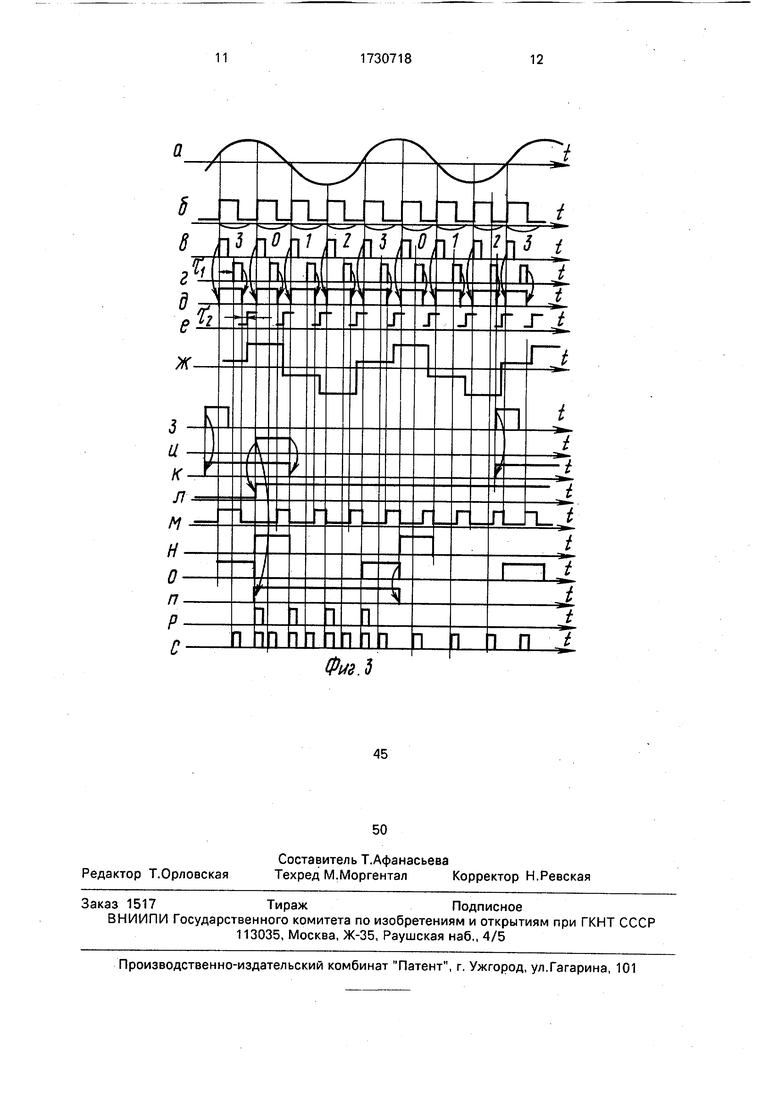

Блок управления 1 содержит формирователи импульсов 11-14, элементы задержки 15, 16, элементы И 17, 18, элемент ИЛИ 19, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20,триггеры 21-24. Третий вход блока управления 1 подключен ко второму входу элемента И 17, четвертый вход блока управления 1 подключен через формирователь импульсов 13 - к R-входу триггера 24, первый вход блока 1 через формирователь импульсов 11 под

ключей ко входу элемента задержки 15, к S-входу триггера 21, к первому входу элемента И 18. Выход элемента И 17 подключен к S-входу триггера 24, к тактовому входу

триггера 23 и через формирователь импульсов 14 - к R-входу триггера 22. Выход триггера 24 подключен ко второму входу элемента И 18. Выходы элемента задержки 15 и элемента И 18 подключены ко входам

элемента ИЛИ 19, кроме того, выход элемента задержки 15 через формирователь импульсов 12 подключен к R-входу триггера 21. Прямой выход триггера 21 и выход триггера 23 подключены ко входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20, инверсный выход триггера 21 подключен ко входу элемента задержки 16. Выход элемента И 18 является первым выходом блока управления 1, выход элемента задержки 16 является третьим выходом блока управления 1, выход элемента ИЛИ 19 является вторым выходом блока управления 1, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20 является четвертым выходом. Пример практической реализации цифрового фильтра приведен для случая 8-разрядной входной информации (), число ячеек (накопителей) примем равным п 4, т.е. число ячеек блока памяти 2 , откуда разрядность счетчика 5 I Iog24 2. Максимальное число циклв накопления примем равным 16, откуда дополнительная разрядность сумматора 3, коммутатора 6, блока памяти 2 составит m loga 16 4, т.е. указанные блоки будут иметь k+m 12 разрядов.

Цифровой фильтр работает следующим образом.

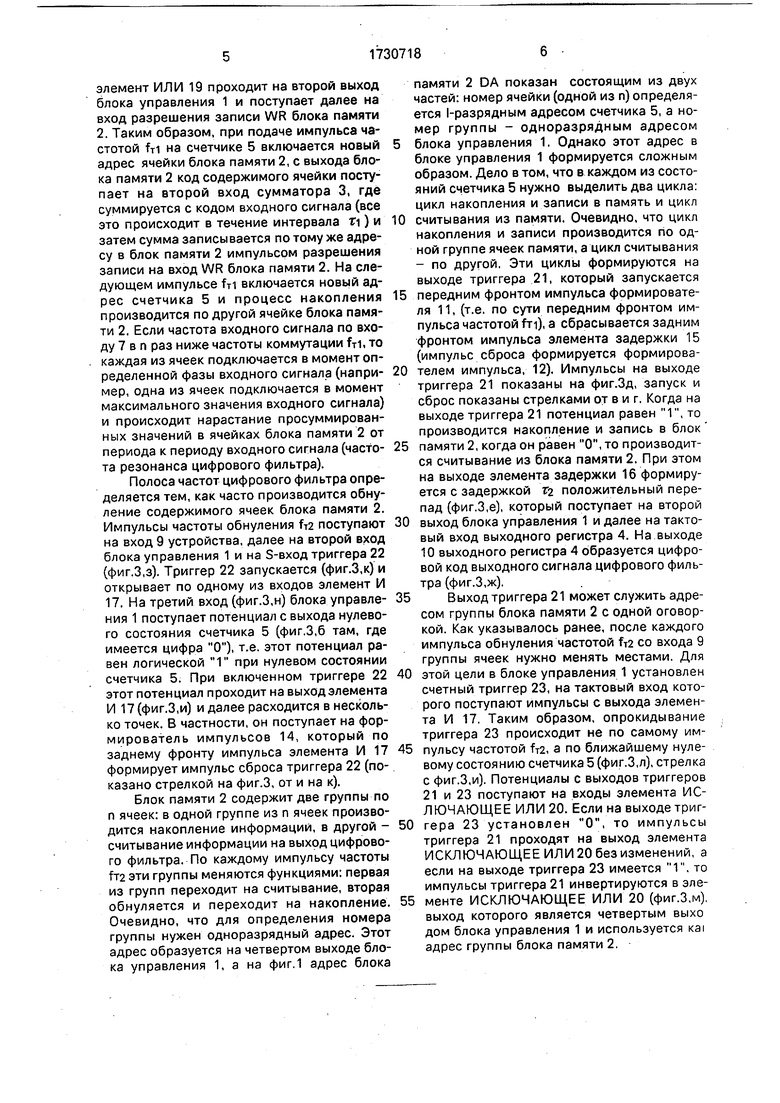

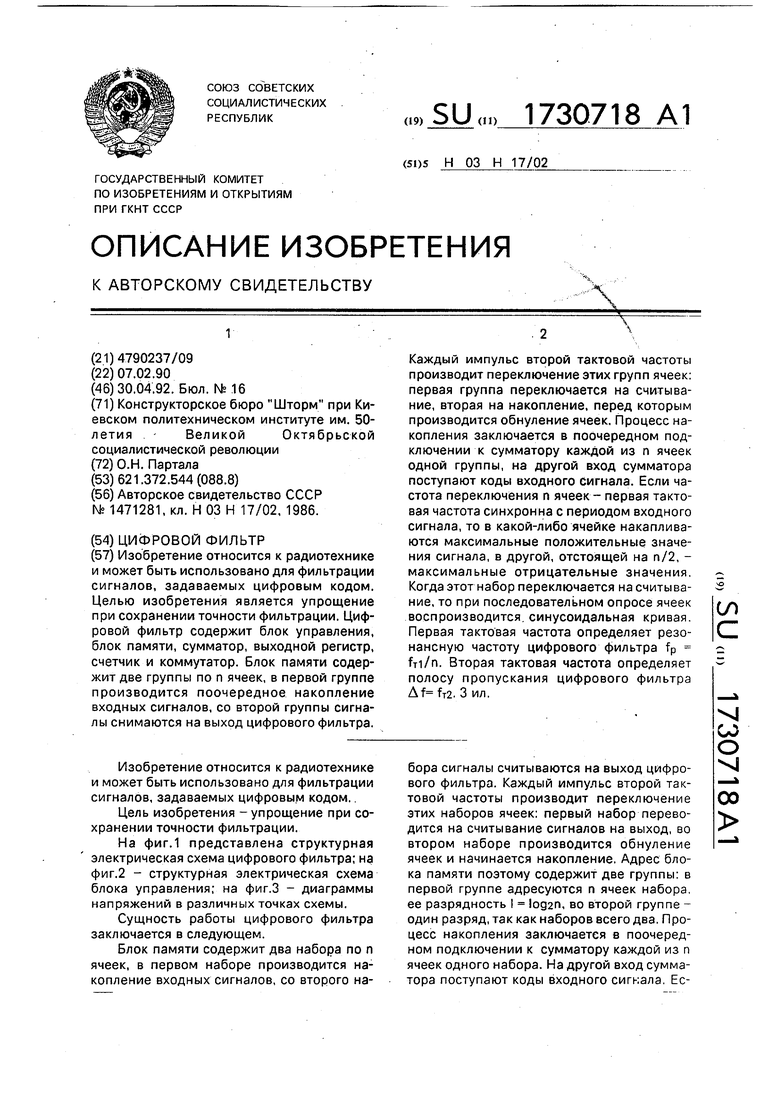

На вход 7 поступают цифровые коды, соответствующие отсчетам сигнала, подвергающегося фильтрации (фиг.З,а), На вход 8 поступают импульсы с частотой коммутации fri (фиг.36), которые отсчитываются счетчиком 5. На разрядных выходах счетчика 5 образуется адрес ячейки блока памяти

2. Всего ячеек п (разрядность счетчика 5 I 1од2п), на фиг.3,6 показана смена номеров ячеек 0,1,2,3 для случая п 4.

Рассмотрим вначале работу цифрового фильтра только в режиме накопления. Импульсы с частотой коммутации fTi со входа 8 поступают на первый вход блока управления 1 и далее на формирователь импульсов 11, где формируются короткие импульсы по переднему фронту импульсов fTi (фиг.З,в).

Длительность импульсов формирователя 11 должна быть не менее времени записи в блок памяти 2. Элемент задержки 15 задерживает импульс формирователя 11 на время П (фиг.З,г). Задержанный импульс через

элемент ИЛИ 19 проходит на второй выход блока управления 1 и поступает далее на вход разрешения записи WR блока памяти 2. Таким образом, при подаче импульса частотой fii на счетчике 5 включается новый адрес ячейки блока памяти 2, с выхода блока памяти 2 код содержимого ячейки поступает на второй вход сумматора 3, где суммируется с кодом входного сигнала (все это происходит в течение интервала TI ) и затем сумма записывается по тому же адресу в блок памяти 2 импульсом разрешения записи на вход WR блока памяти 2. На следующем импульсе fri включается новый адрес счетчика 5 и процесс накопления производится по другой ячейке блока памяти 2. Если частота входного сигнала по входу 7 в п раз ниже частоты коммутации fTi, то каждая из ячеек подключается в момент определенной фазы входного сигнала (например, одна из ячеек подключается в момент максимального значения входного сигнала) и происходит нарастание просуммированных значений в ячейках блока памяти 2 от периода к периоду входного сигнала (частота резонанса цифрового фильтра).

Полоса частот цифрового фильтра определяется тем, как часто производится обнуление содержимого ячеек блока памяти 2. Импульсы частоты обнуления fT2 поступают на вход 9 устройства, далее на второй вход блока управления 1 и на S-вход триггера 22 (фиг.З.з). Триггер 22 запускается (фиг.З,к) и открывает по одному из входов элемент И 17. На третий вход (фиг.З,н) блока управления 1 поступает потенциал с выхода нулевого состояния счетчика 5 (фиг.3,6 там, где имеется цифра О), т.е. этот потенциал равен логической 1 при нулевом состоянии счетчика 5. При включенном триггере 22 этот потенциал проходит на выход элемента И 17 (фиг.З.и) и далее расходится в несколько точек. В частности, он поступает на формирователь импульсов 14, который по заднему фронту импульса элемента И 17 формирует импульс сброса триггера 22 (показано стрелкой на фиг.З, от и на к).

Блок памяти 2 содержит две группы по п ячеек: в одной группе из п ячеек производится накопление информации, в другой - считывание информации на выход цифрового фильтра. По каждому импульсу частоты fT2 эти группы меняются функциями: первая из групп переходит на считывание, вторая обнуляется и переходит на накопление. Очевидно, что для определения номера группы нужен одноразрядный адрес. Этот адрес образуется на четвертом выходе блока управления 1, а на фиг.1 адрес блока

памяти 2 DA показан состоящим из двух частей: номер ячейки (одной из п) определяется 1-разрядным адресом счетчика 5, а номер группы - одноразрядным адресом

блока управления 1. Однако этот адрес в блоке управления 1 формируется сложным образом. Дело в том, что в каждом из состояний счетчика 5 нужно выделить два цикла: цикл накопления и записи в память и цикл

считывания из памяти. Очевидно, что цикл накопления и записи производится по одной группе ячеек памяти, а цикл считывания - по другой. Эти циклы формируются на выходе триггера 21, который запускается

передним фронтом импульса формирователя 11, (т.е. по сути передним фронтом импульса частотой fri), а сбрасывается задним фронтом импульса элемента задержки 15 (импульс сброса формируется формирователем импульса, 12). Импульсы на выходе триггера 21 показаны на фиг.Зд, запуск и сброс показаны стрелками от в и г. Когда на выходе триггера 21 потенциал равен 1, то производится накопление и запись в блок

памяти 2, когда он равен О, то производится считывание из блока памяти 2. При этом на выходе элемента задержки 16 формируется с задержкой тг положительный перепад (фиг.З,е), который поступает на второй

выход блока управления 1 и далее на тактовый вход выходного регистра 4. На выходе 10 выходного регистра 4 образуется цифровой код выходного сигнала цифрового фильтра (фиг.3,ж),

Выход триггера 21 может служить адресом группы блока памяти 2 с одной оговоркой. Как указывалось ранее, после каждого импульса обнуления частотой fT2 со входа 9 группы ячеек нужно менять местами. Для

этой цели в блоке управления 1 установлен счетный триггер 23, на тактовый вход которого поступают импульсы с выхода элемента И 17. Таким образом, опрокидывание триггера 23 происходит не по самому импульсу частотой fT2, а по ближайшему нулевому состоянию счетчика 5 (фиг.З,л), стрелка с фиг.З,и). Потенциалы с выходов триггеров 21 и 23 поступают на входы элемента ИС- ЛЮЧАЮЩЕЕ ИЛИ 20. Если на выходе триггера 23 установлен О, то импульсы триггера 21 проходят на выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20 без изменений, а если на выходе триггера 23 имеется 1. то импульсы триггера 21 инвертируются в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 20 (фиг.З,м) выход которого является четвертым выхо дом блока управления 1 и используется ка адрес группы блока памяти 2.

Импульсы обнуления частотой ft2 поступают во много раз реже, чем импульсы частотой fTi. Сам процесс обнуления содержимого ячеек должен происходить только в течение одного цикла обращения к п ячейкам блока памяти 2. Интервал обнуления формируется на триггере 24, который запускается импульсом с выхода элемента И 17, а сбрасывается задним фронтом импульса п-го состояния счетчика 6 (фиг. Зо), который поступает на четвертый вход блока управления 1 и через формирователь импульсов 13 сбрасывает триггер 24 (см. фиг.З.п - стрелки от фиг.З.п и фиг.З.о). Потенциал с выхода триггера 24 открывает элемент 1/1 18, который пропускает на выход импульсы формирователя 11 (фиг.3,р), поступающие на третий выход блока управления 1 и далее на управляющий вход W коммутатора 6. При подаче импульса на вход W коммутатор 6 подключает на выход нулевой код со своего входа В. Одновременно импульс с выхода элемента И 18 через элемент ИЛИ 19 поступает на второй выход блока 1 и далее на вход записи WR блока памяти 2. Таким образом, нулевой код записывается в ячейку. Как видно на фиг,3,с (выход элемента ИЛИ 19), при каждом адресе счетчика 5 импульс WR формируется дважды: на первом импульсе WR содержимое ячейки обнуляется, затем на интервале между первым и вторым импульсами WR производится считывание из блока памяти 2 нулевого кода, суммирование в сумматоре 3 нулевого кода с сигнальным кодом и запись по второму импульсу WR суммы в ту же ячейку памяти. Процесс повторяется по всем п ячейкам (пока включен триггер 24), а затем по этим ячейкам идет далее чистое накопление без обнуления до следующего импульса частотой fT2. Таким образом, время задержки т в элементе задержки 15 определяется временем, необходимым для записи нулевого кода в блок памяти 2, и временем, необходимым для считывания из блока памяти 2 и суммирования в сумматоре 3.

Формула изобретения 1. Цифровой фильтр, содержащий сумматор, первый вход которого является входом сигнала цифрового фильтра, а выход подключен к первому информационному входу коммутатора, блок памяти, информационный вход которого подключен к выходу коммутатора, а выход - ко второму входу сумматора и информационному входу выходного регистра, выход которого является

выходом фильтра, блок управления, первый вход которого объединен с тактовым входом счетчика и является входом импульсов первой тактовой частоты, второй вход является

входом импульсов второй тактовой частоты, первый выход соединен с управляющим входом коммутатора, второй выход- со входом управления записью блока памяти, а третий выход-с тактовым входом выходного регистра, отличающийся тем, что, с целью упрощения при сохранении точности фильтрации, разрядные выходы счетчика подключены к первому адресному входу блока памяти, выходы нулевого и п-го состояний счетчика подключены соответственно к третьему и четвертому входам блока управления, четвертый выход которого соединен со вторым информационным входом блока памяти, а ко второму информационному входу коммутатора подключена шина нулевого кода.

2. Фильтр по п.1,отличающийся тем, что блок управления содержит последовательно соединенные первый формирователь импульсов, вход которого является первым входом блока управления, первый элемент задержки, второй формирователь импульсов, первый триггер и элемент Исключающее ИЛИ, выход которого является четвертым выходом блока управления, второй триггер, S-вход которого является вторым входом блока управления, последовательно соединенные первый элемент И, первый вход которого является третьим входом блока управления, а второй вход подключен к выходу второго триггера и третий триггер, выход которого подключен к другому входу элемента Исключающее ИЛИ, последовательно соединенные третий

формирователь импульсов, вход которо является четвертым входом блока управления, четвертый триггер и второй элемент И, выход которого является первым выходом блока управления и подключен к первому входу

элемента ИЛИ, второй вход которого соединен с выходом первого элемента задержки, а выход является вторым выходом блока управления, при этом выход первого формирователя импульсов подключен к S-входу

первого триггера и второму входу второго элемента И, выход первого элемента И соединен с S-входом четвертого триггера и через четвертый формирователь с R-входом второго триггера, а выход первого триггера

подключен ко входу второго элемента задержки, выход которого является третьим выходом блока управления.

fl ,N

Фм.Ъ

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Цифровой фильтр | 1983 |

|

SU1249536A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1989 |

|

SU1679535A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

| Цифровой фильтр | 1986 |

|

SU1437968A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Фурье-Чебышеву | 1983 |

|

SU1136181A1 |

| ЛАЗЕРНЫЙ ИМПУЛЬСНЫЙ ДАЛЬНОМЕР | 2014 |

|

RU2551700C1 |

| Логический анализатор | 1986 |

|

SU1410033A1 |

Изобретение относится к радиотехнике и может быть использовано для фильтрации сигналов, задаваемых цифровым кодом. Целью изобретения является упрощение при сохранении точности фильтрации. Цифровой фильтр содержит блок управления, блок памяти, сумматор, выходной регистр, счетчик и коммутатор. Блок памяти содержит две группы по п ячеек, в первой группе производится поочередное накопление входных сигналов, со второй группы сигналы снимаются на выход цифрового фильтра. Изобретение относится к радиотехнике и может быть использовано для фильтрации сигналов, задаваемых цифровым кодом. Цель изобретения -упрощение при сохранении точности фильтрации. На фиг.1 представлена структурная электрическая схема цифрового фильтра; на фиг.2 - структурная электрическая схема блока управления; на фиг.З - диаграммы напряжений в различных точках схемы. Сущность работы цифрового фильтра заключается в следующем. Блок памяти содержит два набора по п ячеек, в первом наборе производится накопление входных сигналов, со второго наКаждый импульс второй тактовой частоты производит переключение этих групп ячеек: первая группа переключается на считывание, вторая на накопление, перед которым производится обнуление ячеек. Процесс накопления заключается в поочередном подключении к сумматору каждой из п ячеек одной группы, на другой вход сумматора поступают коды входного сигнала. Если частота переключения п ячеек- первая тактовая частота синхронна с периодом входного сигнала, то в какой-либо ячейке накапливаются максимальные положительные значения сигнала, в другой, отстоящей на п/2, - максимальные отрицательные значения. Когда этот набор переключается на считывание, то при последовательном опросе ячеек воспроизводится синусоидальная кривая. Первая тактовая частота определяет резонансную частоту цифрового фильтра fp fri/n. Вторая тактовая частота определяет полосу пропускания цифрового фильтра . 3 ил. со С бора сигналы считываются на выход цифрового фильтра. Каждый импульс второй тактовой частоты производит переключение этих наборов ячеек: первый набор переводится на считывание сигналов на выход, во втором наборе производится обнуление ячеек и начинается накопление. Адрес блока памяти поэтому содержит две группы: в первой группе адресуются п ячеек набора, ее разрядность I Iog2n, во второй группе - один разряд, так как наборов всего два. Процесс накопления заключается в поочередном подключении к сумматору каждой из п ячеек одного набора. На другой вход сумматора поступают коды входного сигнала. CJ о ч 00

| Цифровой фильтр | 1986 |

|

SU1471281A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-30—Публикация

1990-02-07—Подача