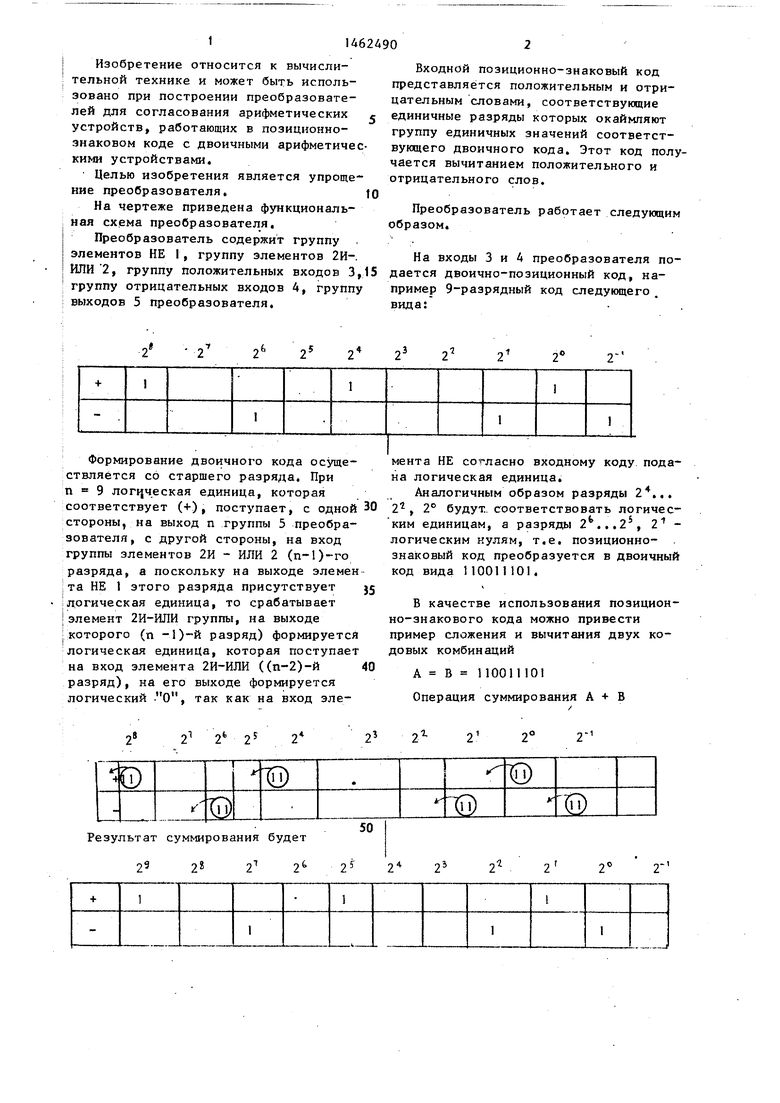

Формирование двоичного кода осуществляется со старшего разряда. При п 9 логическая единица, которая соответствует (+), поступает, с одной 30 стороны, на выход п группы 5 преобразователя, с другой стороны, на вход группы элементов 2И - ИЛИ 2 (п-1)-го разряда, а поскольку на выходе элемен ;та НЕ 1 этого разряда присутствует jj Iлогическая единица, то срабатывает I элемент 2И-ИЛИ группы, на выходе I которого (п -1)-й разряд) формируется логическая единица, которая поступает на вход элемента 2И-ИЛИ ((п-2)-й40

разряд), на его выходе формируется

мента НЕ согласно входному коду подана логическая единица.

Аналогичным образом разряды 2... 2, 2° будут, соответствовать логическим единицам, а разряды 2...2, 2 - логическим нулям, т.е. позиционно- . знаковый код преобразуется в двоичный код вида П0011101.

В качестве использования позицион- но-знакового кода можно привести пример сложения и вычитания двух ко- до вых ко мбин аций

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1984 |

|

SU1171787A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Преобразователь двоичного кода в позиционно-знаковый код | 1987 |

|

SU1438005A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

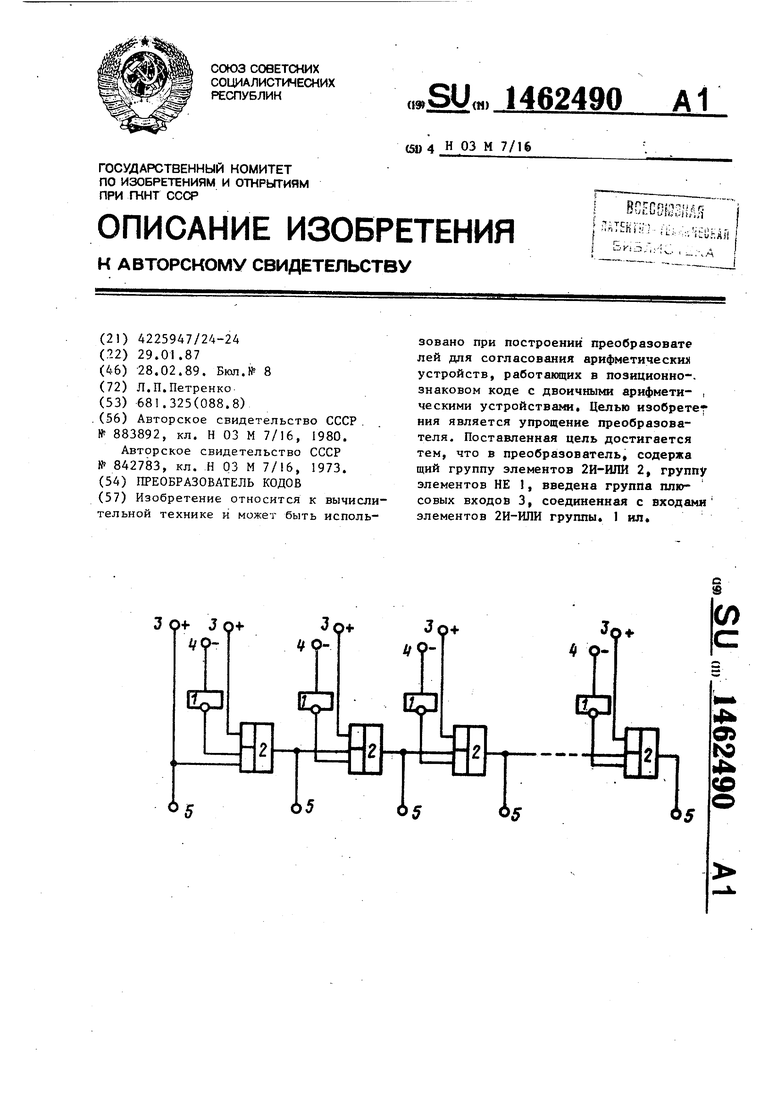

Изобретение относится к вычислительной технике и может быть использовано при построении преобразовате лей для согласования арифметическш устройств, работающих в позиционно-. знаковом коде с двоичными арифмети- , ческими устройствам. Целью изобретет ния является упрощение преобразователя. Поставленная цель достигается тем, что в преобразователь, содержа щий группу элементов 2И-ШШ 2, группу элементов НЕ 1, введена группа плюсовых входов 3, соединенная с входами элементов 2И-ИЛИ группы. 1 ил«

50

Результат суммирования будет

2 2 2

2V 2

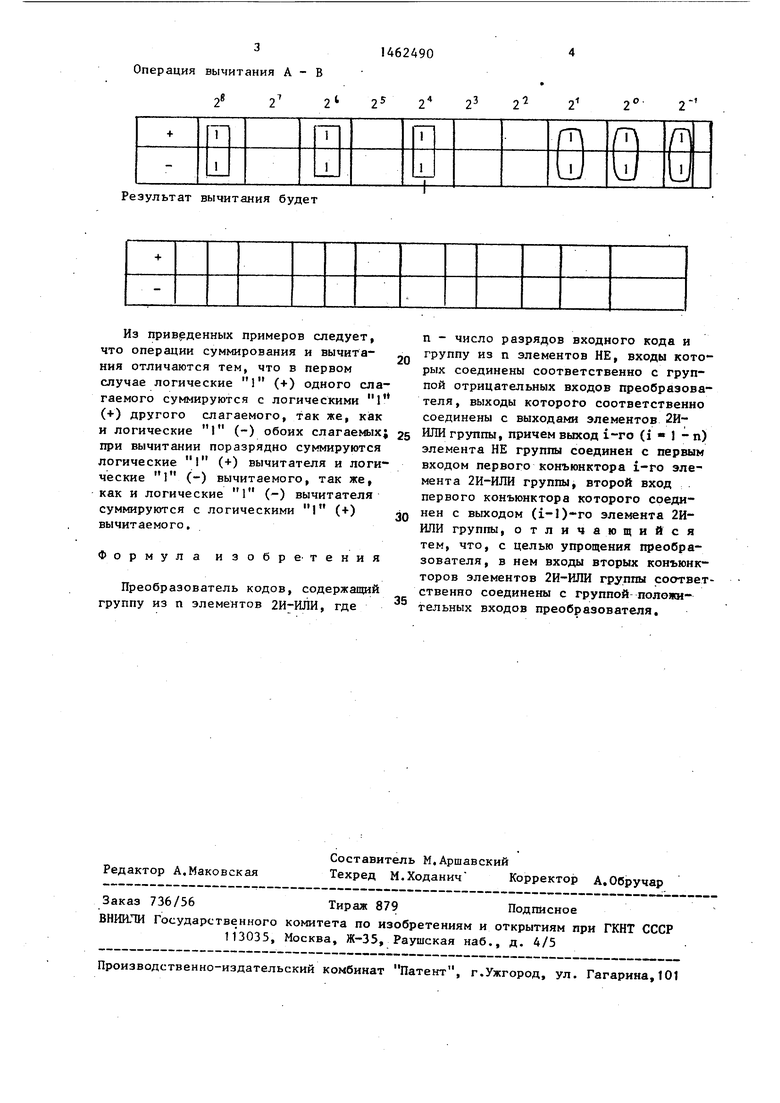

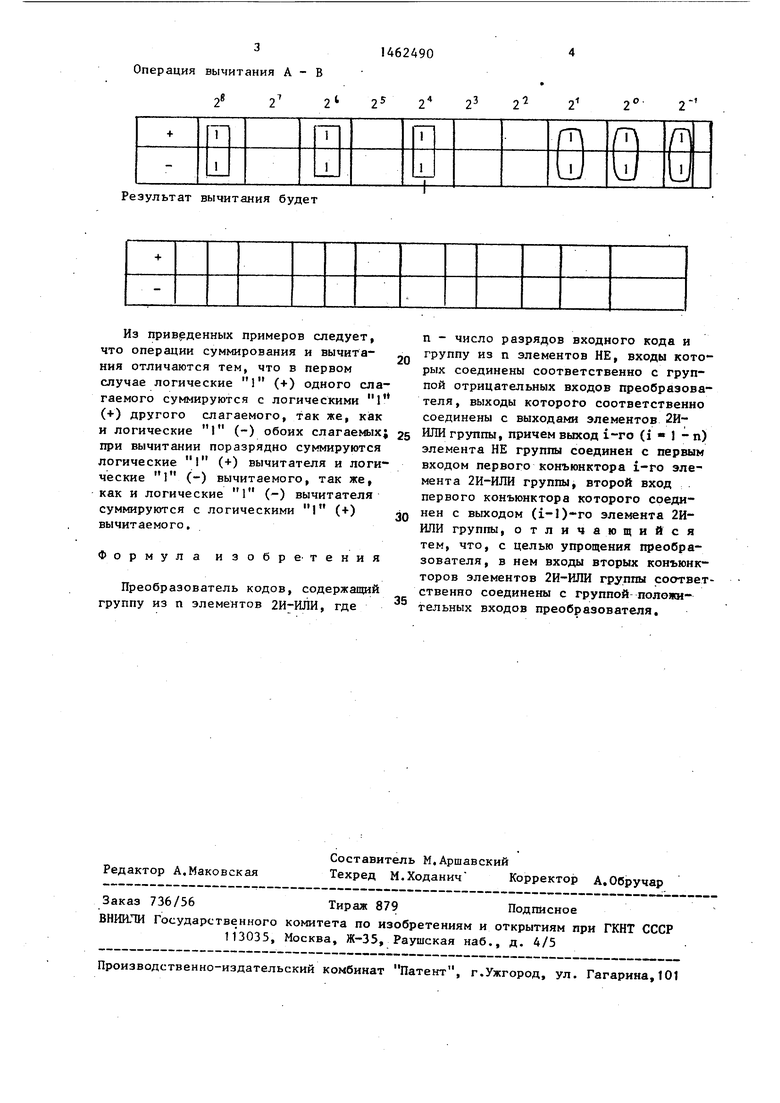

Из приведенных примеров следует, что операции суммирования и вычитания отличаются тем, что в первом случае логические 1 (+) одного слагаемого суммируются с логическими (+) другого слагаемого, так же, как и логические 1 (-) обоих слагаемых; при вычитании поразрядно суммируются логические I (+) вычитателя и логические 1 (-) вычитаемого, так же, как и логические 1 (-) вычитателя суммируются с логическими I (+) вычитаемого.

Формула изобретения Преобразователь кодов, содержащий

группу из п элементов 2И-ИЛИ, где

п - число разрядов входного кода и группу из п элементов НЕ, входы которых соединены соответственно с группой отрицательных входов преобразователя , выходы которого соответственно соединены с выходами элементов 2И- ИЛИ группы, причем вшсод i-ro (i « 1 - п) элемента НЕ группы соединен с первым входом первого конъюнктора i-ro элемента 2И-ИЛИ группы, второй вход первого конъюнктора которого соединен с выходом (i-l)-ro элемента 2И- ИЛИ группы, отличающийся тем, что, с целью упрощения преобразователя, в нем входы вторых конъюнк- торов элементов 2И-ИЛИ группы соответственно соединены с группой положительных входов преобразователя.

Авторы

Даты

1989-02-28—Публикация

1987-01-29—Подача