налов. Sc(t)Cos4wt и Ss(t)Sinda)t. На выходе сумматора 8 формируется однополосный сигнал

S J,,, (t) -и 6,, Cos () t+ZM l,

Формирователь 14, первый и второй умножители и сумматор 8 образуют на фиг.2 - пример выполнения формиро- д квадратурный модулятор. Для локалиИзобретение относится к радиотехнике и может быть использовано в радиосвязи, радиолокации для формирования дискретной сетки частот.

Цель изобретения - повышение быст- родействия.

На фиг.1 представлена структурная электрическая схема синтезатора частот;

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Частотный модулятор | 1989 |

|

SU1626320A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Формирователь частотно-модулированных сигналов | 1990 |

|

SU1732420A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1990 |

|

RU2030829C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2595629C1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1589366A1 |

| Устройство для временного и спектрального анализа сигналов | 1990 |

|

SU1793445A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР МНОГОФАЗНЫХ СИГНАЛОВ | 2010 |

|

RU2423782C1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение быстродействия. Синтезатор частот содержит накапливающий сумматор 1, сумматор 2 кодов, блоки памяти 3 и 9, ЦАП 4, 10 и 16, регулируемые усилители 5 и 11, фильтры 6 и 12 нижних частот, перемножители 7 и 13, сумматор 8, формирователь Т4 квадратурных сигналов и формирователь 15 кодов сигнала коктенсации, В синтезаторе частот путем введения соответствующей амплитудно-фазовой манипуляции сигналов на выходах фильтров 6 и 12 обеспечивается локализация переходных процессов на заданном интервале компенсации, что повышает его быстродействие. Синтезатор по п. 2 ф-лы отличается выполнением формирователя 15; дана его ил. 1 з.п. ф-лы, 2 ил.

вателя кодов сигнала компенсации.

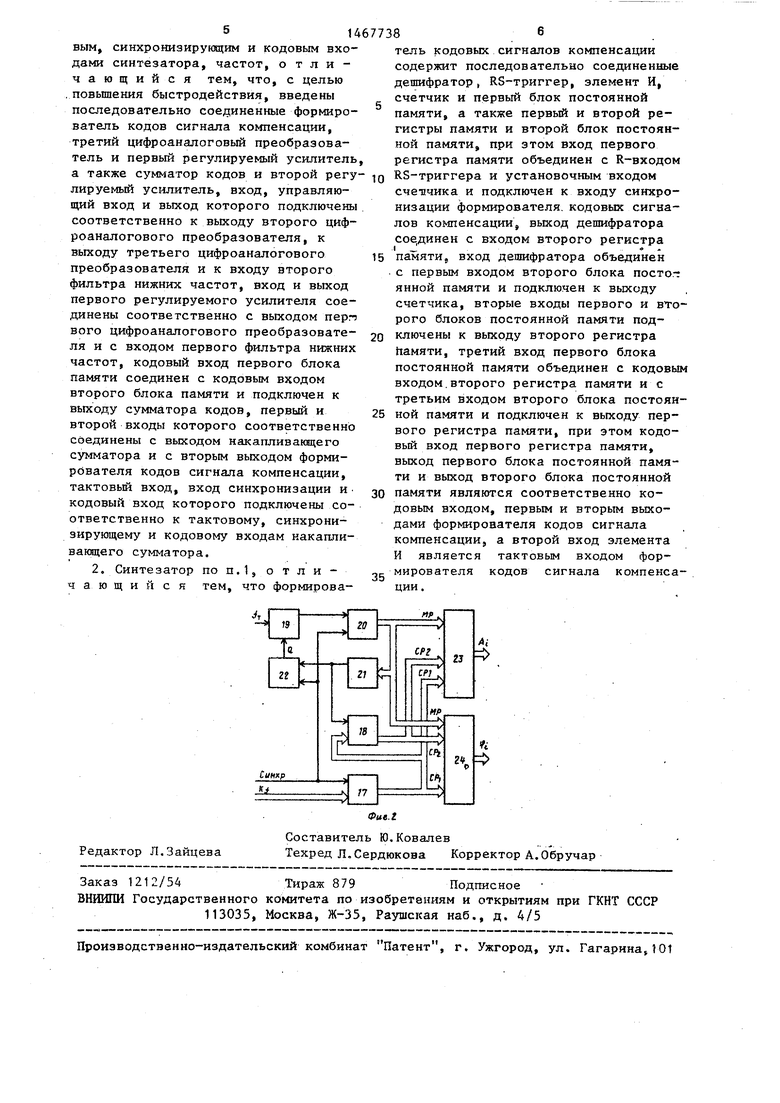

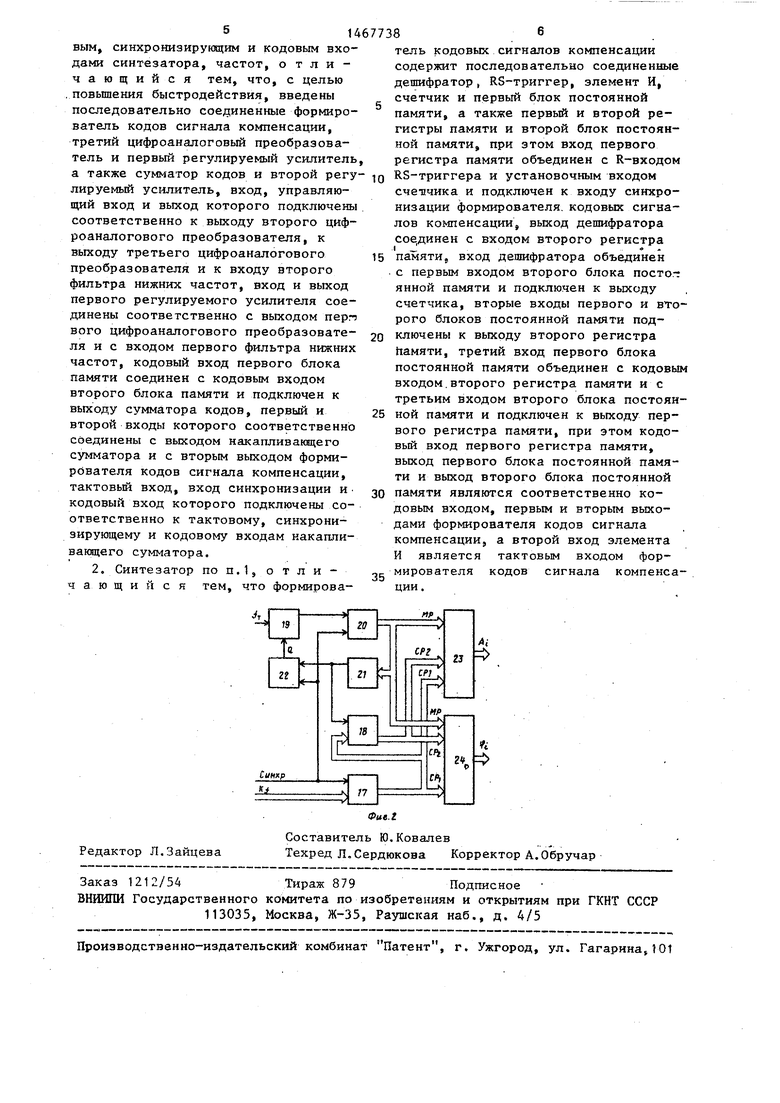

Синтезатор частот содержит накагши- вакщий сумматор (НС) 1, сумматор 2 кодов, первый блок 3 памяти, первый цифроаналоговый преобразователь (ЦАП) 4, первый регулируемый усилитель 5, первый фильтр 6 нижних частот, первый перемножитель 7, суммато 8j второй блок 9 памяти, второй ЦАП lOj второй регулируемый усилитель 11 второй фильтр 12 нижних частот, второй пере5множитель 13, формирователь 14 квадратурных сигналов, формирователь кодов t5 сигнала компенсации и третий ЦАП 16. При этом формирова- тель 15 кодов включает в себя первый регистр 17 памяти, второй регистр 18 памяти, элемент И 19, счетчик 20, дешифратор 21, RS-триггер 22, первый блок постоянной памяти (БПП) 23, второй БПП 24,

Синтезатор частот работает следующим образом.

В начальный момент в НС 1, в первый регистр 17 и во второй регистр 1В записывается код нулевой частоты К jf , Затем на первый вход синтезатора частот подается двоичный код требуемой частоты, который по импульсу синхронизации запоминается в НС 1 ВьЕсодной код НС 1 является кодом аргумента Н выборок тригонометрических функций Cos(21in/H) и Sin (21Тп/Н), занесенньгх в первый и второй блоки памяти 3 и 9 соответственно, где п - порядковьй номер выборки, п 0,1, 2,.,.,Н-1. Дискрет приращения кода аргумента тригонометрических функций равен 21ГК,7Н. С выхода НС 1 код аргу

fi ч, о выхода мента через сумматор 2 кодов поступает на адресные входы первого 3 и второго 9 блоков памяти, на выходах которых формируются выборки тригонометрических функций. С помощью первого 4 и второго 10 ЦАП эти выборки преобразуются в аналоговые сигналы со ступенчатой аппроксимацией, а с помощью первого 6 и второго 12, фильтров осуществляется формирование сиг

зации на заданном интервале переходных процессов, возникающих в первом 6 и втором 12 фильтрах, при переключении частоты на этом интервале осуществляется амплитудно-фазовая модуляция колебаний, подаваемых на первый 6 и второй 12 фильтры с помощью первого 5 и второго 1t регулируемых усилителей.

р«

|A;{lIt-(i-t)(t-it)}Sin(Kfnt+ /,)

t о t и t,

1 при SinKjSlt

при t - t

+ N + N

(2)

0

5 где А.

Ч 1/f, N

5

Ли) 0

5

амплитуды на выходах первого 5 и второго 11 регулирующих усилителей; начальные фазы на выход дах первого 5 и второго 11 регулирующих усилителей;

интервал формирования отсчетов колебаний; порядок первого 6 и второго 12 фильтров; сдвиг частоты выходного сигнала синтезатора частот;

дискрет сдвига частоты. Интервал компенсации переходных процессов кратен периоду колебания тактовой частоты. Количество периодов тактовой частоты, составляющих интервал компенсации равно порядку первого 6 и второго 12 фильтров. На каждом i-M периоде колебания тактовой частоты, на интервале компенсации устанавливается определенная амплитуда А; и фаза i/. сигналов на

51 21Г/Н ;

входах первого 6 и второго 12 фильтров. Закон изменения значений А; и W( на интервале компенсации для заданного фильтра зависит от предыдущего и устанавливаемого значений частоты генерируемого колебания.

С целью обеспечения на интервале компенсации необходимых параметров амплитудно-фазовой модуляции колебаний код частоты К {, записьшается в первый регистр 17 формирователя 15 кодов. Начальным синхроимпульсом счетчик 20 устанавливается в нулево состояние, RS-триггер 22 по выходу устанавливается в состояние логической 1, что разрешает прохождение тактовых импульсов через элемент И 19 на счетный вход счетчика 20, С помощью двух групп кодов адреса с выходов первого 17 и второго 18 регистров, подаваемых на адресные входы первого 23 и второго 24 БПП, выбираются требуемые законы фазово и амплитудной модуляций сигналов на выходах первого 4 и второго 10 ЦАП. Мгновенные значения требуемого фазового сдвига (. выбираются из второго БПП 24, а мгновенные значения амплитуды А. выбираются из первого БПП 23 по младшим адресным разрядам, прступагацим с выхода счетчика 20.

Считываемые из второго БПП 24 коды ц. поступают на второй вход сумматора 2 кодов, с помощью которого осуществляется фазовая модуляция. С выхода первого БПП 23 коды амплитуды А; поступают на третий ЦАП 16, где преобразуются в аналоговый сигнал, с помощью которого производится синхронное управление коэффициентами передачи первого 5 и второго 11 регулируемых усилителей. Количество значений А, и i,, требуемых для полной компенсации переходных процессов в первом 6 и втором 12 фильтрах, равно порядку этих,,фильтров. Переходные процессы полностью заканчийаются по истечении интервала компенсации. Параметры первого компенсирующего импульса А , и t/, выбираются из первого 23 и второго 24 БПП нулевым кодом с выхода счетчика 20. После прохождения на счетный вход счетчика 20 первого тактового импульса из первого БПП 23 выбираются параметры второго импульса компенсации А, а из второго БПП 24 - параметры второго импульса компенсации ч и т.д. После

выборки параметров п-г6 импульса компенсации следующий тактовый импульс устанавливают на выходе счетчи- ка 20 код числа п, который дешифрируется дешифратором 2t. Импульс с выхода дешифратора 21 устанавливает RS-триггер 22 в нулевое состояние и в дальнейшем прохождение тактовых JQ импульсов через элемент И |9 запрещается. Импульсом с выхода дешифратора 2t содержимое первого регистра .17 заносится во второй регистр 18, По коду числа с выхода счетчика 20 5 при любых состояниях первого 17 и второго Т8 регистров с выхода первого БПП 23 считывается код единичного . коэффициента передачи А, первого 5 и второго П регулируемых усилите- 0 лей, а с выхода второго БПП 24 - нулевой код фазы Lff,,. Это обеспечивает формирование сигналов S (t) и SsCt) на выходах первого 6 и второго 12 фильтров до записи в синтезатор 5 частот нового кода частоты.

Таким образом, путем введение соответствующей a mлитyднo-ч|)aзoвoй манипуляции сигналов на выходах первого 6 и второго 12 фильтров обеспе- 0 чивается локализация переходных процессов на заданном интервале компенсации, что повышает быстродействие синтезатора частот.

35

0

5

0

Формула изобретение

t. .Синтезатор частот, содержащий накапливающий сумматор, последовательно соединенные первьй блок памяти и первый цифроаналоговый преобразователь, последовательно соединенные второй блок памяти и втор ой цифроана- ,логовый преобразователь, последовательно соединенные первый фильтр нижних частот, первый перемножитель и сумматор, последовательно соединенные второй фильтр нижних частот и второй перемножитель, выход которого подключен к второму входу сумматора, а также формирователь квадратурные сигналов, вход которого является входом высокой частоты синтезатора частот, а первый и второй выходы формирователя квадратурных составляющих соединены соответственно с вторили входами первого и второго перемножителей, при этом тактовый, синхронизирующий - и кодовый входы накапливающего сумматора являются соответственно такто

| Авторское свидетельство СССР № , кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Ти рней, Рэйдер, Голд | |||

| Цифровые синтезаторы частоты, - Зарубежная радиоэлектроника, 1972, № 3, с.62-71. | |||

Авторы

Даты

1989-03-23—Публикация

1987-07-27—Подача