1

Изобретение относится к радиотехнике и измерительной технике и может быть использовано в приборостроении, автоматике и вычислительной технике.

Цель изобретения - повьпиение стабильности сдвига фаз выходных сигналов.

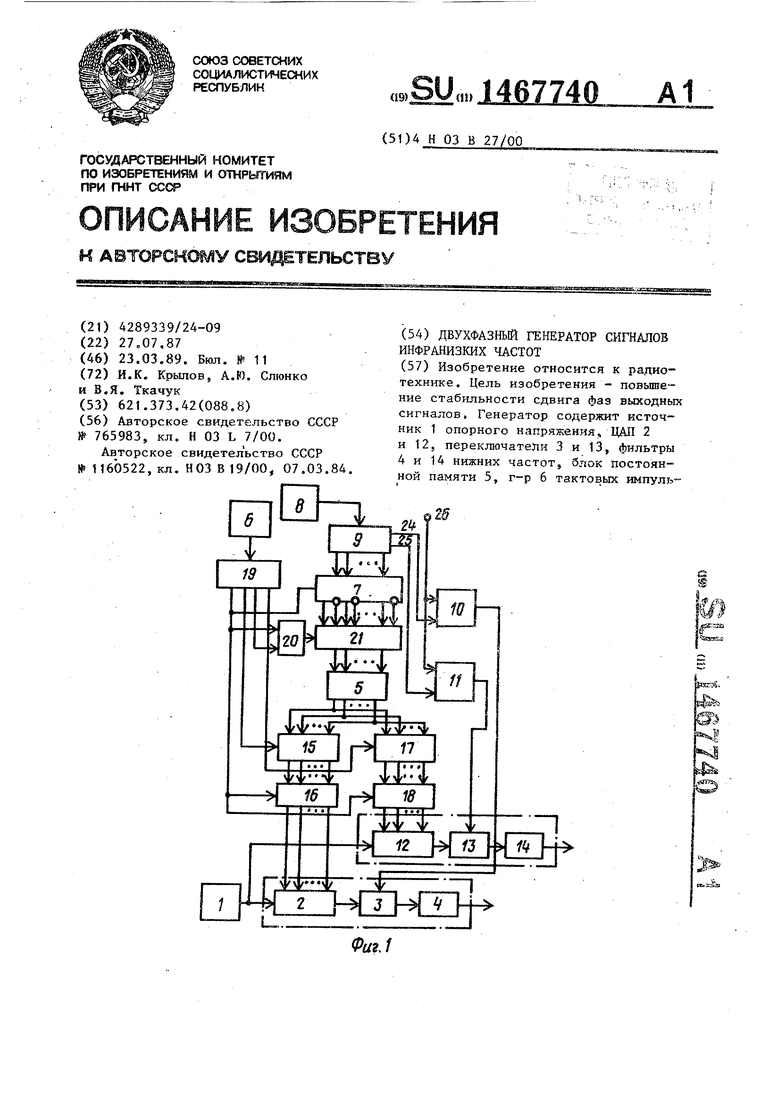

На фиг. 1 приведена структурная электрическая схема двухфазного генератора сигналов инфранизких частот; на фиг. 2-4 - временные диаграммы, поясняющие работу генератора.

Двухфазный генератор сигналов инфранизких частот содержит источник 1 опорного напряжения, первый цифро- аналоговый преобразователь ЦАП 2, первый переключатель 3, первый фильтр 4 нижних частот, блок 5 постоянной памяти, генератор 6 тактовых импульсов, регистр 7 сдвига, перестраиваемый генератор 8 импульсов, реверсивный счетчик 9, первый 10 и второй 11 счетные триггеры, второй цифроаналоговый преобразователь ЦАП 12, второй переключатель 13, второй фильтр 14 нижних частот, первый 15, второй 1б5третий 17 и четвертый

18регистры памяти, распределитель

19импульсов, RS-триггер 20, коммутатор 21.

Двухфазный генератор сигналов ни- франизких частот работает следующим образом.

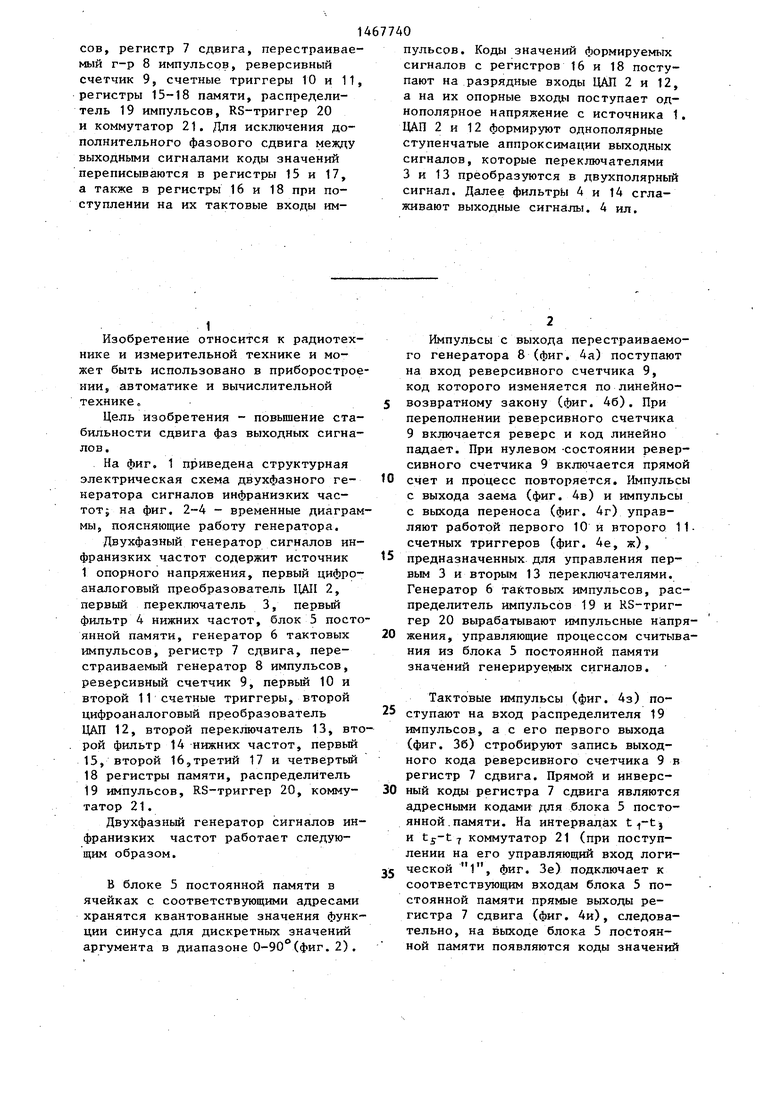

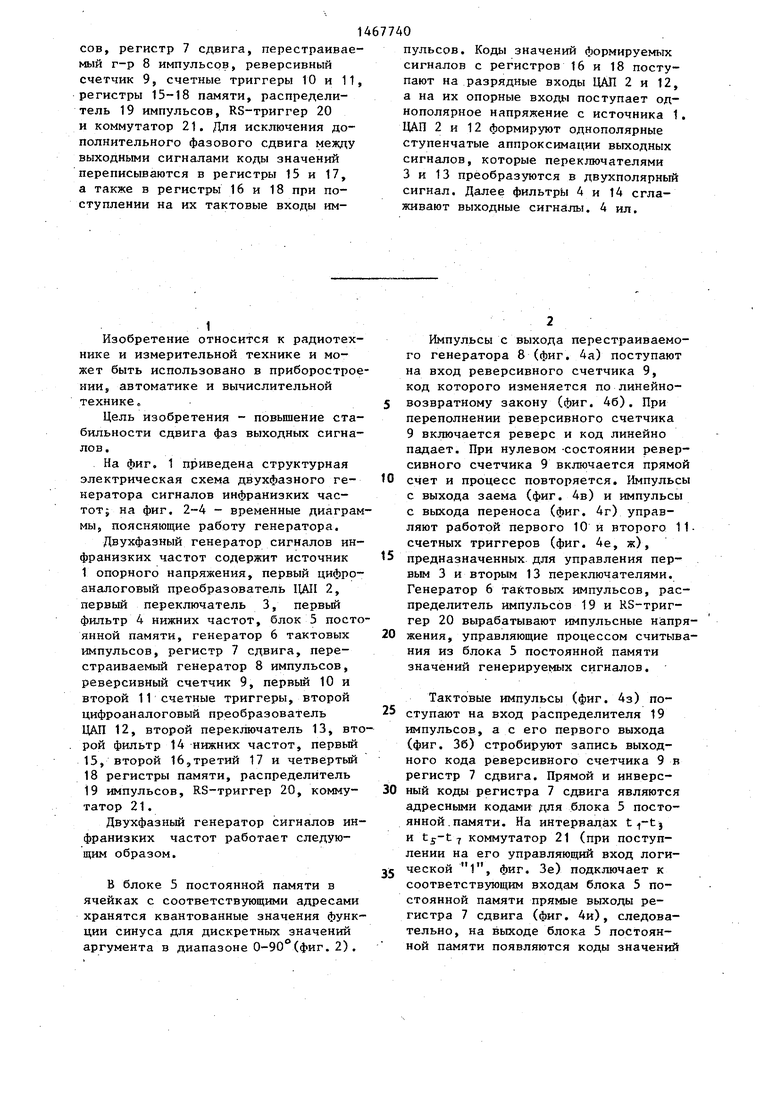

В блоке 5 постоянной памяти в ячейках с соответствующими адресами хранятся квантованные значения функции синуса для дискретных значений аргумента в диапазоне 0-90 (фиг. 2).

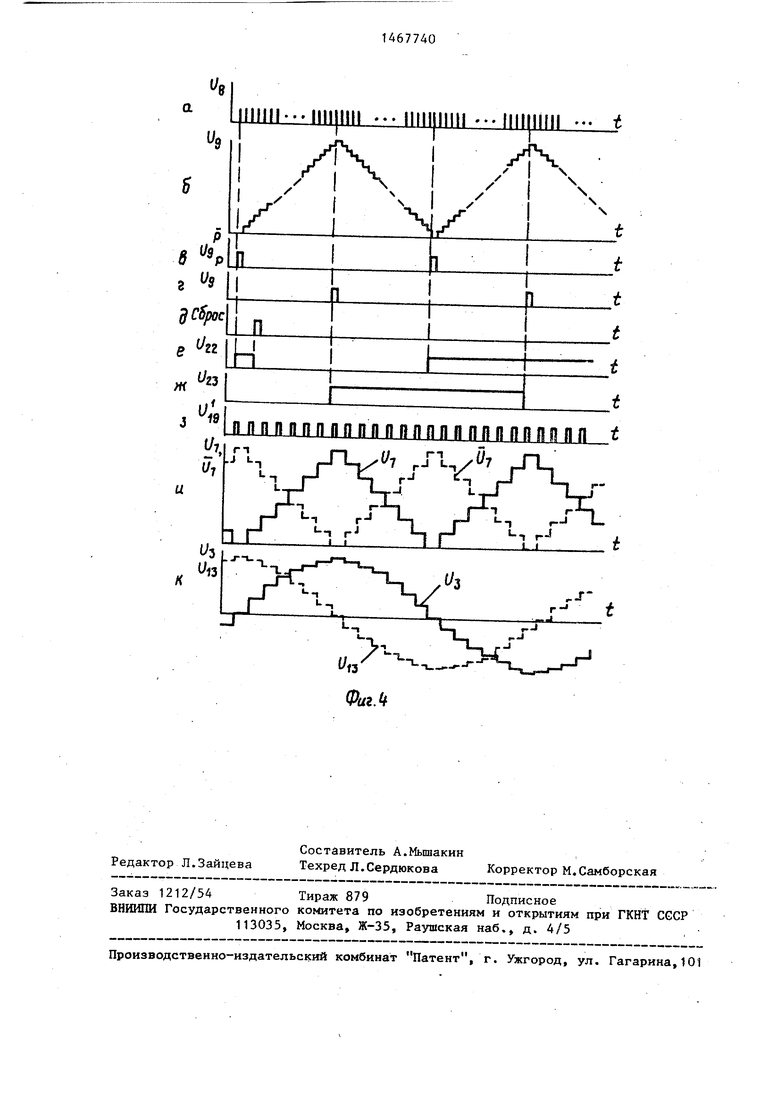

Импульсы с выхода перестраиваемого генератора 8 (фиг. 4а) поступают на вход реверсивного счетчика 9, код которого изменяется по линейновозвратному закону (фиг. 46). При переполнении реверсивного счетчика 9 включается реверс и код линейно падает. При нулевом -состоянии реверсивного счетчика 9 включается прямой

счет и процесс повторяется. Импульсы с выхода заема (фиг. 4в) и импульсы с выхода переноса (фиг. 4г) управляют работой первого 10 и второго 11- счетных триггеров (фиг. 4е, ж),

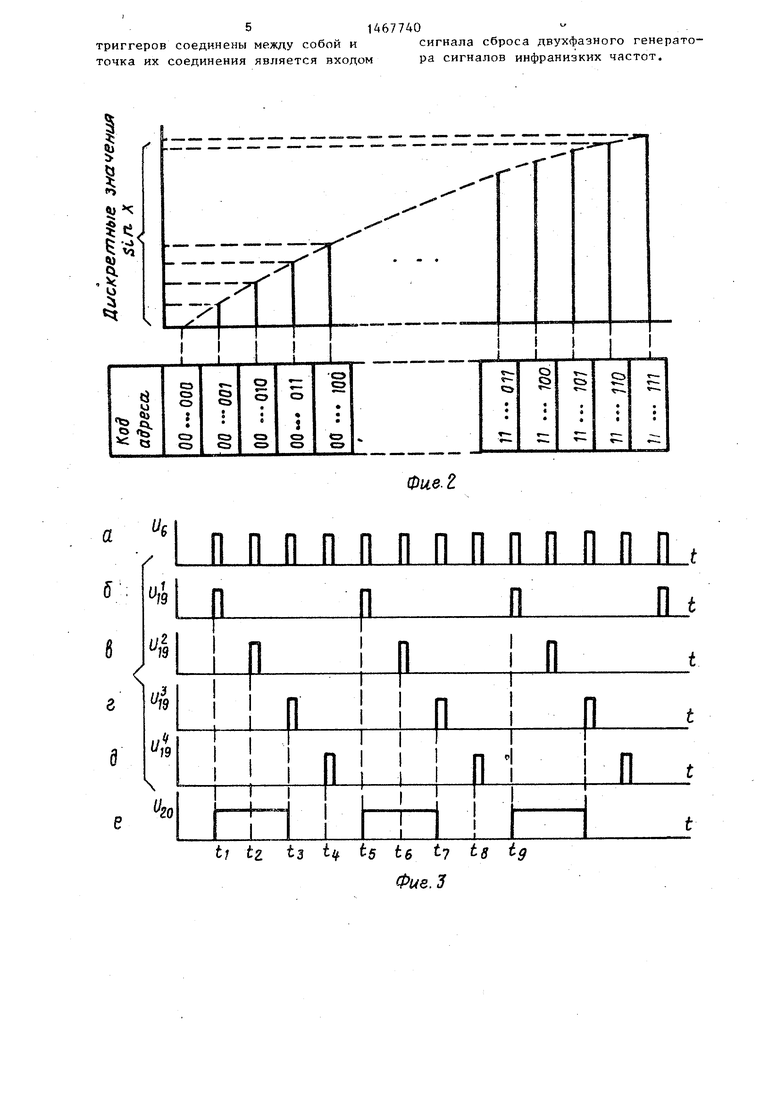

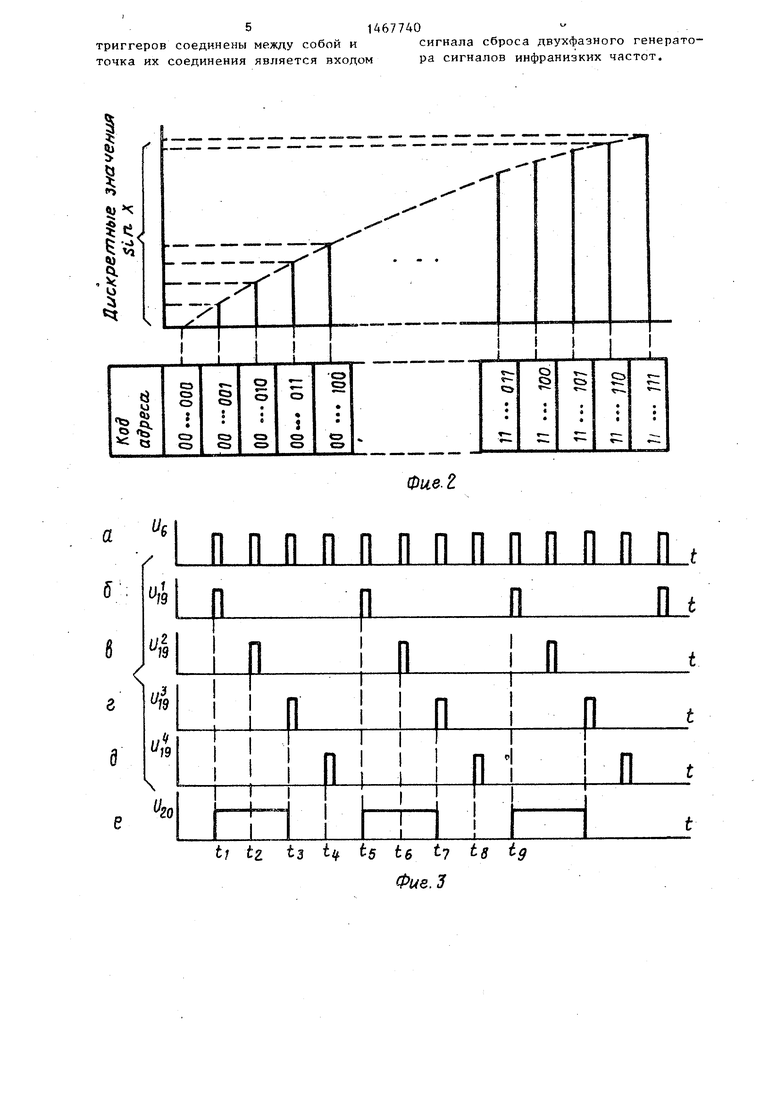

предназначенных для управления первым 3 и вторым 13 переключателями. Генератор 6 тактовых импульсов, распределитель импульсов 19 и RS-триггер 20 вырабатывают импульсные напряжения, управляющие процессом считывания из блока 5 постоянной памяти значений генерируемых сигналов.

Тактовые импульсы (фиг. 4з) по- ступают на вход распределителя 19 импульсов, а с его первого выхода (фиг. 36) стробируют запись выходного кода реверсивного счетчика 9 в регистр 7 сдвига. Прямой и инверс- ный коды регистра 7 сдвига являются адресными кодами для блока 5 постоянной, памяти. На интервалах t;,-tj и коммутатор 21 (при поступлении на его управляющий вход логи- ческой 1, фиг. Зе) подключает к соответствующим входам блока 5 постоянной памяти прямые выходы регистра 7 сдвига (фиг. 4и), следовательно, на выходе блока 5 постоянной памяти появляются коды значений

синусоидального сигнала. На интервалах времени t,-t5 и t-,-t g коммутатор 21 (при поступлении на его управляющий вход логического О, фиг. Зе) подключает к соответствующим входам блока 5 постоянной памяти инверсные выходы регистра 7 сдвига (фиг. 4и), следовательно, на выходе блока 5 постоянной памяти появляются коды значений косинусоидального сигнала для тех же значений аргументов, что и при считывании значений синусоидального сигнала.

Для исключения дополнительного фазового сдвига между выходными сигналами коды значений переписываются в перый 15 и третий 17 регистры памяти, а также в второй 16 и четвертый 18 регистры памяти при поступлении на их тактовые входы соответствующих импульсов (фиг. 3 б,в,г,д). Коды значений формируемых сигналов с разрядных выходов второго 16 и

и первьй фильтр нижних частот, в ход которого является первым вых дом двухфазного генератора сигна инфранизких частот, а также гене тор тактовых импульсов и блок по янной памяти, отличаюти с я тем, что с целью повышения с бильности сдвига фаз выходных сиг

,р лов, введены последовательно соед ненные второй цифроаналоговый пре разователь, вход опорного напряже которого соединен с выходом источ ка опорного напряжения, второй пе

5 ключатель и второй фильтр нижних тот, выход которого является втор выходом двухфазного генератора си лов инфранизких частот, последова тельно включенные первый и второй

2Q гистры памяти, последовательно вк ченные третий и четвертый регистр памяти, а также распределитель им пульсов, коммутатор,RS-триггер, п вый и второй счетные триггеры, пр

„„„„„„ . oiupuM счетные триггеры, пр

четвертого 18 регистров памяти посту- этом выход переноса и выход заема

ПаЮТ НЯ пя-зпаггчию ov.rr, ,О t -- а. п поалид dcteMd

пают на разрядные входы первого 2 и второго 12 ЦАП. На входы опорного напря жения первого 2 и второго 12ЦАП поступает однополярное напряжение с выхода источника 1 опорного напряжения, поэтому на выходах первого 2 и второго 12 1ДАП формируются одно- полярные ступенчатые аппроксимации выходных сигналов. Первый 3 и второй 13 переключатели преобразуют однополярный сигнал в двухполярный (фиг. 4к), первый 4 и второй 14 фильтры нижних частот сглаживают вы- ходные сигналы. Сигнал сброса (фиг. 4д) поступает на входы обнуления первого 10 и второго 11 счетных триггеров и служит для начальной взаимной фазовой привязки выходных сигналов после подачи питания на двухфазный генератор сигналов инфранизких частот. Изменение частоты генерируемых сигналов осул(ествляется путем перестройки частоты перестраиваемого генератора 8.

30

40

45

реверсивного счетчика соединены с ответственно со счетными входами первого и второго счетных триггер выходы которых соединены соответственно с управляющими входами пер вого и второго переключателей, раз рядные выходы второго и четвертого регистров памяти соединены соответ ственно с разрядными входами перво го и второго цифроаналоговых преоб разователей, nepBbiji выход распреде лителя импульсов соединен с тактовым входом второго и четвертого регистров памяти, S-входом RS-триг гера и тактовым входом регистра сдвига, прямые и инверсные выходы регистра сдвига соединены с соответствующими входами коммутатора, ходы которого подключены к соотве ствующим входам блока постоянной памяти, управляющий вход коммутато ра соединен с выходом RS-триггера, R-вход которого соединен с вторым выходом распределителя ггмпульсов, выход генератора тактовых импульсов соединен с входом распределителя импульсов, третий и четвертый выход которого соединены соответственно с тактовыми входами первого и третьег регистров памяти, информационные входы первого и третьего регистров памяти поразрядно объединены и подключены к соответствующим выходам блока постоянной памяти, входы обну ления первого и второго счетных

Формула изоб

Р е т е н и я

Двухфазный генератор сигналов инфранизких частот, содержащий последовательно перестраиваемый генератор импульсов, реверсивный счетчик и регистр сдвига, последовательно соединенные источник опорного напряжения, первый цифроаналоговый преобразователь, первый переключатель

1467740

и первьй фильтр нижних частот, выход которого является первым выходом двухфазного генератора сигналов инфранизких частот, а также генератор тактовых импульсов и блок постоянной памяти, отличаютий- с я тем, что с целью повышения стабильности сдвига фаз выходных сигнар лов, введены последовательно соединенные второй цифроаналоговый преобразователь, вход опорного напряжения которого соединен с выходом источника опорного напряжения, второй пере5 ключатель и второй фильтр нижних частот, выход которого является вторым выходом двухфазного генератора сигналов инфранизких частот, последовательно включенные первый и второй реQ гистры памяти, последовательно включенные третий и четвертый регистры памяти, а также распределитель импульсов, коммутатор,RS-триггер, первый и второй счетные триггеры, при

° oiupuM счетные триггеры, пр

этом выход переноса и выход заема

а. п поалид dcteMd

30

40

5

0

5

реверсивного счетчика соединены соответственно со счетными входами первого и второго счетных триггеров, выходы которых соединены соответственно с управляющими входами первого и второго переключателей, разрядные выходы второго и четвертого регистров памяти соединены соответственно с разрядными входами первого и второго цифроаналоговых преобразователей, nepBbiji выход распределителя импульсов соединен с тактовым входом второго и четвертого регистров памяти, S-входом RS-триг- гера и тактовым входом регистра сдвига, прямые и инверсные выходы регистра сдвига соединены с соответствующими входами коммутатора, выходы которого подключены к соответствующим входам блока постоянной памяти, управляющий вход коммутатора соединен с выходом RS-триггера, R-вход которого соединен с вторым выходом распределителя ггмпульсов, выход генератора тактовых импульсов соединен с входом распределителя импульсов, третий и четвертый выходы которого соединены соответственно с тактовыми входами первого и третьего регистров памяти, информационные входы первого и третьего регистров памяти поразрядно объединены и подключены к соответствующим выходам блока постоянной памяти, входы обнуления первого и второго счетных

51467740

триггеров соединены между собой и сигнала сброса двухфазного генерато- точка их соединения является входом

ра сигналов инфранизких частот.

сигнала сброса двухфазного генер

ра сигналов инфранизких частот.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный генератор | 1978 |

|

SU840853A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| КОРРЕЛЯЦИОННАЯ ИЗМЕРИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2007753C1 |

| Многоканальный аналого-цифровой процессор | 1983 |

|

SU1120375A1 |

| Устройство цикловой синхронизации | 1989 |

|

SU1626431A1 |

| Цифровой фазометр мгновенных значений | 1985 |

|

SU1320770A1 |

| Устройство сбора данных для цифрового анализатора сигналов | 1990 |

|

SU1751683A1 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

Изобретение относится к радиотехнике. Цель изобретения - повьше- ние стабильности сдвига фаз выходных сигналов. Генератор содержит источник 1 опорного напряжения. ЦА11 2 и 12, переключатели 3 и 13, фильтры 4 и 14 нижних частот, блок постоянной памяти 5, г-р 6 тактовых импуль

t; tz t3 i« 5 Ьб t 8 9

Фы&. З

| Генератор синусоидальных колебаний инфранизкой частоты | 1978 |

|

SU765983A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Генератор сигналов инфранизких частот | 1984 |

|

SU1160522A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1989-03-23—Публикация

1987-07-27—Подача