(Л

Од

Изобретение относится к импульсной технике и может быть использовано в БИС на основе инжекционной логики.

Цель изобретения - упрощение мажоритарного элемента типа.

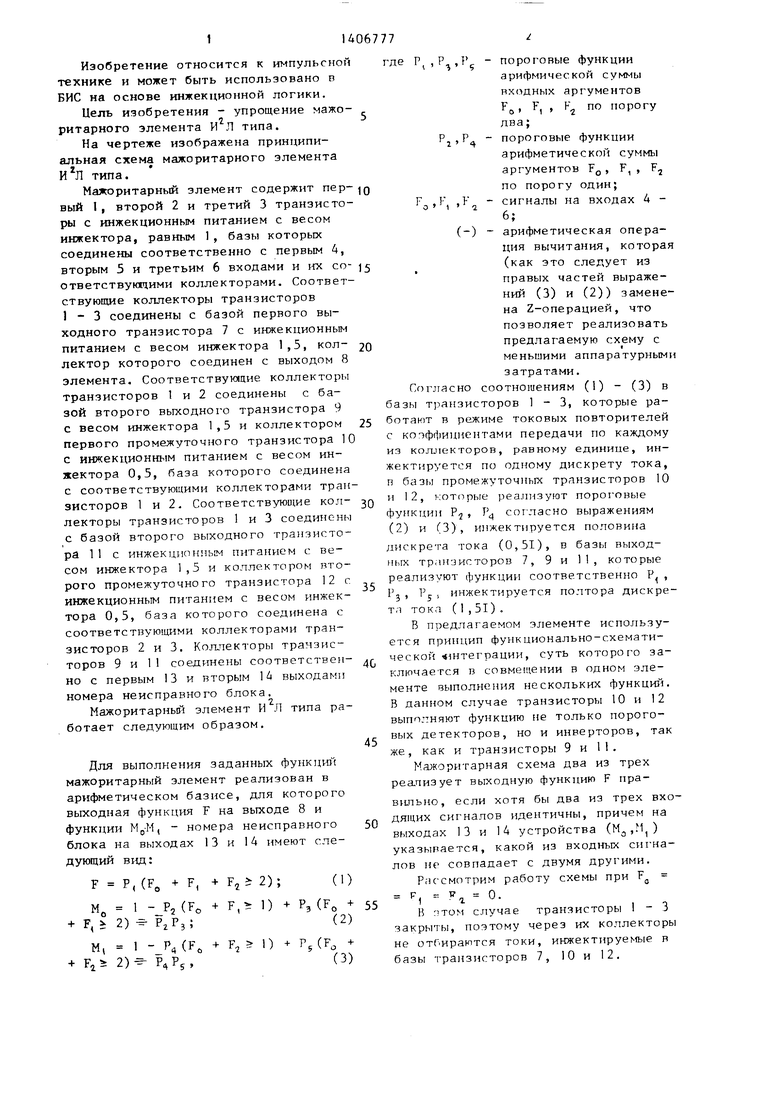

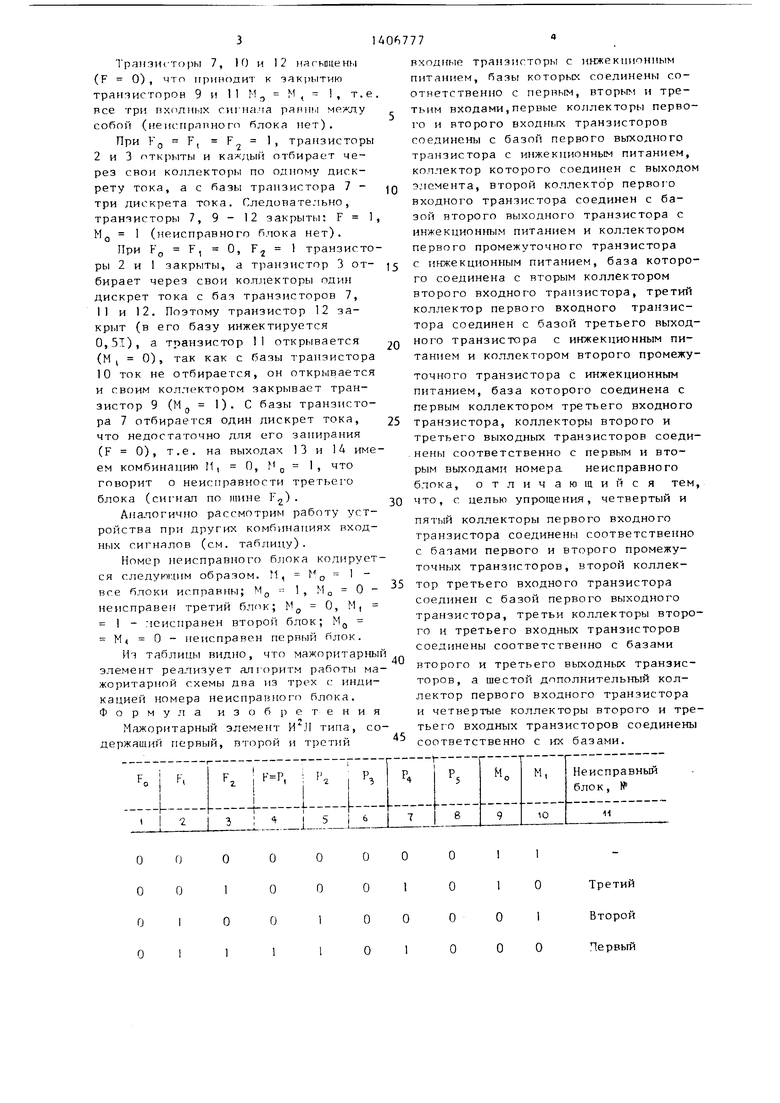

На чертеже изображена принципиальная схема мажоритарного элемента типа.

Мажоритарный элемент содержит первый I, второй 2 и третий 3 транзисторы с инжекционным питанием с весом инжектора, равным 1, баэы которых соединены соответственно с первым 4, вторым 5 и третьим 6 входами и их соответствующими коллекторами. Соответствующие коллекторы транзисторов 1 - 3 соединены с базой первого выходного транзистора 7 с инжекционным питанием с весом инжектора 1,5, кол- лектор которого соединен с выходом 8 элемента. Соответствукяцие коллекторы транзисторов 1 и 2 соединены с базой второго выходного транзистора 9 с весом инжектора 1,5 и коллектором первого промежуточного транзистора 10 с инжекционным питанием с весом инжектора 0,5, база которого соединена с соответствующими коллекторами транзисторов 1 и 2. Соответствующие кол- лекторы транзисторов 1 и 3 соединены с базой второго выходного транзистора 1 1 с инжекццоннь М питанием с весом инжектора 1,5 и коллектором второго промежуточного транзистора 12с инжекционным питанием с весом инжектора 0,5, база которого соединена с соответствующими коллекторами транзисторов 2 и 3. Коллекторы транзисторов 9 и 11 соединены соответствен- но с первым 13 и вторым 14 выходами номера неисправного блока.

MaжopитapньD элемент И Л типа работает следующим образом.

Для выполнения заданных функциз ; мажоритарный элемент реализован в арифметическом базисе, для которого выходная функция F на выходе 8 и функции , номера неисправного блока на выходах 13 и 14 имеют следующий вид;

F Р, (FJ, + F, + Fji 2);(1)

1 (0 + F,- 1) + РЗ (FO + + F, ь. 2) - Р,РЗ;(2)

М, 1 (Fo + F П + PjCF + + FI 2)- ,(3)

где Р,Р,Р - пороговые функции арифмической суммы входных аргументов FJJ , F, , F по порогу два; Р,Р - пороговые функции

арифметической суммы аргументов F, F, , F, по порогу один;

F., F ,F - сигналы на входах 4 - 6;

(-) арифметическая операция вычитания, котора (как это следует из правых частей выражений (3) и (2)) заменена Z-операцией, что позволяет реализовать предлагаемую схему с меньшими аппаратурным затратами.

Согласно соотношениям (1) - (3) в базы транзисторов 1 - 3, которые работают в режиме токовых повторителей с когэффициентами передачи по каждому из коллекторов, равному единице, инжектируется по одному дискрету тока, п базы промежуточных транзисторов 10 и 12, которьге реализуют пороговые функции Р,2 , Р, сог ласно выражениям (2) и (3), инжектируется половина дискрета тока (0,51), в базы выходных TpairjHCTOpoB 7, 9 и 11, которые реализуют функции соответственно Р., РЗ 5 инжектируется полтора дискре тп тока (1,51),

В предлагаемом элементе используется принцип функционально-схематической itiHTerpanHH, суть которог о заключается в совмещении в одном элементе выполнения нескольких функций. В данном случае транзисторы 10 и 12 выполняют функцию не только пороговых детекторов, но и инверторов, так же, как и транзисторы 9 и 11.

Мажоритарная схема два из трех реапизует выходную функцию F пра- вютьно, если хотя бы два из трех входящих сигналов идентичны, причем на выходах 13 и 14 устройства (М., , 1 ) указывается, какой из входных сигналов не совпадает с двумя другими. Ргк смотрим работу схемы при F

F, 0.

В ТОМ случае транзисторы 1 - 3 закрыты, поэтому через их коллекторы не отГ Ираются токи, инжектируемые в базы транзисторов 7, 10 и 12.

Траизш-торы , 10 и 12 нагьпиены (F 0), что принодит к закрытию транзисторов 9 и 11 М,, М, 1, т.е. все три ПХ1 ЛИ| 1Х сш иггча pamn.i между собой (неиспрапного бдока нет).

При Fg F, F 1, транзисторы 2 и 3 открыты и каждый отбирает через свои коддекторы по одному дискрету тока, а с базы транзистора 7 - три дискрета тока. Сдедовате.чьно, транзисторы , 9 - 12 закрыты: F 1, Мд 1 (1еиснравного блока нет).

о

F, о, F 1 транзисто

При

ры 2 и 1 закрыты, а транзистор 3 отбирает через свои кодлекторы один дискрет тока с баз транзисторов , 11 и 12. Поэтому транзистор 12 закрыт (в его базу инжектируется 0,51), а транзистор 11 открывается (МJ 0), так как с базы транзистора 10 ток не отбирается, он открывается и своим коллектором закрывает транзистор 9 (Мg 1). С базы транзистора отбирается один дискрет тока, что недостаточно для его задирания (F 0), т.е. на выходах 13 и 14 имеем комбинацию И, О, fо что говорит о неисправности третр его блока (сигнал до шине F).

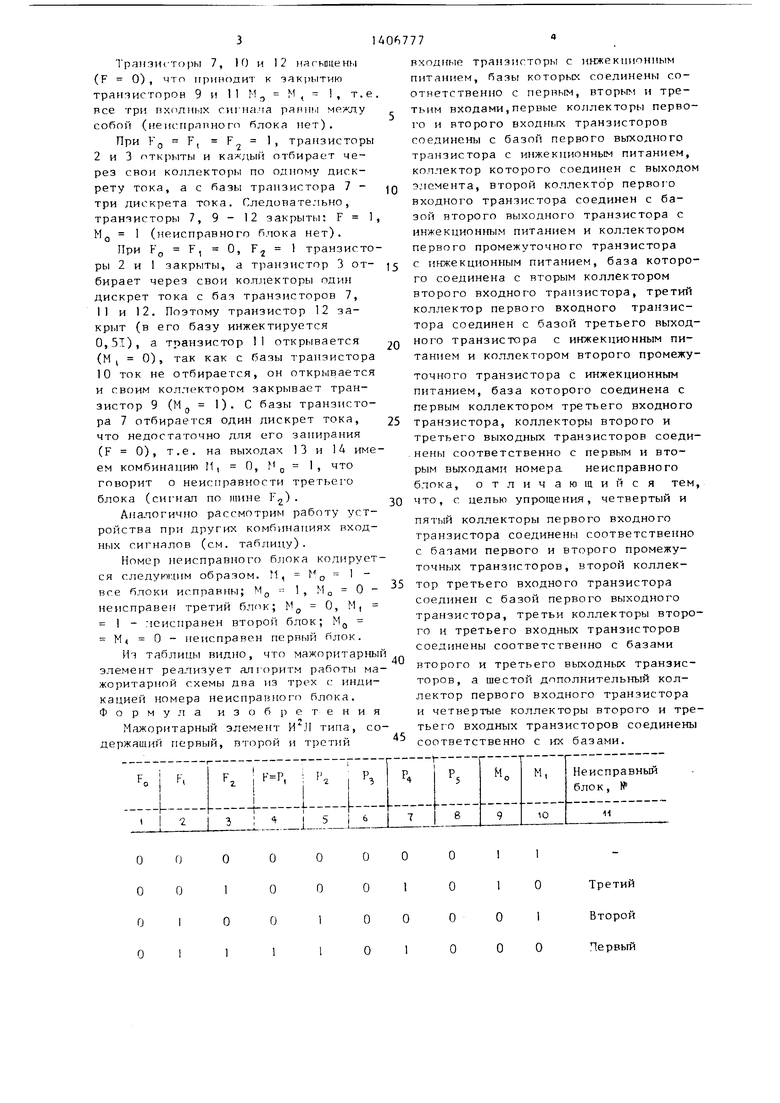

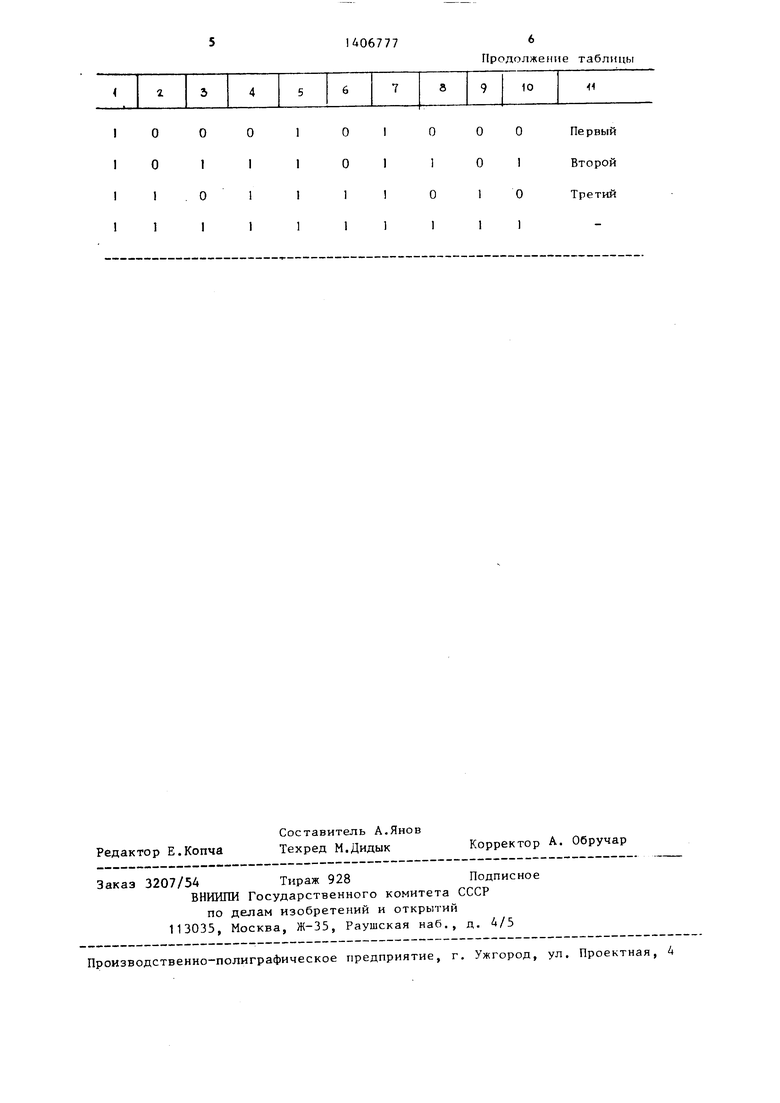

Аналогично рассмотрим работу устройства при других комбинациях входных сигналов (см. таблицу).

Номер неисправного блока кодируется следующим образом. М, о 1 - все блоки исправны; М - 1, MQ О - неисправен третий блок; М О, 1 - мсисправен второй блок; М О - неисправен первый блок.

Ит таблицы вид)Ю, что мажоритарны эдемент реализует алгоритм работы мажоритарной схемы дна из трех с индикацией номера неисправного бдока. Формула изобретения

Мажоритарный элемент И Л типа, содержащий первый, второй и третий

MO

5

0

5

0

0

5

входные транзисторы с инжекнионным питанием, базы которьк соединены соответственно с первым, вторым и третьим входами,первые коллекторы первого и второго входных транзисторов соединены с базой первого выходного транзистора с инжекционным питанием, коллектор которого соединен с выходом элемента, второй коллектор первого входного транзистора соединен с базой второго выходного транзистора с инжекционным питанием и коддектором первого промежуточного транзистора с инжекционным питанием, база которого соединена с вторым коллектором второго входного транзистора, третий коллектор первого входного транзистора соединен с базой третьего выходного транзистора с инжекционным питанием и коллектором второго промежуточного транзистора с инжекционным питанием, база которого соединена с первым коллектором третьего входного транзистора, коллекторы второго и третьего выходных транзисторов соединены соответственно с первым и вторым выходами номера неисправного блока, отличающийся тем, что, с целью упрощения, четвертый и

пятый кодлекторы первого входного транзистора соединены соответственно с базами первого и второго промежуточных транзисторов, второй кодлек- тор третьего входного транзистора соединен с базой первого выходного транзистора, третьи коллекторы второго и третьего входных транзисторов соединены соответственно с базами

второго и третьего выходных транзисторов, а шестой дополнительный коллектор первого входного транзистора и четвертые коллекторы второго и тре- тьег О входных транзисторов соединены соответственно с lix базами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Схема контроля на четность И @ Л типа | 1985 |

|

SU1269253A1 |

| Схема контроля на четность И @ Л-типа | 1988 |

|

SU1525906A1 |

| Четырехразрядный преобразователь двоичного кода в циклический код Грея | 1986 |

|

SU1388993A1 |

| Тактируемый JK-триггер И @ Л-типа | 1987 |

|

SU1422367A1 |

| Интегральный четырехзначный D-триггер | 1986 |

|

SU1338012A1 |

| Инжекционный динамический элемент | 1980 |

|

SU953731A1 |

| Одноразрядный сумматор-вычитатель | 1987 |

|

SU1424013A1 |

| Устройство для приема и передачи информации | 1988 |

|

SU1510095A1 |

| Одноразрядный сумматор | 1988 |

|

SU1522193A1 |

| Входной транслятор И @ Л-типа | 1984 |

|

SU1202049A1 |

Изобретение может быть использовано в БИС на основе инжекционной логики. Цель изобретения - упрощение мажоритарного элемента И Л типа. Устройство содержит транзисторы 1-3 с инжекционным питанием, выходные транзисторы 7, 9 и 11 и промежуточные транзисторы 10 и 12. Предложенное функциональное соединение элементов схемы позволяет реализовать алгоритм работы два из трех с индикацией номера неисправного блока. 1 ип., I табл.

ОО

ОО

О1

О1

Третий Второй Первый

Продолжение таблицы

| Разработка и исследование интегральных схем на новых типах полупроводниковых приборов | |||

| Руководство по схемотехническому проектированию цифровых БИС и сверх БИС на базе интегральной инжекционной логики | |||

| Отчет по НИР | |||

| - № ГР 75026315, инв | |||

| № Б801544 | |||

| М., 1979, с | |||

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

| Приспособление для плетения проволочного каркаса для железобетонных пустотелых камней | 1920 |

|

SU44A1 |

Авторы

Даты

1988-06-30—Публикация

1986-12-02—Подача