Изобретение относится к оптоэлектронике к разделам считывания, обработки и хранения оптической информации и может быть использовано в интегральных фотоматричных устройствах, предназначенных для фотоэлектрического преобразования, считывания, хранения, логико-арифметической обработки оптических сигналов.

Известны фотоприемные ячейки [1,2,3,4] предназначенные для сравнения, двух оптических сигналов путем их дифференциального фотоэлектрического преобразования. Результат этого сравнения представляется на электрических выходах ячейки либо в форме аналогового электрического сигнала [1 и 2] либо в форме электрических сигналов нормированного уровня [3 и 4]

Наиболее близким по технической сущности и признакам к предлагаемому устройству является фотоприемная ячейка [3] содержащая два фотоприемника и выполненная по МДП-технологии. Кроме фотоприемников ячейка содержит дифференциальный усилитель и выходной каскад с функциями высокочувствительного компаратора с ячейкой памяти (триггера-защелки). Фотоприемники ячейки представляют собой фотодиоды, образованные р-n переходами между диффузионными областями МДП-транзисторов (истоками и стоками) и подложкой. Фотодиоды подключены к затворам усилительных транзисторов дифференциального усилителя и через первый и второй транзисторы стирания к источнику напряжения смещения. Управляются ключевые транзисторы стирания сигналами стирания по затворам, подключенным к шине стирания. Ток в дифференциальном усилителе задается первым токостабилизирующим транзистором, затвор которого подключен к управляющей шине. К выходу дифференциального усилителя подключен каскад, представляющий дифференциальный усилитель-компаратор (триггер-защелку), содержащий усилительные, нагрузочные, второй токостабилизирующий транзистор, ключевые транзисторы с цепочкой на входе из последовательно соединенных канала третьего ключевого транзистора стирания и запоминающего конденсатора.

Обладая рядом преимуществ, устройство способно обеспечить определенный высокий уровень таких важнейших технических характеристик, как дифференциальная фоточувствительность при наличии светового фона, быстродействие и др. Однако уровень этих характеристик для прототипа имеет свои ограничения. Так ограничение пороговой чувствительности обусловлено влиянием следующих факторов: при формировании сигнала на входе триггера-защелки реально существующая паразитная емкость между затвором третьего транзистора стирания и его стоком (истоком), подключенным к запоминающему конденсатору, задним фронтом сигнала стирания искажает полезный сигнал на входе триггера-защелки, что напрямую ограничивает пороговую чувствительность такой ячейки; технологический разброс пороговых напряжений входных усилительных транзисторов дифференциального усилителя-компаратора ячейки, который реально может составлять несколько сот милливольт, также напрямую ограничивает пороговую чувствительность. Ограничения пороговой чувствительности ячейки приводят к понижению ее реального быстродействия, поскольку фотоприемники ячейки функционируют в режиме накопления (т. е. интегрирования преобразуемых оптических сигналов), и поэтому для обеспечения надежного функционирования ячейки приходится разменивать понижение ее пороговой чувствительности на увеличение времени накопления (т.е. быстродействия фотоэлектрического преобразования). Существенным недостатком известного устройства является и то, что уровни выходных информационных сигналов (т.е. напряжений на выходах триггера-защелки), а также требуемые для функционирования ячейки уровни управляющих сигналов (т.е. стирания и записи) определяются напряжением на шине питания дифференциального усилителя ячейки. В то же время триггер-защелка, являясь составной частью фотоприемной ячейки, представляет по существу элемент цифровой логики, для успешного взаимодействия которого с внешними по отношению к ячейке устройствами весьма желательно иметь стандартные уровни управляющих и выходных сигналов.

Указанные недостатки известного устройства устраняются в предлагаемом устройстве.

Существенная новизна и оригинальность предлагаемого технического решения достигается введением в состав фотоприемной ячейки дополнительных элементов, которые в связи с остальными элементами ячейки позволяют добиться новых свойств: повышения пороговой чувствительности за счет компенсации на каждом такте работы ячейки как начального разбаланса дифференциального усилителя в условиях действия паразитных связей между элементами, так и влияния технологического разброса пороговых напряжений входных усилительных транзисторов триггера-защелки; повышения устойчивости к влиянию неидентичности электрических параметров запоминающих конденсаторов и паразитных емкостей ключевых транзисторов за счет дифференциальной схемы включения указанных элементов, а также улучшения эксплуатационных параметров ячейки (энергопотребления, возможности использования стандартных уровней управляющих и выходных сигналов) за счет возможности разнесения, а следовательно, и соответствующего выбора, питания дифференциального усилителя и триггера-защелки ячейки от отдельных источников. И, если известно [4] отличное от предлагаемого как по исполнению, так и по эффективности действия, техническое решение компенсации на каждом такте работы ячейки начального разбаланса дифференциального усилителя в условиях действия паразитных связей между элементами, то компенсация технологического разброса пороговых напряжений входных усилительных транзисторов используемого в ячейке триггера-защелки предлагается впервые.

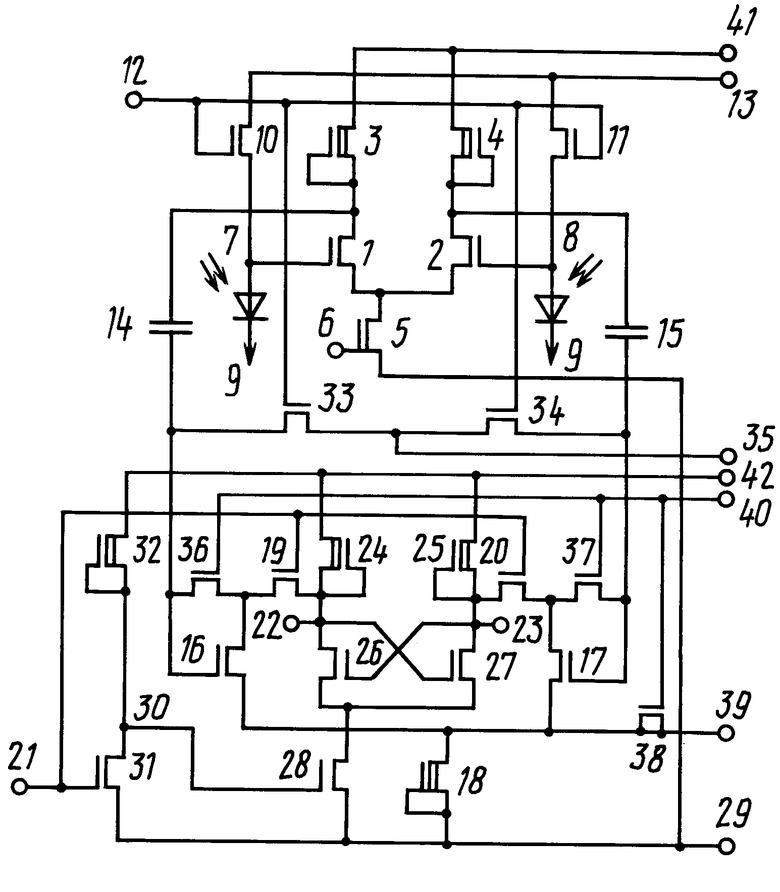

На чертеже представлена схема фотоприемного интегрального элемента памяти.

Фотоприемный интегральный элемент памяти содержит дифференциальный усилитель, состоящий из первого и второго усилительных транзисторов 1 и 2, первого и второго нагрузочных транзисторов 3 и 4, первого токостабилизирующего транзистора 5, управляемого от задающей режим усилителя шины 6, фотодиоды 7 и 8, подключенные к затворам усилительных транзисторов 1, 2 и к подложке 9, первый и второй ключевые транзисторы стирания 10 и 11, затворы которых подключены к шине стирания 12, стоки к источнику смещения фотодиодов 13, а истоки соответственно к затворам усилительных транзисторов 1 и 2. Сток усилительного транзистора 1 через первый запоминающий конденсатор 14, а сток усилительного транзистора 2 через второй запоминающий конденсатор 15 соединены соответственно с затворами третьего и четвертого усилительных транзисторов 16 и 17 дополнительного дифференциального усилителя, являющегося составной частью триггера-защелки. Истоки третьего и четвертого усилительных транзисторов 16 и 17 дополнительного дифференциального усилителя соединены со стоком второго токостабилизирующего транзистора 18 этого усилителя. Стоки третьего и четвертого усилительных транзисторов 16 и 17 дополнительного дифференциального усилителя соединены соответственно с истоками первого и второго ключевых транзисторов записи 19 и 20, затворы которых подключены к шине записи 21, а стоки, являющиеся первым и вторым информационными выходами 22 и 23 дополнительного дифференциального усилителя и фотоприемной ячейки (триггера-защелки), соответственно к истоку и затвору третьего и истоку и затвору четвертого нагрузочных транзисторов 24 и 25 этого усилителя. Сток пятого и затвор шестого усилительных транзисторов 26 и 27 подключены к первому выходу 22 фотоприемной ячейки, сток шестого и затвор пятого усилительных транзисторов 27, 26 подключены ко второму выходу 23 фотоприемной ячейки. Истоки пятого и шестого усилительных транзисторов 26 и 27 соединены со стоком третьего транзистора записи 28, исток которого подключен к общей шине 29, а затвор к выходу 30 инвертора сигнала на шине записи 22. Инвертор сигнала записи содержит первый ключевой и пятый нагрузочный транзисторы 31, 32. Истоки третьего и четвертого ключевых транзисторов стирания 33, 34 подключены соответственно к затворам третьего и четвертого усилительных транзисторов 16, 17. Стоки третьего и четвертого ключевых транзисторов стирания 33, 34 соединены с шиной 35 источника смещения входов дополнительного дифференциального усилителя, а затворы этих транзисторов соединены с шиной стирания 12. Сток и исток второго ключевого транзистора 36 подключены соответственно к стоку и затвору третьего усилительного транзистора 16. Сток и исток третьего ключевого транзистора 37 соединены соответственно со стоком и затвором четвертого усилительного транзистора 17. Сток и исток четвертого ключевого транзистора 38 подключены соответственно к шине источника смещения балансировки 39 и истокам усилительных транзисторов 16 и 17. Затворы второго, третьего и четвертого ключевых транзисторов 36, 37 и 38 соединены с шиной 40 балансировки. Исток первого токостабилизирующего транзистора 5, истоки и затвор второго токостабилизирующего транзистора 18, а также исток первого ключевого транзистора 31 соединены с общей шиной 29. Стоки первого и второго нагрузочных транзисторов 3, 4 дифференциального усилителя ячейки подключены к первой шине 41 питания. Стоки третьего и четвертого нагрузочных транзисторов 24 и 25 триггера-защелки, а также сток пятого нагрузочного транзистора 32 инвертора сигнала записи соединены со второй шиной питания 42.

Принцип работы устройства состоит в следующем.

По сигналу стирания с шины стирания 12 через открытые каналы ключевых транзисторов стирания 10 и 11 заряжаются до напряжения источника смещения 13 емкости фотодиодов 7 и 8. На выходах дифференциального усилителя (стоках усилительных транзисторов 1 и 2) устанавливается при этом напряжение вых0 начального разбаланса этого усилителя. Одновременно с зарядом емкостей фотодиодов происходит заряд емкостей запоминающих конденсаторов 14, 15 через открытые каналы ключевых транзисторов стирания 33 и 34 от источника смещения 35 входов усилительных транзисторов триггера-защелки и выходов дифференциального усилителя (стоков транзисторов 1 и 2).

При этом на затворах транзисторов 16 и 17 устанавливаются напряжения, равные напряжению источника смещения 35 входов триггера-защелки, а начальный разбаланс дифференциального усилителя запоминается на емкостях конденсаторов 14, 15 в виде разности напряжений на этих конденсаторах. По окончании сигнала стирания каналы транзисторов стирания 10, 11, 33, 34 запираются. Фотодиоды 7 и 8 оказываются обратно смещенными зарядами, запасенными их емкостями во время стирания, а на емкостях запоминающих конденсаторов 14 и 15 устанавливаются напряжения, разность которых равна вых0 в то время, как на входах дополнительного дифференциального усилителя напряжения остаются равными и близкими по величине напряжению смещения на шине 42. Благодаря симметрии емкостей запоминающих конденсаторов (их целесообразно по этой причине выполнять одинаковыми), а также параметров (в том числе и паразитных емкостей) ключевых транзисторов стирания 33 и 34 задний фронт импульса стирания не искажает полезного сигнала на входах триггера-защелки (разность напряжений на затворах транзисторов 16 и 17 по-прежнему сохраняется равной нулю). Тем самым вход компаратора (триггера-защелки) защищается от начального разбаланса дифференциального усилителя в условиях действия паразитных связей между элементами ячейки и на его вход поступает только полезный сигнал, соответствующий дифференциальной разности оптических сигналов, преобразуемых фотоприемниками ячейки.

В предлагаемом интегральном элементе памяти сигнал на входе триггера-защелки в отсутствие сигнала записи, когда транзисторы 19 и 20 заперты, подвергается дополнительной коррекции в соответствии с разбросом пороговых напряжений усилительных транзисторов 16 и 17. Для этой цели на затворы ключевых транзисторов 36, 37 и 38 подается по шине 40 сигнал балансировки (импульс напряжения), задний фронт которого задержан относительно заднего фронта сигнала стирания. Открытые каналы ключевых транзисторов 36 и 37 соединяют стоки и затворы усилительных транзисторов 16 и 17, у которых каналы сток-исток будут проводящими, если напряжение на стоках превышает напряжение на истоках на величину Uпор соответствующего транзистора.

В предлагаемом устройстве напряжение на истоках транзисторов 16 и 17 при наличии сигнала балансировки на шине 40 устанавливается через открытый канал ключевого транзистора 38 равным напряжению на шине смещения балансировки 39. Источниками напряжений на затворах транзисторов 16 и 17 будут заряды, запасенные емкостями запоминающих конденсаторов 14 и 15 во время стирания. Поэтому, если после стирания во время балансировки напряжения на затворах транзисторов 16 и 17 будут удовлетворять условиям U16 > Uпор16 + U39 U17 > Uпор17 + U39, где U16 и U17 напряжения на затворах транзисторов 16 и 17, Uпор16 и Uпор пороговые напряжения транзисторов 16 и 17, U39 напряжение на шине смещения балансировки, то запоминающие конденсаторы 14 и 15 будут разряжаться до тех пор, пока каналы сток-исток транзисторов 16 и 17 будут проводящими, т.е. пока имеют место упомянутые выше условия.

Таким образом, во время балансировки напряжения на затворах усилительных транзисторов 16 и 17 дополнительного дифференциального усилителя устанавливаются перед началом накопления в соответствии с напряжением на шине 39 и пороговыми напряжениями транзисторов 16 и 17, компенсируя тем самым разброс пороговых напряжений этих транзисторов и повышая дифференциальную чувствительность ячейки в целом.

Дополнительный дифференциальный усилитель, включающий третий и четвертый усилительные транзисторы 16 и 17, второй токостабилизирующий транзистор 18, нагрузочные транзисторы 24 и 25, соединенные последовательно с первым и вторым ключевыми транзисторами записи 19 и 20, образует вместе с пятым и шестым усилительными транзисторами 26 и 27, инвертором на транзисторах 31 и 32 и третьим транзистором записи 28 выходной каскад фотоприемной ячейки с функциями высокочувствительного компаратора с ячейкой памяти (триггера-защелки).

При отсутствии сигнала записи на шине 21 каналы ключевых транзисторов записи 19 и 20 заперты, а ключевой транзистор 28 открыт (выходным сигналом с выхода 30 инвертора сигнала записи). При этом конфигурация, состоящая из транзисторов 26, 27, 24, 25, образует статический триггер (транзистор 28 включает его питание), т.е. ячейку памяти с выходами 22 и 23. На время действия сигнала записи питание триггера отключается (канал транзистора 28 запирается), зато при замкнутых каналах ключевых транзисторов 19 и 20 из транзисторов 16, 17, 19, 20, 24, 25, 18 образуется конфигурация дифференциального усилителя, который усиливает дифференциальный сигнал на его входах (затворах транзисторов 16 и 17). Усиленный сигнал запоминается на паразитных емкостях выходов 22 и 23. По заднему фронту сигнала записи каналы транзисторов записи 19 и 20 запираются, а канал транзистора 28 открывается, происходит срабатывание триггера в соответствии со знаком напряжения, установившегося на его входах (выходах 22 и 23) перед концом сигнала записи. Таким образом производится компарирование сигнала дифференциального усилителя с фотодиодами на входах и запоминающими конденсаторами на выходах, его нормирование по уровню и запись в триггер.

Отсутствие на входном сигнале дополнительного дифференциального усилителя начального разбаланса первого каскада, коррекция этого сигнала в соответствии с разбросом пороговых напряжений входных усилительных транзисторов триггера-защелки повышает отношение сигнал/шум для фоточувствительной ячейки в целом, а следовательно, увеличивает ее пороговую чувствительность. Повышает ее устойчивость к действию технологического разброса параметров элементов, к наличию паразитных параметров и связей между элементами фотоприемной ячейки, а также неоднородностей, вносимых технологией производства и условиями эксплуатации. Наличие в предлагаемом устройстве между выходами дифференциального каскада и входами триггера-защелки запоминающих конденсаторов, т.е. отсутствие связи между каскадами по постоянному току, позволяет использовать для питания этих каскадов отдельные источники питания. Это позволяет выбирать режимы каскадов независимыми друг от друга, обеспечивая, например, требуемые уровни управляющих и выходных сигналов для ячейки независимыми от напряжения питания и режимов работы дифференциального каскада с фотоприемниками на входе.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2050600C1 |

| Фотоприемная ячейка | 1989 |

|

SU1619344A1 |

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Фотоприемная ячейка | 1989 |

|

SU1626261A1 |

| Фотоприемная ячейка | 1989 |

|

SU1619345A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Устройство считывания сигналов с фотоприемной матрицы инфракрасного излучения (варианты) | 2018 |

|

RU2688953C1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Оптоэлектронный элемент памяти | 1977 |

|

SU661608A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

Изобретение относится к оптоэлектронике, а именно к считыванию и хранению оптической информации. Повышение пороговой чувствительности достигается введением запоминающих конденсаторов между выходами дифференциального усилителя и входами триггера-защелки, смещение входов триггера-защелки на каждом такте работы ячейки с помощью ключевых транзисторов стирания и дополнительных ключевых транзисторов, осуществляющих при балансировке ячейки компенсацию влияния несимметрии пороговых напряжений входных усилительных транзисторов триггера-защелки на пороговую чувствительность ячейки. 1 ил.

ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ, содержащий первый усилительный транзистор, сток которого подключен к затвору второго усилительного транзистора и к затвору и истоку первого нагрузочного транзистора, сток второго усилительного транзистора и затвор первого усилительного транзистора соединены с затвором и истоком второго нагрузочного транзистора, истоки первого и второго усилительных транзисторов соединены со стоком первого ключевого транзистора записи, затвор которого подключен к стоку ключевого транзистора и к затвору и истоку третьего нагрузочного транзистора, третий и четвертый усилительные транзисторы, истоки которых соединены со стоком первого токостабилизирующего транзистора, стоки третьего и четвертого усилительных транзисторов подключены соответственно к истокам второго и третьего ключевых транзисторов записи, стоки которых соединены с затворами и истоками соответственно первого и второго нагрузочных транзисторов, затворы второго и третьего ключевых транзисторов записи и ключевого транзистора подключены к шине записи, стоки первого, второго и третьего нагрузочных транзисторов соединены с первой шиной питания, истоки ключевого транзистора и первого ключевого транзистора записи и исток и затвор первого токостабилизирующего транзистора подключены к общей шине, пятый и шестой усилительные транзисторы, стоки которых соединены с истоками и затворами соответственно четвертого и пятого нагрузочных транзисторов, истоки пятого и шестого усилительных транзисторов подключены к стоку второго токостабилизирующего транзистора, затвор которого соединен с управляющей шиной, исток с общей шиной, первый и второй фотодиоды, которые подключены к затворам соответственно пятого и шестого усилительных транзисторов и одноименными выводами к подложке, первый и второй ключевые транзисторы стирания, истоки которых соединены соответственно с первым и вторым фотодиодами, стоки с источником смещения фотодиодов, третий ключевой транзистор стирания, исток которого соединен с затвором третьего усилительного транзистора, затворы первого, второго и третьего ключевых транзисторов стирания подключены к шине стирания, запоминающий конденсатор, соединенный соответственно со стоком шестого усилительного транзистора и затвором четвертого усилительного транзистора, отличающийся тем, что в него введены четвертый ключевой транзистор стирания, второй запоминающий конденсатор, второй, третий и четвертый ключевые транзисторы, затворы которых подключены к шине балансировки, исток второго ключевого транзистора и затвор третьего усилительного транзистора через второй запоминающий конденсатор соединены со стоком пятого усилительного транзистора, исток третьего ключевого транзистора подключен к затвору четвертого усилительного транзистора и истоку четвертого ключевого транзистора стирания, стоки третьего и четвертого ключевых транзисторов соединены соответственно со стоками третьего и четвертого усилительных транзисторов, затвор четвертого ключевого транзистора стирания соединен с шиной стирания, а сток со стоком третьего ключевого транзистора стирания и шиной смещения затворов, исток четвертого ключевого транзистора подключен к стоку первого токостабилизирующего транзистора, а сток к шине смещения балансировки, стоки пятого и шестого нагрузочных транзисторов соединены с второй шиной питания.

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-09-10—Публикация

1993-01-15—Подача