Изобретение относится к автоматике и вычислительной технике и может быть использовано при тестовом контроле дискретных логических блоков в устройствах для контроля логических блоков, предполагающих наличие в их структуре эталонного эквивалента контролируемого логического блока как формирователя эталонных значений выходных реакций.

Цель изобретения - расширение функциональных возможностей за счет формирования тестов для последова-. тельностных блоков.

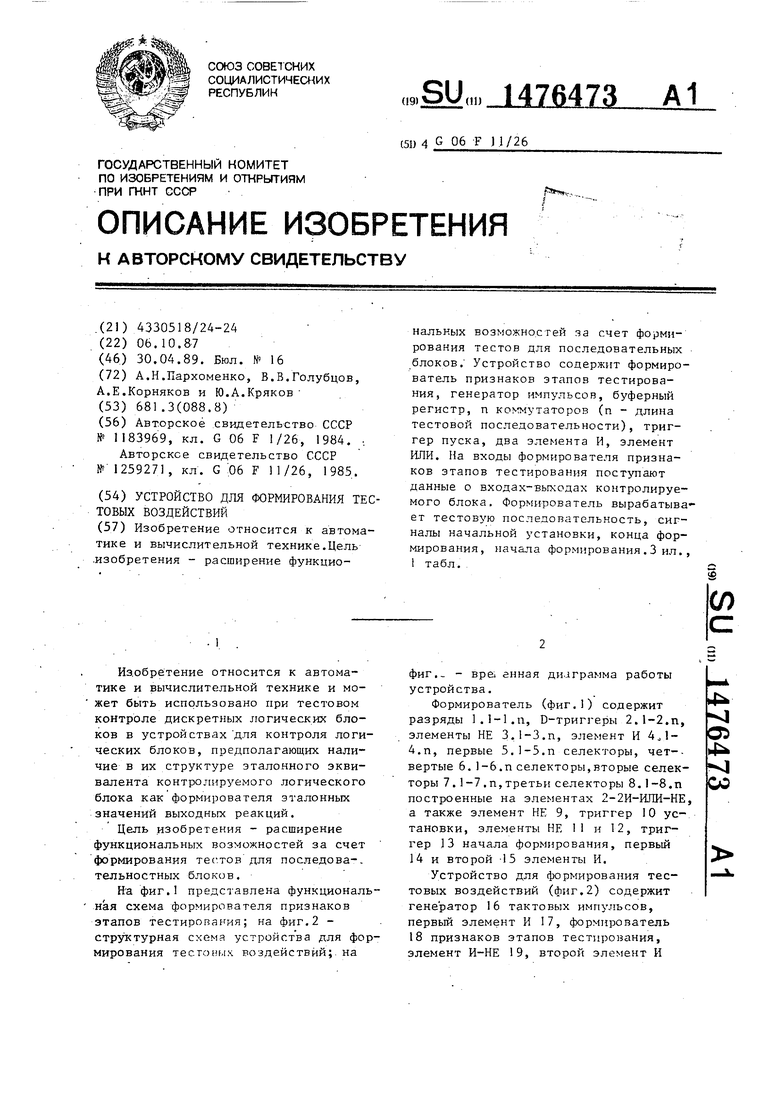

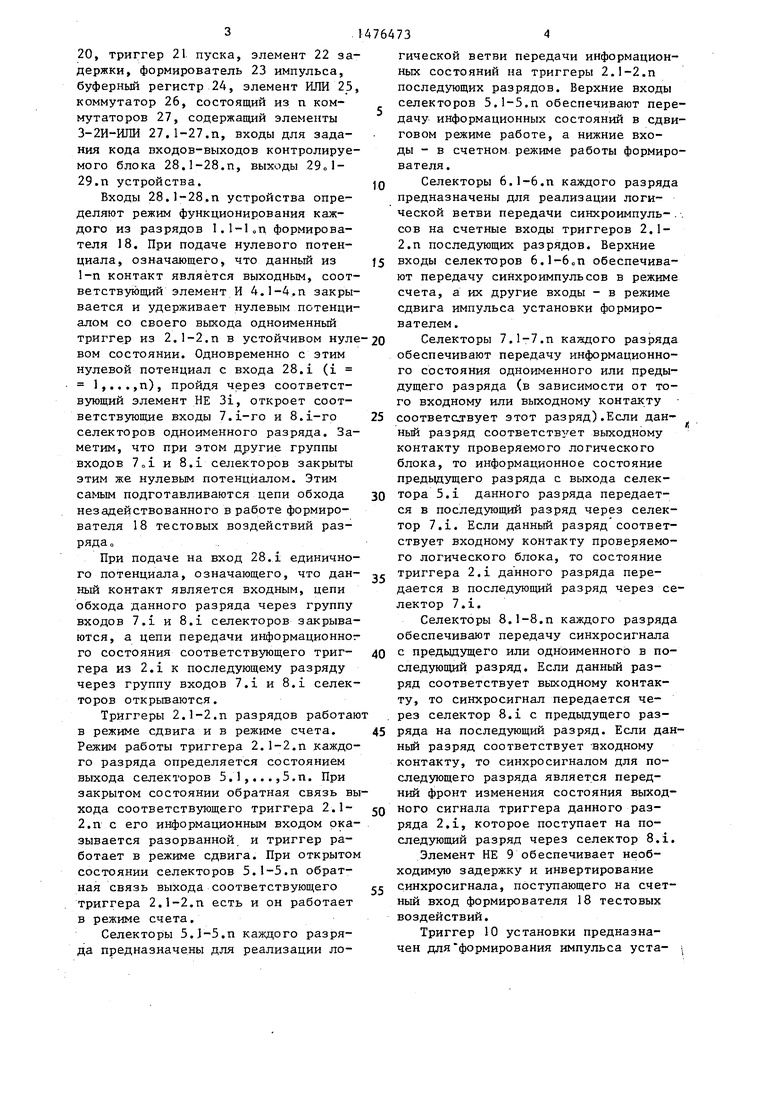

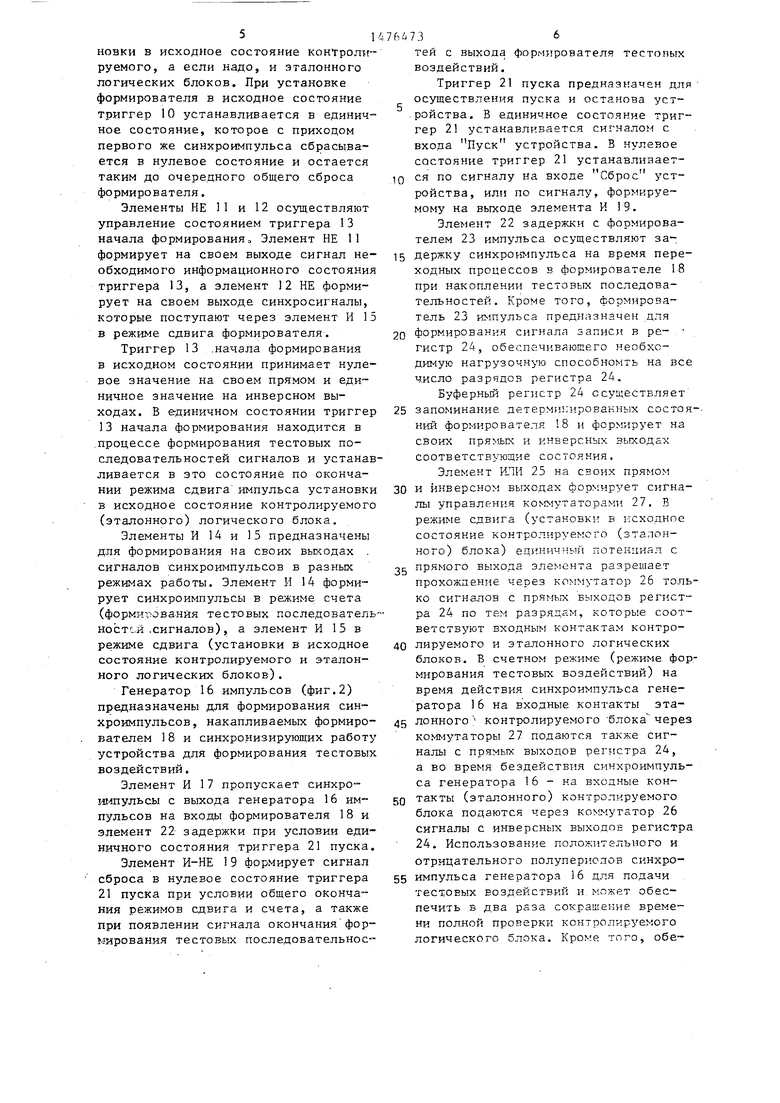

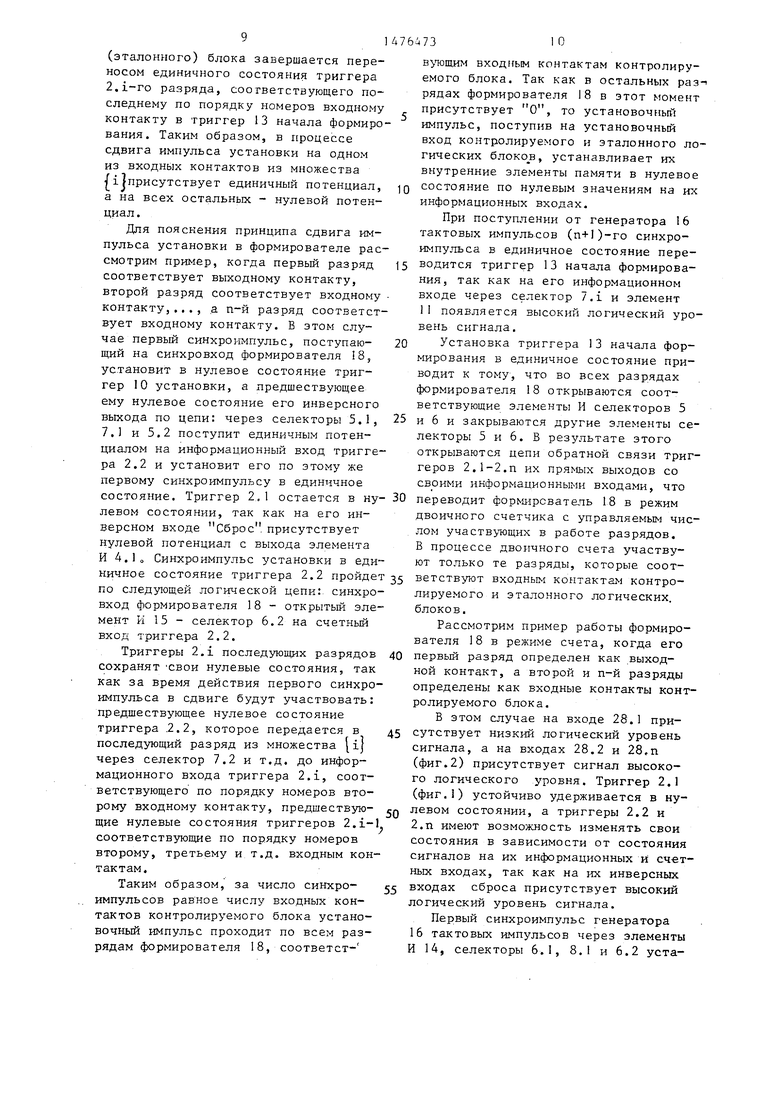

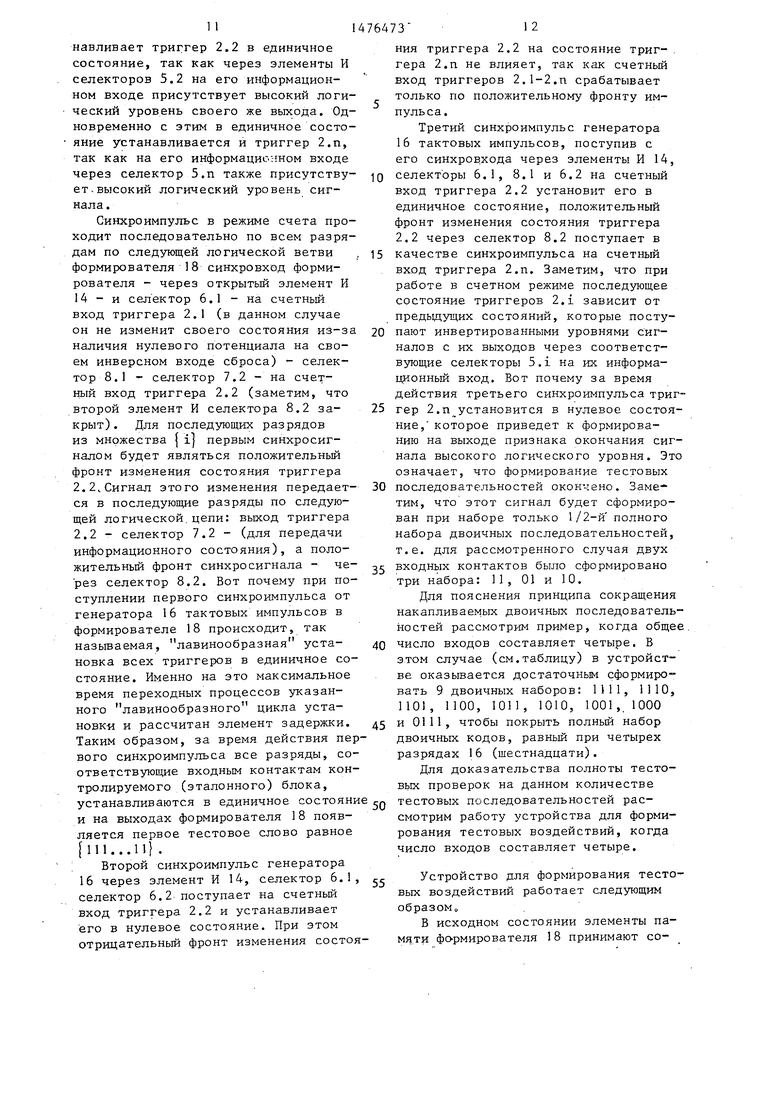

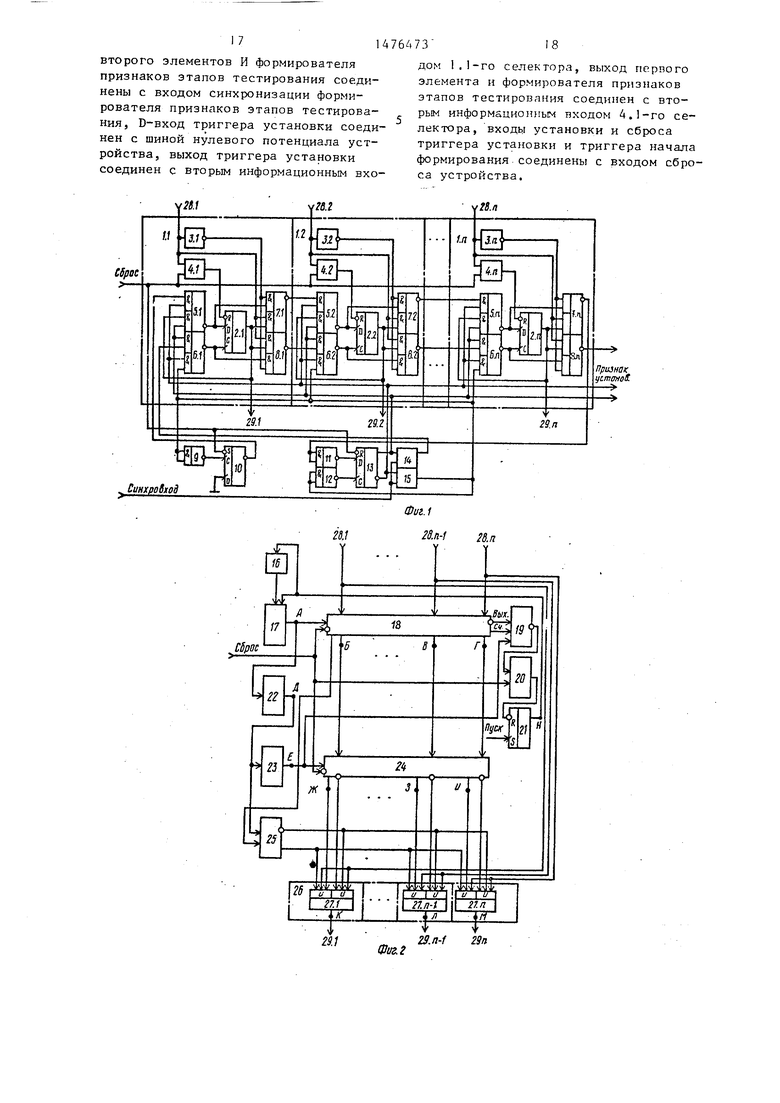

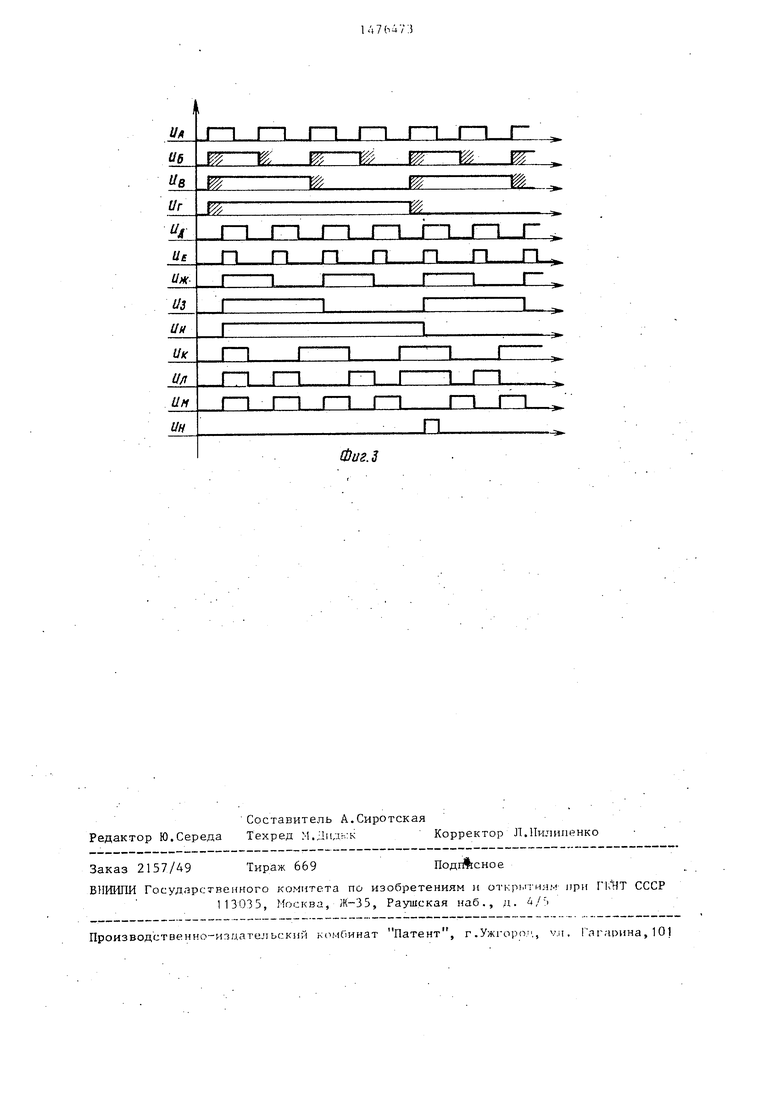

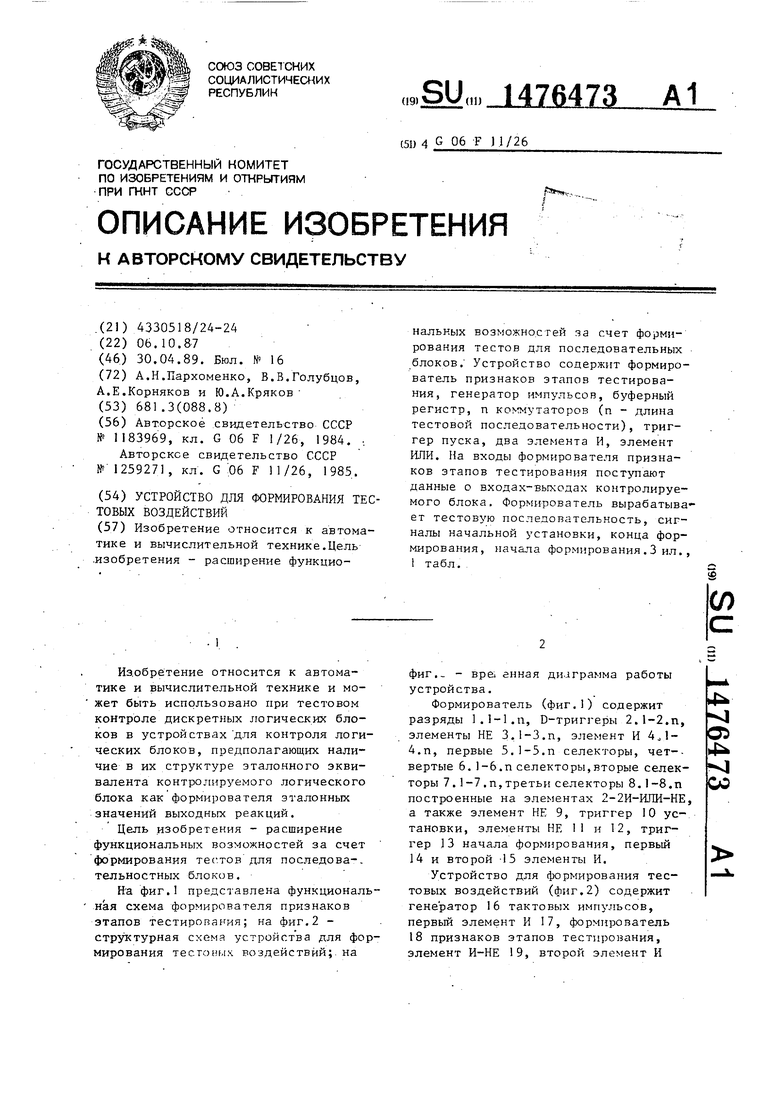

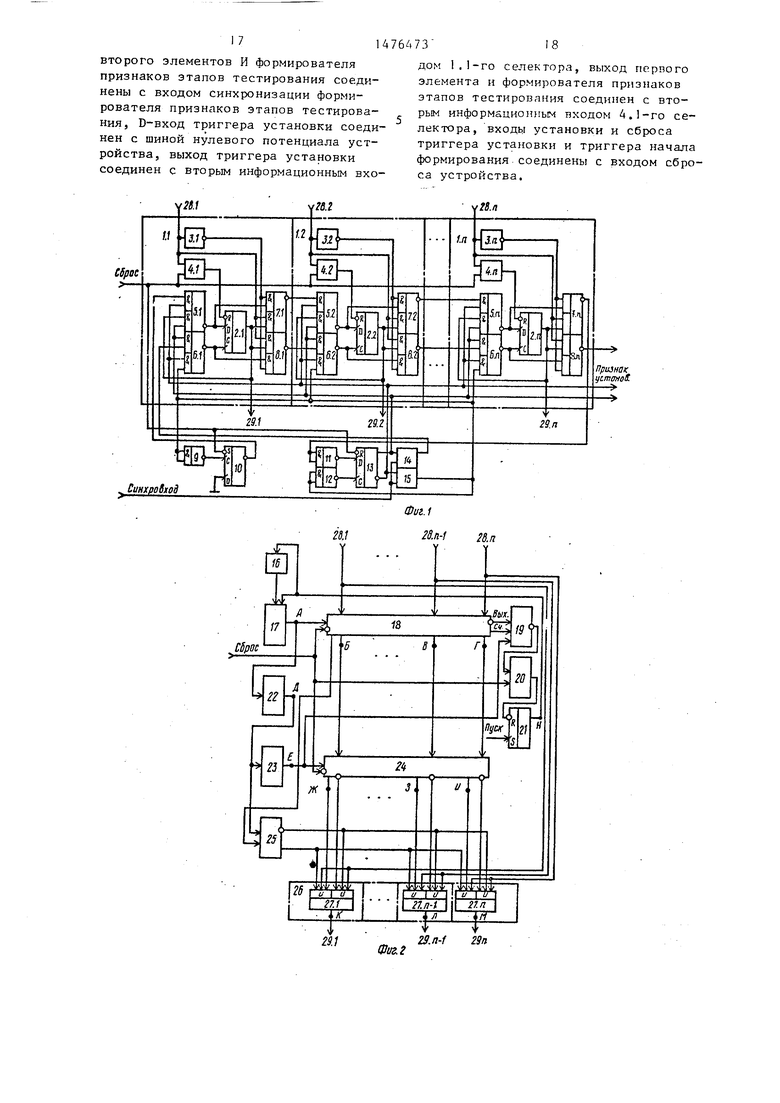

На фиг.1 представлена функциональная схема формирователя признаков этапов тестирования; на фиг.2 - структурная схемч устройства для формирования тестовых воздействий; на

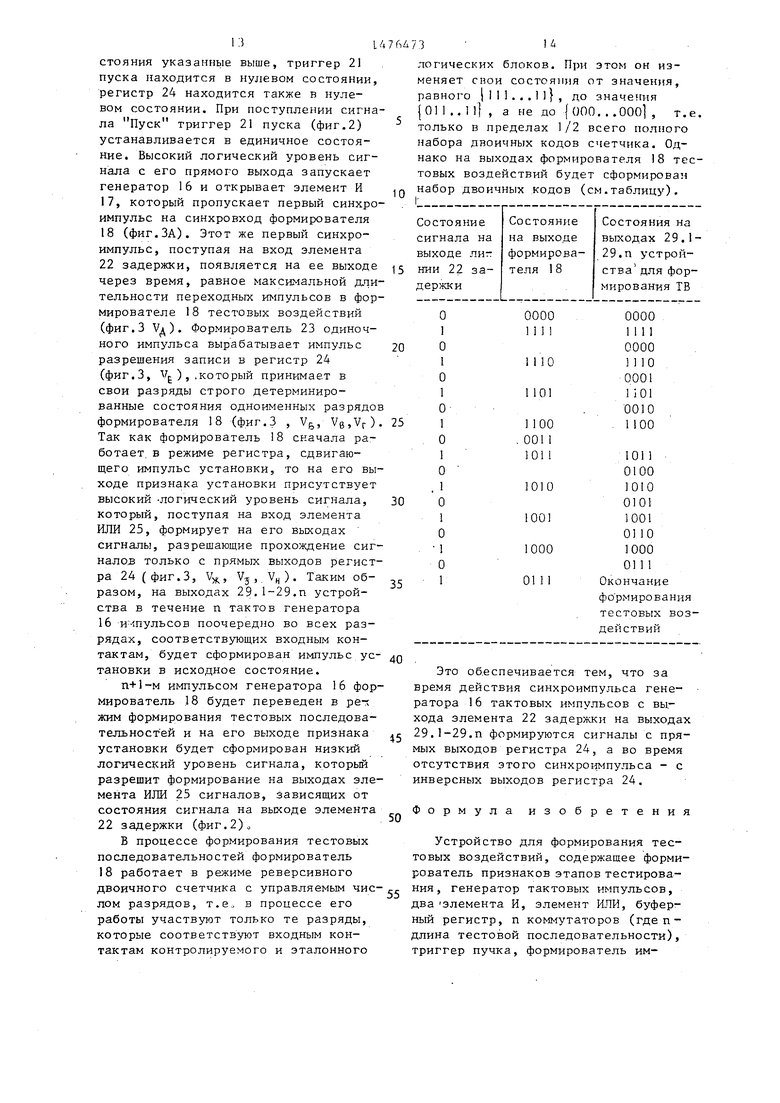

фиг,- - Bpei енная дидграмма работы устройства.

Формирователь (фиг.О содержит разряды 1.1-l.n, D-триггеры 2.1-2.П, элементы НЕ 3.1-З.п, элемент И 4,1- 4.п, первые 5.1-5.П селекторы, чет-- вертые 6. 1-6.п селекторы,вторые селекторы 7.1-7.п,третьи селекторы 8.1-8.п построенные на элементах 2-2И-ИЛИ-НЕ, а также элемент НЕ 9, триггер 10 установки, элементы НЕ 11 и 12, триггер 13 начала формирования, первый 14 и второй 15 элементы И.

Устройство для формирования тестовых воздействий (фиг.2) содержит генератор 16 тактовых импульсов, первый элемент И 17, формирователь 18 признаков этапов тестирования, элемент И-НЕ 19, второй элемент И

4 1

ОЭ 4

1

00

3

20, триггер 21 пуска, элемент 22 задержки, формирователь 23 импульса, буферный регистр 24, элемент ИЛИ 25 коммутатор 26, состоящий из п коммутаторов 27, содержащий элементы 3-2И-ИЛИ 27.1-27.п, входы для задания кода входов-выходов контролируемого блока 28.1-28.П, выходы 29.п устройства.

Входы 28.1-28.п устройства определяют режим функционирования каждого из разрядов 1.1-1„п формирователя 18. При подаче нулевого потенциала, означающего, что данный из 1-п контакт является выходным, соответствующий элемент И 4.1-4.П закрывается и удерживает нулевым потенциалом со своего выхода одноименный триггер из 2.1-2.П в устойчивом нул вом состоянии. Одновременно с этим нулевой потенциал с входа 28,i (i 1,...,п), пройдя через соответствующий элемент НЕ 31, откроет соответствующие входы 7.1-го и 8.1-го селекторов одноименного разряда. Заметим, что при этом другие группы входов 7„1 и 8.1 селекторов закрыты этим же нулевым потенциалом. Этим самым подготавливаются цепи обхода незадействованного в работе формирователя 18 тестовых воздействий разряда „

При подаче на вход 28.1 единичного потенциала, означающего, что данный контакт является входным, цепи обхода данного разряда через группу входов 7.1 и 8.1 селекторов закрываются, а цепи передачи информационно го состояния соответствующего триггера из 2.1 к последующему разряду через группу входов 7.1 и 8.1 селекторов открываются.

Селекторы 8.1-8.П каждого разряда обеспечивают передачу синхросигнала с предыдущего или одноименного в последующий разряд. Если данный разряд соответствует выходному контакту, то синхросигнал передается через селектор 8.1 с предыдущего разТриггеры 2.1-2.П разрядов работают в режиме сдвига и в режиме счета. 45 ряда на последующий разряд. Если дан- Режим работы триггера 2.1-2.П каждо- ный разряд соответствует входному го разряда определяется состоянием выхода селекторов 5.1,...,5.п. При закрытом состоянии обратная связь выхода соответствующего триггера 2.1- 50 2,п с его информационным входом окаконтакту, то синхросигналом для последующего разряда является передний фронт изменения состояния выходного сигнала триггера данного разряда 2.1, которое поступает на последующий разряд через селектор 8.1.

зывается разорванной и триггер работает в режиме сдвига. При открытом состоянии селекторов 5.1-5.П обратная связь выхода соответствующего триггера 2.1-2.П есть и он работает в режиме счета.

Селекторы 5.J-5.n каждого разряда предназначены для реализации ло

гической ветви передачи информационных состояний на триггеры 2.1-2.П последующих разрядов. Верхние входы селекторов 5.1-З.п обеспечивают передачу информационных состояний в сдвиговом режиме работе, а нижние входы - в счетном режиме работы формирователя.

Селекторы 6.1-б.п каждого разряда предназначены для реализации логической ветви передачи синхроимпульсов на счетные входы триггеров 2.1- 2.п последующих разрядов. Верхние

входы селекторов 6.1-60п обеспечивают передачу синхроимпульсов в режиме счета, а их другие входы - в режиме сдвига импульса установки формирователем .

Селекторы 7.1-7.П каждого разряда обеспечивают передачу информационного состояния одноименного или предыдущего разряда (в зависимости от того входному или выходному контакту

соответствует этот разряд).Если данный разряд соответствует выходному контакту проверяемого логического блока, то информационное состояние предыдущего разряда с выхода селектора 5.1 данного разряда передается в последующий разряд через селектор 7.1. Если данный разряд соответствует входному контакту проверяемого логического блока, то состояние

триггера 2.1 данного разряда передается в последующий разряд через селектор 7.1.

Селекторы 8.1-8.П каждого разряда обеспечивают передачу синхросигнала с предыдущего или одноименного в последующий разряд. Если данный разряд соответствует выходному контакту, то синхросигнал передается через селектор 8.1 с предыдущего раз

ряда на последующий разряд. Если дан- ный разряд соответствует входному

ряда на последующий разряд. Если дан- ный разряд соответствует входному

контакту, то синхросигналом для последующего разряда является передний фронт изменения состояния выходного сигнала триггера данного разряда 2.1, которое поступает на последующий разряд через селектор 8.1.

Элемент НЕ 9 обеспечивает необходимую задержку и инвертирование синхросигнала, поступающего на счетный вход формирователя 18 тестовых воздействий.

Триггер 10 установки предназначен для формирования импульса уста- (

5К

новки в исходное состояние контролируемого, а если надо, и эталонного логических блоков. При установке формирователя в исходное состояние триггер 10 устанавливается в единичное состояние, которое с приходом первого же синхроимпульса сбрасывается в нулевое состояние и остается таким до очередного общего сброса формирователя.

Элементы НЕ 11 и 12 осуществляют управление состоянием триггера 13 начала формирования. Элемент НЕ 11 формирует на своем выходе сигнал необходимого информационного состояния триггера 13, а элемент 12 НЕ формирует на своем выходе синхросигналы, которые поступают через элемент И 15 в режиме сдвига формирователя.

Триггер 13 начала формирования в исходном состоянии принимает нулевое значение на своем прямом и единичное значение на инверсном выходах. В единичном состоянии триггер 13 начала формирования находится в процессе формирования тестовых последовательностей сигналов и устанавливается в это состояние по окончании режима сдвига импульса установки в исходное состояние контролируемого (эталонного) логического блока.

Элементы И 14 и 15 предназначены для формирования на своих выходах сигналов синхроимпульсов в разных режимах работы. Элемент И 14 формирует синхроимпульсы в режиме счета (формиг-ования тестовых последовательностей .сигналов), а элемент И 15 в режиме сдвига (установки в исходное состояние контролируемого и эталонного логических блоков).

Генератор 16 импульсов (фиг.2) предназначены для формирования синхроимпульсов, накапливаемых формирователем 18 и синхронизирующих работу устройства для формирования тестовых воздействий,

Элемент И 17 пропускает синхроимпульсы с выхода генератора 16 импульсов на входы формирователя 18 и элемент 22 задержки при условии единичного состояния триггера 21 пуска.

Элемент И-НЕ 9 формирует сигнал сброса в нулевое состояние триггера 21 пуска при условии общего окончания режимов сдвига и счета, а также при появлении сигнала окончания формирования тестовых последовательносГ-4736

тей с выхода формирователя тестовых воздействий.

Триггер 21 пуска предназначен для осуществления пуска и останова устройства. В единичное состояние триггер 21 устанавливается сигналом с входа Пуск устройства. В нулевое состояние триггер 21 устанавлиаает0 ся по сигналу на входе Сброс устройства, или по сигналу, формируемому на выходе элемента И 19.

Элемент 22 задержки с формирователем 23 импульса осуществляют за

15 держку синхроимпульса на время переходных процессов в формирователе 18 при накоплении тестовых последовательностей, Кроме того, формирователь 23 импульса предназначен для

Q формирования сигнала записи в ре- гистр 2, обеспечивающего необходимую нагрузочную способномть на все число разрядов регистра 2А.

Буферный регистр 24 осуществляет

5 запоминание детерминированных состояний формирователя 8 и формирует на своих прямых и инверсных выходах соответствующие состояния.

Элемент ИЛИ 25 на своих прямом

0 и инверсном выходах формирует сигналы управления коммутаторами 27. В режиме сдвига (установки в исходное состояние контролирх емего (эталонного) блока) епиниччый потенциал с

g прямого выхода элемента разрешает прохождение через коммутатор 26 только сигналов с прямых выходов регистра 2 по тем разрядам, которые соответствуют входным контактам контроQ лируемого и эталонного логических

блоков. В счетном режиме (режиме формирования тестовых воздействий) на время действия синхроимпульса генератора 16 на входные контакты эта5 лонного1 контролируемого блока через коммутаторы 27 подаются также сигналы с прямых выходов регистра 24, а во время бездействия синхроимпульса генератора 16 - на входные конQ такты (эталонного) контролируемого блока подаются через кo 2 yгaтop 26 сигналы с инверсных ВЫХОППЕ регистра 24. Использование положительного и отрицательного полупернолов синхро5 импульса генератора 16 для подачи тестовых воздействий и может обес печить Б два раза сокращение времени полной проверки контролируемого логического блока. Кроме того, обеспечивается большая равномерность изменения сигналов на всех входных контактах контролируемого (эталонного) блока.

Формирователь 18 работает следующим образом.

После задания номеров входных (выходных) контактов блока нулевыми потенциалами на входах 28, которые соответствуют выходным контактам кон тролируемого блока, и единичными потенциалами, которые соответствуют входным контактам. Таким образом, для разрядов формирователя 18, которые будут соответствовать выходным контактам открывается селектор 7.1 и . Триггер 2.1 данного разряда удерживается в нулевом состоянии нулевым .потенциалом с выхода элемента И 4.1 одноименного разряда. Одновременно с этим закрыты другие элементы И входов селектора 7.1 и селектора 8.1. В результате этого создаются обходные цепи: через верхние элементы И селектора 7.1 - для передачи информационного состояния с предыдущего разряда в последующий, минуя данный разряд, через нижний элемент И селектора 8.1 - для прохождения сигнала синхроимпульса.

Для разрядов, соответствующих входным контактам, в формирователе 18 будут открыты нижние входы селектора 7Д и соответствующий элемент И селектора 8.1. Одновременно с этим будут закрыты другие элементы И селектора 7Д и соответствующие элемен1 ты И селектора 8.1. На инверсный R-вход Сброс соответствующего триг- гера 2.1 будет поступать единичный потенциал с выхода элемента И 4.1 од- поименного разряда, которьй позволит триггеру этого разряда принимать любые значения в зависимости от сигналов, подаваемых на его информацион1 ный и счетный входы. Таким образом, в разряде формирователя 18, соответствующем входному контакту контролируемого (эталонного) блока, информационные состояния предыдущего(щих) разряда(ов) будут влиять на триггер 4.1, а изменение его состояния будет передаваться в последующие разряды. Обходные цепи будут закрыты.

При поступлении нулевого потенциала установки в исходное состояние элементы памяти формирователя 18 принимают следующие состояния. Тригге7.738

ры 2„1-2.п всех разрядов устанавливаются в нулевое состояние. Триггер 10 устанавливается в единичное сос- тояние, а триггер 13 устанавливается в нулевое состояние.

При нулевом состоянии триггера 13 во всех разрядах формирователя 18 открываются соответствующие элементы Ю И селектора 5„1-5.п и 6.1-б.п, а закрываются другие элементы И этих селекторов. Таким образом, он подготовлен к работе в режиме регистра, сдвигающего импульс установки, так

15 как цепи обратной связи,каждого триггера 2.1-2.П между его выходом и информационным входом через элементы И селектора 5.1-Ь.п в этом случае закрыты и, следовательно, разорваны,

20 что и определяет работу каждого триггера в режиме сдвига, а не в режиме счета.

Сдвиг импульса установки в исходное состояние контролируемого (эта25 лонного) блока производится следующим образом

При поступлении на синхровход формирователя 18 первого синхроимпульса от генератора 16 через откры30 тьй в случае поступления сигнала Пуск высоким логическим уровнем сигнала, с выхода триггера 21 пуска элемент И 17, этот синхроситет проходит через открытый элемент И 15, элемент И-ИЛИ 9 () на счетный вход триггера 10 и через селекторы 6т1-6.п на счетные входы триггеров 2.1-2.п. В результате этого триггер 10 установки принимает нулевое со40 стояние (его информационный вход соединен с шиной нулевого потенциала) , триггер 2.1 (или 2.1, если первый разряд не является разрядом, входящим в множество { i, которое вклю45 чает в себя все разряды, определенные как входные контакты) устанавливается единичный потенциал, который поступает по следующей логической цепи: инверсный выход триггера

сп 10 - первый элемент И селектора 5.1 - информационный вход триггера 2.1 селектора 7.1.

Вторым синхроимпульсом единичное состояние будет сдвинуто в следую55 щий разряд на множества 1, соответствующий по порядку номеров второму входному контакту.

Цикл сдвига импульса установки в исходное состояние контролируемого

35

9

(эталонного) блока завершается переносом единичного состояния триггера 2.1-го разряда, соответствующего последнему по порядку номеров входному контакту в триггер 13 начала формирования. Таким образом, в процессе сдвига импульса установки на одном из входных контактов из множества Јi)присутствует единичный потенциал, а на всех остальных - нулевой потенциал.

Для пояснения принципа сдвига импульса установки в формирователе рассмотрим пример, когда первый разряд соответствует выходному контакту, второй разряд соответствует входному контакту,..., а n-й разряд соответствует входному контакту. В этом случае первый синхроимпульс, поступаю- щий на синхровход формирователя 18, установит в нулевое состояние триггер 10 установки, а предшествующее ему нулевое состояние его инверсного выхода по цепи: через селекторы 5.1, 7.1 и 5.2 поступит единичным потенциалом на информационный вход триггера 2.2 и установит его по этому же первому синхроимпульсу в единичное состояние. Триггер 2,1 остается в ну- левом состоянии, так как на его инверсном входе Сброс присутствует нулевой потенциал с выхода элемента И 4.1 о Синхроимпульс установки в единичное состояние триггера 2.2 пройдет по следующей логической цепи: синхровход формирователя 18 - открытый элемент И 15 - селектор 6.2 на счетньй вход триггера 2.2.

Триггеры 2.1 последующих разрядов сохранят свои нулевые состояния, так как за время действия первого синхроимпульса в сдвиге будут участвовать: предшествующее нулевое состояние триггера 2.2, которое передается в последующий разряд из множества ij через селектор 7.2 и т.д. до информационного входа триггера 2.1, соответствующего по порядку номеров второму входному контакту, предшествую- щие нулевые состояния триггеров 2.1-1 соответствующие по порядку номеров второму, третьему и т.д. входным контактам.

Таким образом, за число синхро- импульсов равное числу входных контактов контролируемого блока установочный импульс проходит по всем разрядам формирователя 18, соответст

О

вующим входным контактам контролируемого блока. Так как в остальных раз рядах формирователя 18 в этот момент присутствует О, то установочный импульс, поступив на установочный вход контролируемого и эталонного логических блоков, устанавливает их внутренние элементы памяти в нулевое состояние по нулевым значениям на их информационных входах.

При поступлении от генератора 16 тактовых импульсов (п+1)-го синхроимпульса в единичное состояние переводится триггер 13 начала формирования, так как на его информационном входе через селектор 7.1 и элемент II появляется высокий логический уровень сигнала.

Установка триггера 13 начала формирования в единичное состояние приводит к тому, что во всех разрядах формирователя 18 открываются соответствующие элементы И селекторов 5 и 6 и закрываются другие элементы селекторы 5 и 6. В результате этого открываются цепи обратной связи триггеров 2.1-2.П их прямых выходов со своими информационными входами, что переводит формирователь 18 в режим двоичного счетчика с управляемым числом участвующих в работе разрядов. В процессе двоичного счета участвуют только те разряды, которые соответствуют входным контактам контролируемого и эталонного логических, блоков.

Рассмотрим пример работы формирователя 18 в режиме счета, когда его первый разряд определен как выходной контакт, а второй и n-й разряды определены как входные контакты контролируемого блока.

В этом случае на входе 28.1 присутствует низкий логический уровень сигнала, а на входах 28.2 и 28,п (фиг.2) присутствует сигнал высокого логического уровня. Триггер 2.1 (фиг.1) устойчиво удерживается в нулевом состоянии, а триггеры 2.2 и 2.п имеют возможность изменять свои состояния в зависимости от состояния сигналов на их информационных и счетных входах, так как на их инверсных входах сброса присутствует высокий логический уровень сигнала.

Первый синхроимпульс генератора 16 тактовых импульсов через элементы И 14, селекторы 6.1, 8.1 и 6.2 устанавливает триггер 2.2 в единичное состояние, так как через элементы И селекторов 5.2 на его информационном входе присутствует высокий логический уровень своего же выхода. Одновременно с этим в единичное состояние устанавливается и триггер 2.п, так как на его информационном входе через селектор 5.п также присутству- ет-высокий логический уровень сигнала.

Синхроимпульс в режиме счета проходит последовательно по всем разрядам по следующей логической ветви формирователя 18 синхровход формирователя - через открытый элемент И 14 - и селектор 6.1 - на счетный вход триггера 2.1 (в данном случае он не изменит своего состояния из-за наличия нулевого потенциала на своем инверсном входе сброса) - селектор 8.1 - селектор 7.2 - на счетный вход триггера 2.2 (заметим, что второй элемент И селектора 8.2 за- крыт). Для последующих разрядов из множества i первым синхросигналом будет являться положительньй фронт изменения состояния триггера 2.2,Сигнал этого изменения передает- ся в последующие разряды по следующей логической цепи: выход триггера 2.2 - селектор 7.2 - (для передачи информационного состояния), а положительньй фронт синхросигнала - че- рез селектор 8.2. Бот почему при поступлении первого синхроимпульса от генератора 16 тактовых импульсов в формирователе 18 происходит, так называемая, лавинообразная уста- новка всех триггеров в единичное состояние. Именно на это максимальное время переходных процессов указанного лавинообразного цикла установки и рассчитан элемент задержки. Таким образом, за время действия первого синхроимпульса все разряды, соответствующие входным контактам контролируемого (эталонного) блока, устанавливаются в единичное состояни и на выходах формирователя 18 появляется первое тестовое слово равное fill...11} .

Второй синхроимпульс генератора 16 через элемент И 14, селектор 6.1, селектор 6.2 поступает на счетный вход триггера 2.2 и устанавливает его в нулевое состояние. При этом отрицательный фронт изменения состояния триггера 2.2 на состояние триггера 2.п не влияет, так как счетный вход триггеров 2.1-2.П срабатывает только по положительному фронту импульса.

Третий синхроимпульс генератора 16 тактовых импульсов, поступив с его синхровхода через элементы И 14, селекторы 6.1, 8.1 и 6.2 на счетный вход триггера 2.2 установит его в единичное состояние, положительный фронт изменения состояния триггера 2.2 через селектор 8.2 поступает в качестве синхроимпульса на счетный вход триггера 2.п. Заметим, что при работе в счетном режиме последующее состояние триггеров 2.1 зависит от предыдущих состояний, которые поступают инвертированными уровнями сигналов с их выходов через соответствующие селекторы 5.1 на их информационный вход. Вот почему за время действия третьего синхроимпульса триггер 2.установится в нулевое состояние, которое приведет к формированию на выходе признака окончания сигнала высокого логического уровня. Эт означает, что формирование тестовых последовательностей окончено. Заметим, что этот сигнал будет сформирован при наборе только 1/2-й полного набора двоичных последовательностей, т.е. для рассмотренного случая двух входных контактов было сформировано три набора: И, 01 и 10.

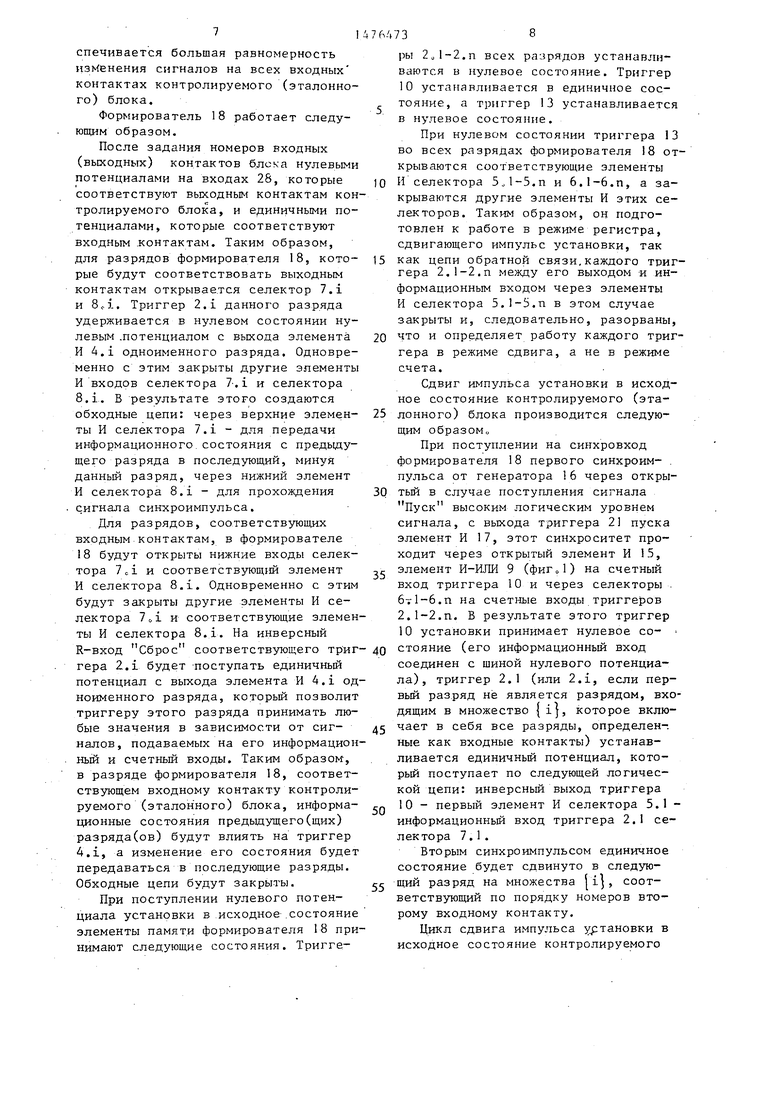

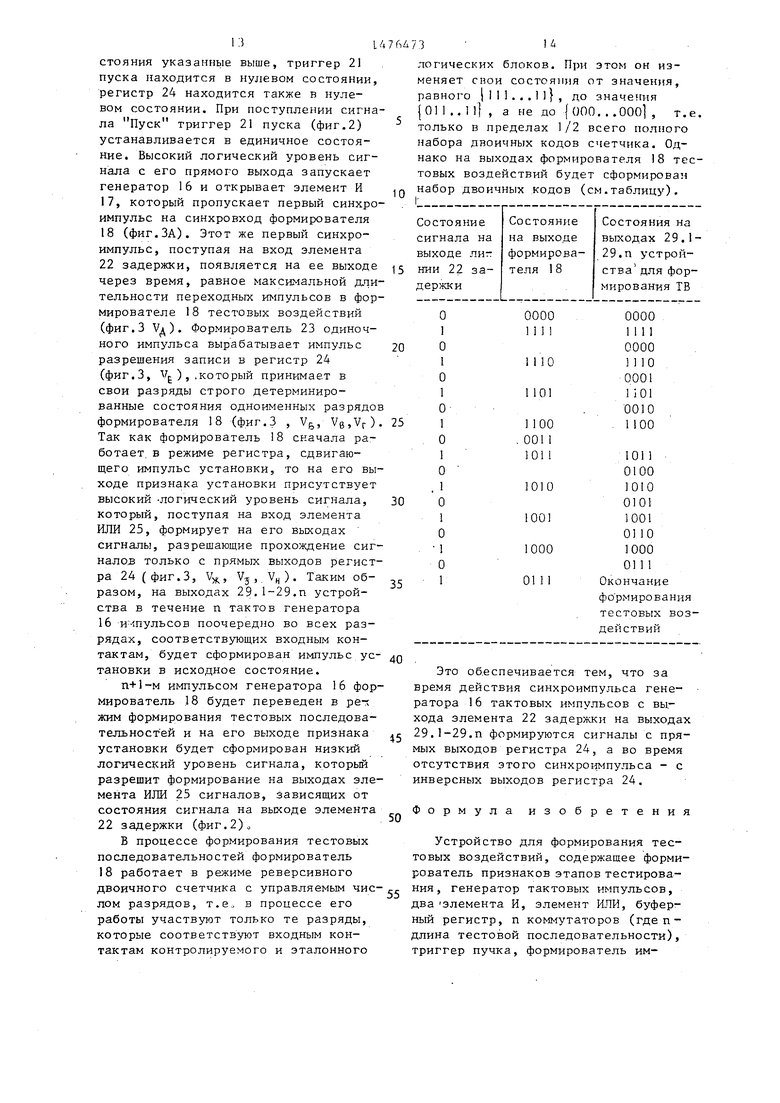

Для пояснения принципа сокращения накапливаемых двоичных последовательностей рассмотрим пример, когда обще число входов составляет четыре. В этом случае (см.таблицу) в устройстве оказывается достаточным сформировать 9 двоичных наборов: П11, 1110, 1101, 1100, 1011, 1010, 1001,. 1000 и 0111, чтобы покрыть полный набор двоичных кодов, равный при четырех разрядах 16 (шестнадцати).

Для доказательства полноты тестовых проверок на данном количестве тестовых последовательностей рассмотрим работу устройства для формирования тестовых воздействий, когда число входов составляет четыре.

Устройство для формирования тестовых воздействий работает следующим образоМо

В исходном состоянии элементы памяти фо-рмирователя 18 принимают со

ИL4

стояния указанные выше, триггер 21 пуска находится в нулевом состоянии, регистр 24 находится также в нулевом состоянии. При поступлении сигнала Пуск триггер 21 пуска (фиг.2) устанавливается в единичное состояние. Высокий логический уровень сигнала с его прямого выхода запускает генератор 16 и открывает элемент И 17, который пропускает первый синхроимпульс на синхровход формирователя 18 (фиг.ЗА). Этот же первый синхроимпульс, поступая на вход элемента 22 задержки, появляется на ее выходе через время, равное максимальной длительности переходных импульсов в формирователе 18 тестовых воздействий (фиг.З Уд). Формирователь 23 одиночного импульса вырабатывает импульс разрешения записи в регистр 24 (фиг.З, Vf.), который принимает в свои разряды строго детерминированные состояния одноименных разрядов формирователя 18 (фиг.З , Vb, Vg,Vr). Так как формирователь 18 сначала работает в режиме регистра, сдвигающего импульс установки, то на его выходе признака установки присутствует высокий -логический уровень сигнала, который, поступая на вход элемента ИЛИ 25, формирует на его выходах сигналы, разрешающие прохождение сигналов только с прямых выходов регистра 24 (фиг.З, Уж, V3 , VH ). Таким образом, на выходах 29.1-29.п устройства в течение п тактов генератора 16 и-шульсов поочередно во всех разрядах, соответствующих входным контактам, будет сформирован импульс ус- тановки в исходное состояние.

п+1-м импульсом генератора 16 формирователь 18 будет переведен в pe-t жим формирования тестовых последовательностей и на его выходе признака установки будет сформирован низкий логический уровень сигнала, который разрешит формирование на выходах элемента ИЛИ 25 сигналов, зависящих от состояния сигнала на выходе элемента 22 задержки (фиг.2)0

В процессе формирования тестовых последовательностей формирователь 18 работает в режиме реверсивного двоичного счетчика с управляемым числом разрядов, т.е. в процессе его работы участвуют только те разряды, которые соответствуют входным контактам контролируемого и эталонного

73U

логических блоков. При этом он изменяет спои состояния от значения, равного ll11..., до значения {01 1 .. 1 1} , а не до { 000. . .000 , т.е. только в пределах 1/2 всего полного набора двоичных кодов счетчика. Однако на выходах формирователя 18 тестовых воздействий будет сформирован набор двоичных кодов (см.таблицу).

15

5 25 до

20

5 25 до

5 25 до

30

5 25 до

35

Это обеспечивается тем, что за время действия синхроимпульса генератора 16 тактовых импульсов с выхода элемента 22 задержки на выходах 29.1-29.п формируются сигналы с прямых выходов регистра 24, а во время отсутствия этого синхроимпульса - с инверсных выходов регистра 24.

Формула изобретения

Устройство для формирования тестовых воздействий, содержащее формирователь признаков этапов тестирования, генератор тактовых импульсов, два элемента И, элемент ИЛИ, буферный регистр, п коммутаторов (гдеп- длина тестовой последовательности), триггер пучка, формирователь импульса, причем выход генератора тактовых импульсов соединен с первым- входом первого элемента И, вход пуска устройства соединен с единичным входом триггера пучка, выход первого элемента И соединен с входом синхронизации формирователя признаков этапов тестирования, адресные входы которого являются входами для задания кодов входов-выходов тестируемого блока устройства и соединены с первыми управляющими входами п коммутаторов, выходы которых являются выходами устройства, причем формирователь признаков этапов тестирования содержит п D-триггеров, п элементов И, триггер формирования и два элемента И, причем прямой выход триггера начала формирования соединен с первым входом первого элемента И формирователя признаков этапов тестирования, инверсный выход триггера начала формирования соединен с первым входом второго элемента И формирователя признаков этапов тестирования, адресные входы формирователя признаков этапов тестирования соединены с первыми входами соответствующих п элементов И,выходы которых соединены с входами сброса одноименных п D-триггеров формирователя признаков этапов тестирования, отличающееся тем, что, с целью расширения функциональных возможностей за счет формирования тестов для последователь- постных блоков, устройство дополнительно содержит элемент И-НЕ, элемент задержки, а формирователь признаков этапов тестирования дополнительно содержит группу из п элементов НЕ, три элемента НЕ, триггер установки, п - п селекторов, причем выход триггера пуска соединен с вторыми входом первого элемента И и с входом пуска генератора тактовых импульсов, выход первого элемента И соединен через элемент задержки с первым входом элемента ИПИ и с вхо10

15

20

регистра и с вторыми входами п элементов И формирователя признаков этапов тестирования, прямые и инверс ные выходы буферного регистра соединены с первыми и вторыми информацион ными входами п коммутаторов соответственно, вторые и третьи управляющие входы п коммутаторов соединены с прямым и инверсным выходами элемента ИЛИ соответственно, выходы п D-триггеров соединены с первыми ин- формационными входами 1. К-го (К,1, о..,п), 2.К-го и З.К-го селекторов, а также с информационными входами буферного регистра, вхо ды задания кода входов-выходов тести руемого блока устройства соединены с первыми управляющими входами 2.К-Х и З.К-х селекторов и через соответствующие п элементы НЕ соединены с вторыми управляющими входами 2. и селекторов, выходы 2,1-х и 3.1-х (,...п-1) селекторов сое- 25 динены Q вторым и первым информацион ными входами 1К-х и 4. К селекторов соответственно, выходы . 1-х селекто ров соединены с D-входами соответствующих D-триггеров и с вторыми информационными входами 2.1-х селекторов, выходы 4-1-х селекторов соединены с С-входами соответствующих D-триггеров и с вторыми информационными входами 3-К-х селекторов, выход 2.п-го селектора соединен через первый элемент НЕ с D-входом триггера начала формирования, выход 3,п-го се лектора соединен с вторым входом элемента И-НЕ, третий вход которого соединен с прямым выходом триггера начала формирования, с вторым входом первого элемента И формирователя признаков этапов тестирования, и с первыми управляющими входами 1.п-х и 4 .п-х селекторов, инверсный выход триггера начала формирования соединен с первым входом второго элемента И формирователя признаков этапов тестирования, с вторыми управляющими

30

35

40

45

дом формирователя импульса, выход ко- 5Q входами 1.п-х и 4.n-х селекторов и с

вторым входом элемента ИЛИ, выход второго элемента И формирователя признаков этапов тестирования соединен с вторыми информационными входами 4-т-х (т 5. с,, ,п) селекторов и с С- входом триггера установки соответст венно и через второй и третий элементы НЕ - с С-входом триггера начала формирования, вторые входы первого и

торого соединен с входом записи-считывания буферного регистра и с первым входом первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И, выход которого соединен с входом сброса триггера пуска, вход сброса устройства соединен с вторым входом второго элемента И, с входом сброса буферною

0

5

0

регистра и с вторыми входами п элементов И формирователя признаков этапов тестирования, прямые и инверсные выходы буферного регистра соединены с первыми и вторыми информационными входами п коммутаторов соответственно, вторые и третьи управляющие входы п коммутаторов соединены с прямым и инверсным выходами элемента ИЛИ соответственно, выходы п D-триггеров соединены с первыми ин- , формационными входами 1. К-го (К,1, о..,п), 2.К-го и З.К-го селекторов, а также с информационными входами буферного регистра, входы задания кода входов-выходов тестируемого блока устройства соединены с первыми управляющими входами 2.К-Х и З.К-х селекторов и через соответствующие п элементы НЕ соединены с вторыми управляющими входами 2. и селекторов, выходы 2,1-х и 3.1-х (,...п-1) селекторов сое- 5 динены Q вторым и первым информационными входами 1К-х и 4. К селекторов соответственно, выходы . 1-х селекторов соединены с D-входами соответствующих D-триггеров и с вторыми информационными входами 2.1-х селекторов, выходы 4-1-х селекторов соединены с С-входами соответствующих D-триггеров и с вторыми информационными входами 3-К-х селекторов, выход 2.п-го селектора соединен через первый элемент НЕ с D-входом триггера начала формирования, выход 3,п-го селектора соединен с вторым входом элемента И-НЕ, третий вход которого соединен с прямым выходом триггера начала формирования, с вторым входом первого элемента И формирователя признаков этапов тестирования, и с первыми управляющими входами 1.п-х и 4 .п-х селекторов, инверсный выход триггера начала формирования соединен с первым входом второго элемента И формирователя признаков этапов тестирования, с вторыми управляющими

0

5

0

5

входами 1.п-х и 4.n-х селекторов и с

вторым входом элемента ИЛИ, выход второго элемента И формирователя признаков этапов тестирования соединен с вторыми информационными входами 4-т-х (т 5. с,, ,п) селекторов и с С- входом триггера установки соответст венно и через второй и третий элементы НЕ - с С-входом триггера начала формирования, вторые входы первого и

V2S.1

$1Л 29.1-1 29п

Фиг, г

Признак учптоЧ

Ил

ГП-Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь тестов | 1985 |

|

SU1259271A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1367015A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| Формирователь тестов | 1985 |

|

SU1291986A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Устройство для функционального контроля логических элементов | 1983 |

|

SU1327108A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Генератор тестовой псевдослучайной двоичной последовательности | 1987 |

|

SU1640699A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - расширение функциональных возможностей за счет формирования тестов для последовательных блоков. Устройство содержит формирователь признаков этапов тестирования, генератор импульсов, буферный регистр, N коммутаторов (N - длина тестовой последовательности), триггер пуска, два элемента И, элемент ИЛИ. На входы формирователя признаков этапов тестирования поступают данные о входах/выходах контролируемого блока. Формирователь вырабатывает тестовую последовательность, сигналы начальной установки, конца формирования, начала формирования. 3 ил., 1 табл.

U6

Егь.

Ж

в

Ж

Иг

Ж

tf

I-I I-I ГП I-IГ

Ue

п п п п п п п

из

ин

Составитель А.Сиротская Редактор Ю.Середа Техред М.Лпд- к Корректор Л.НилипРнко

Заказ 2157/49

Тираж 669

БНИИПИ Государственного комитета по изобретениям и отьрьчилм при СССР 113035, Москва, Ж-35, Раушская наб., д. 4/

т

Ж1

ж

JL

п

ПодгА

сное

| Авторское свидетельство СССР № 1183969, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Формирователь тестов | 1985 |

|

SU1259271A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-30—Публикация

1987-10-06—Подача