Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано в радиоэлектронной промышленности в процессе серийного производства микропроцессоров,

Цель изобретения - расширение функциональных возможностей за счет обеспечения формирования тестов для контроля микропроцессорных элементов.

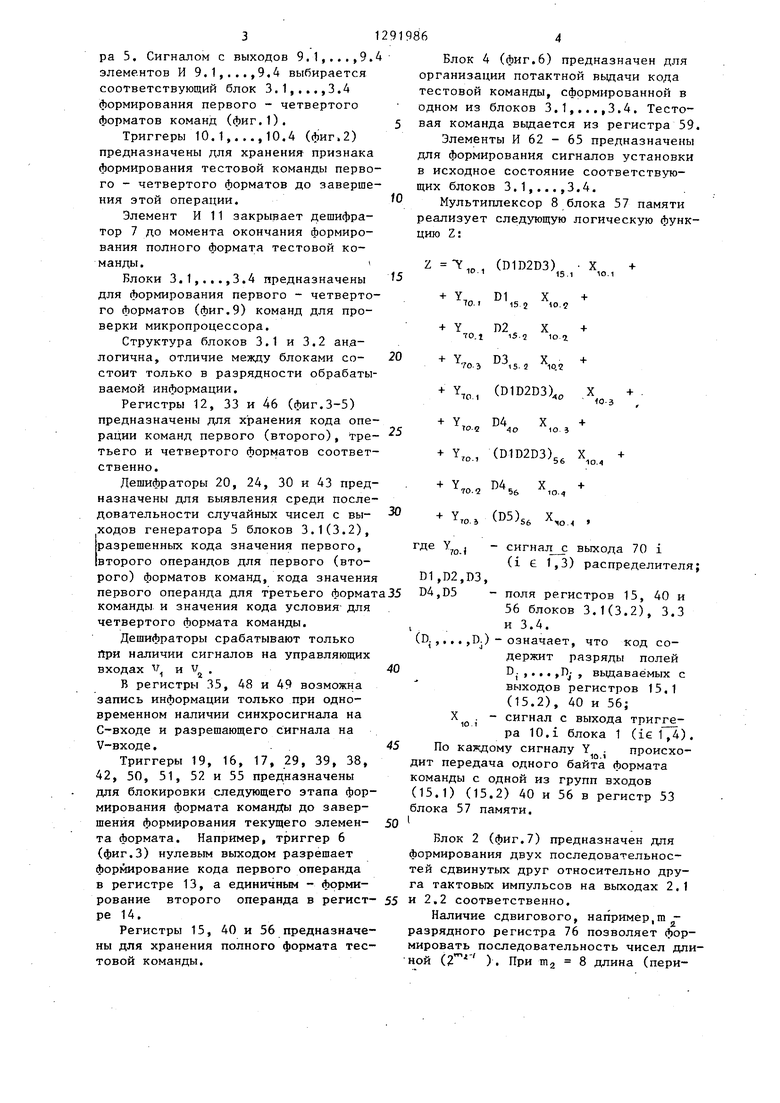

Формирователь тестов (фиг.1) содержит блок 1 задания режима рабо- ты, блок 2 синхронизации, блоки 3,1,,,,,З.п формирования входных воздействий, узел 4 вьщачи теста, генератор 5 псевдослучайных кодов.

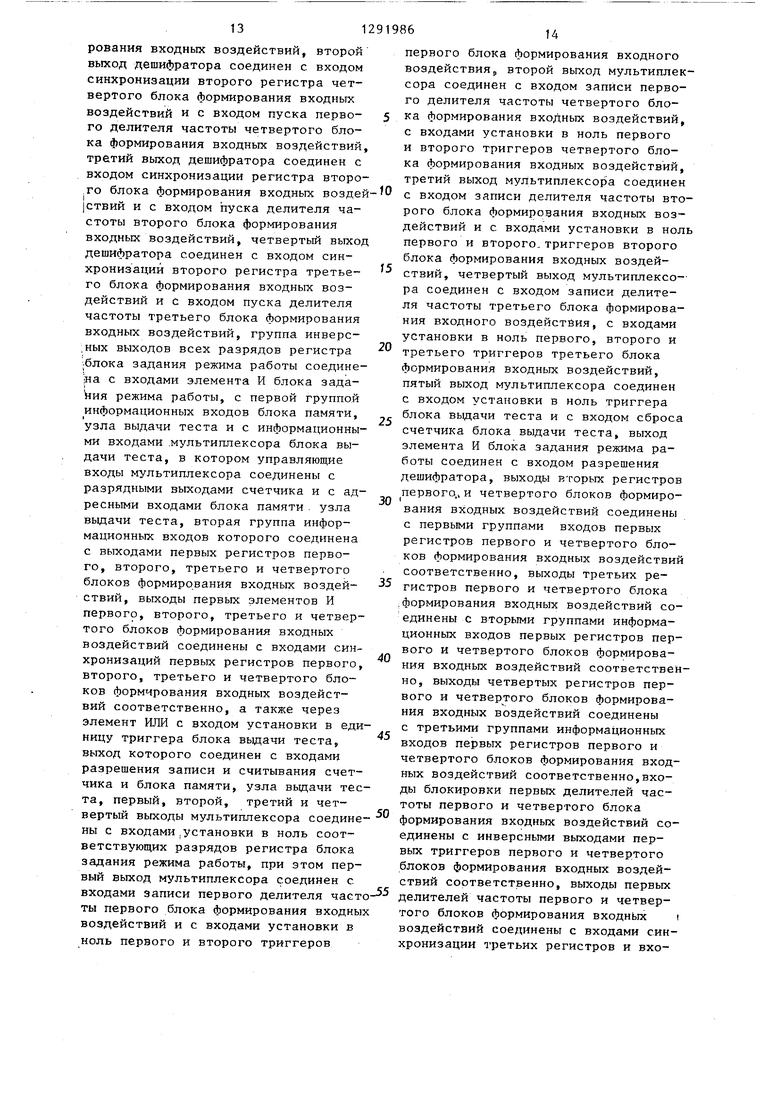

Блок 1 задания режима работы (фиг,2) содержит дешифратор 6 (образованный дешифратором 7, элементами ИЛИ 8,1,,,,,8,4), элементы И 9,1,,,,,9,4, регистр 10 (образован триггерами 10,1,,,,,10,4), элемент И 11,

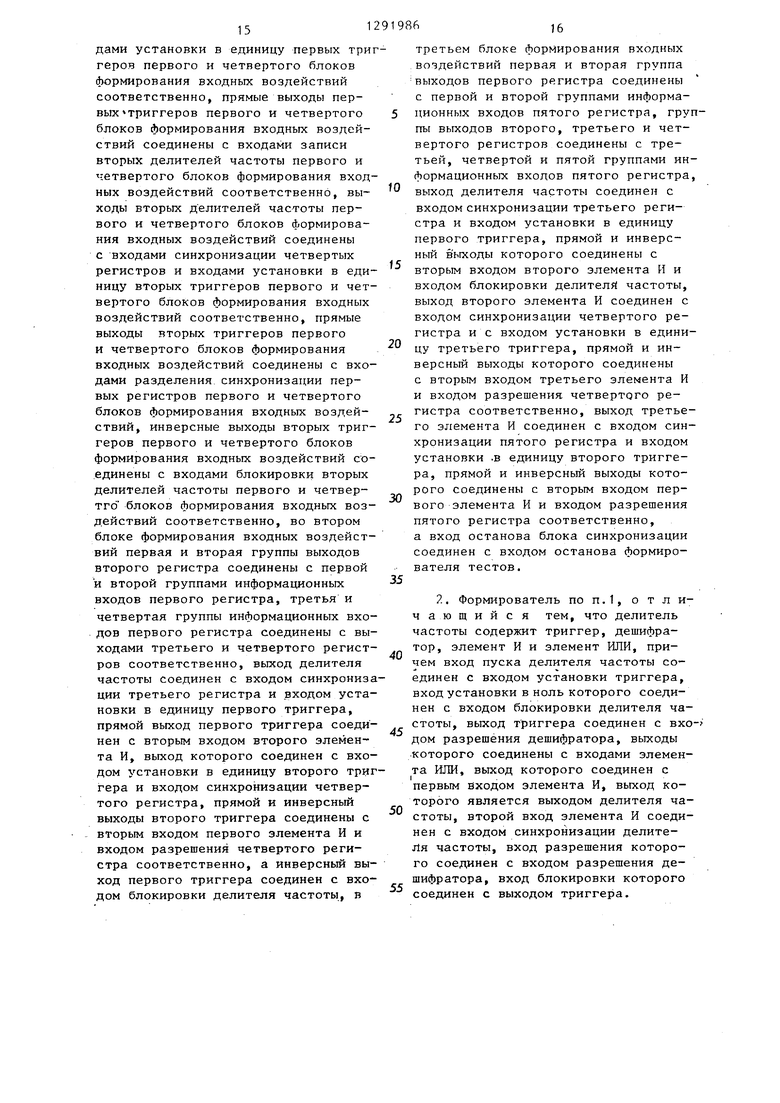

Блок 3,1 (3,2) формирования входного воздействия (первый и четвертый блоки) (фиг,3) содержит регистр 12 (в него записывается код операции), регистр 13 (записывается первый операнд), регистр 14 (записывается второй .операнд) , регистр 15, триггеры 16 и 17, делитель 18 частоты, образованный .триггером 19, дешифратором 20, элементом ИЛИ 21, элементом И 22 делитель 23 частоты, образованный дешифратором 24, элементом ИЛИ 25, элементом И 26, а также элемент И 27,

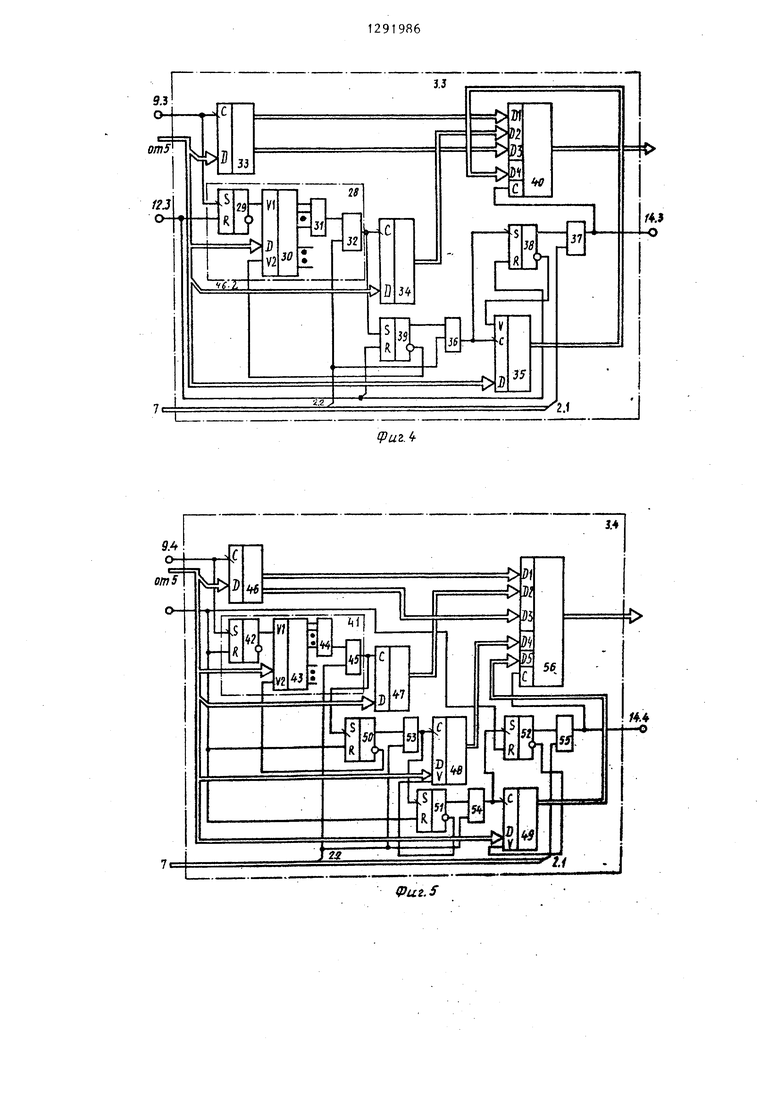

Второй блок 3,3 формирования входных воздействий (фиг,4) содержит делитель 28 частоты, образованный триггером 29, дешифратором 30, элементом ИЛИ 31, элементом И 32, регистр 33 (хранит код операции), регистр 34 (хранит первый операнд), регистр 35 (хранит второй операнд), элементы

И 36 и 37,триггеры 38 и 39,регистр 40

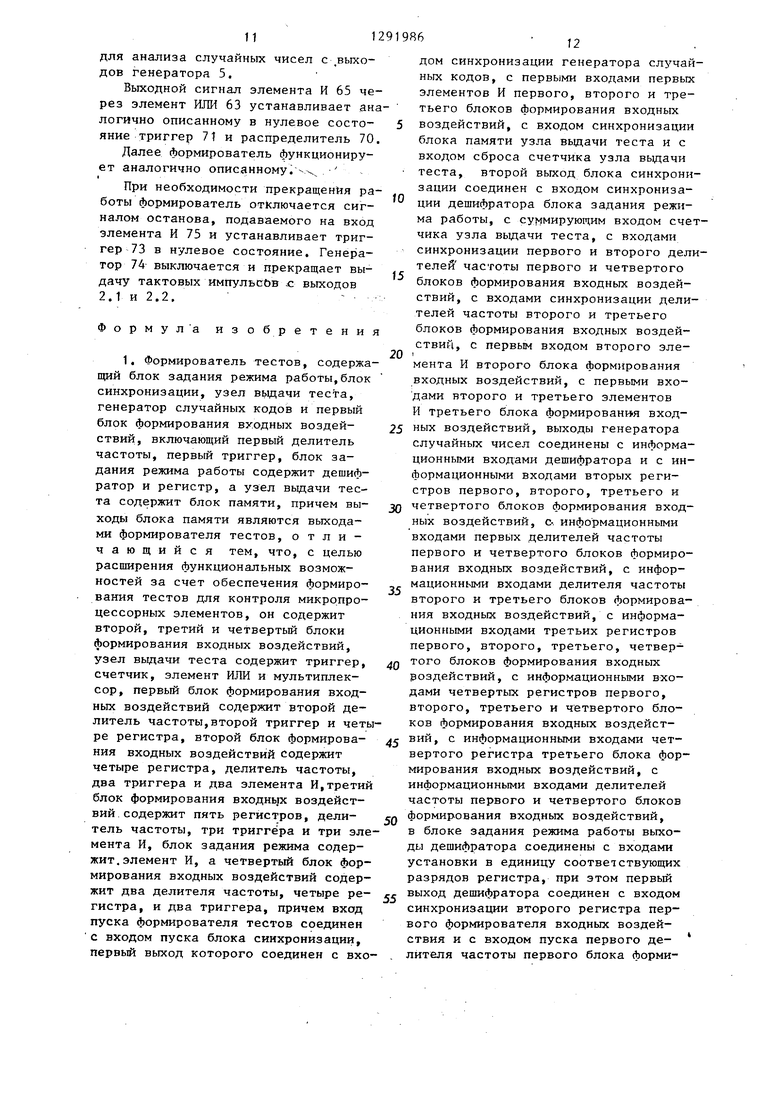

Третий блок 3,4 формирования входных воздействий (фиг,5) содержит делитель 41 частоты,образованный триггером 42, дешифратором 43, элементом ИЛИ 44, элементом И 45, регистр 46 (хранит код операции), регистр 47 (хранит код условия), регистр 48 (хр

Дешифратор 7 (фиг,2) предназнач для выбора из случайной последовател ности чисел, которые можно использ вать для формирования кодов операци тестовых команд,Каждый из элементо ИЛИ 8,1,.,,,8,4 объединяет выходы Д1,,,,,Д4 дешифратора 7, соответствующие командам с первого - четвер .того форматов. Элементы И 9,1,,,,, 9,4 предназначены для формирования

нит первый операнд), регистр 49(хра-

нит второй операнд), триггеры 50 - 52, случайного сигнала выбора команд и

элементы И 53 - 55, регистр 56,

Узел 4 выдачи теста (фиг,6) содержит блок 57 памяти, образованный мульформатов на основании выходных сиг налов элементов ИЖ 8,1,.,,,8,4 и кодов случайных чисел от генерато

0

5

0

5

0

5

0

типлексором 58, регистром 59, элементом И 60, мультиплексор 61, образованный элементами И 62-65 и элементом ИЖ 66, счетчик 67, образованный элементами И 68 и 69 и распределителем 70 импульсов, триггер 71, элемент ИЛИ 72,

Блок 2 синхронизации (фиг,7) содержит триггер 73, генератор 74 тактовых импульсов и элемент И 75,

Генератор 5 псевдослучайной последовательности (фиг,8) содержит регистр 76 с,,вига, элемент И-НЕ 77, сумматор 78 по модулю два,элемент ИЛИ 79,

На фиг,3 - 5 приведены примеры выполнения блоков 3,1 (3,2), 3,3 и 3.4, которые формируют первый (второй) , третий и четвертый форматы команд соответственно для микропроцессора типа INTEL 8080, К580 и других аналогичного типа,

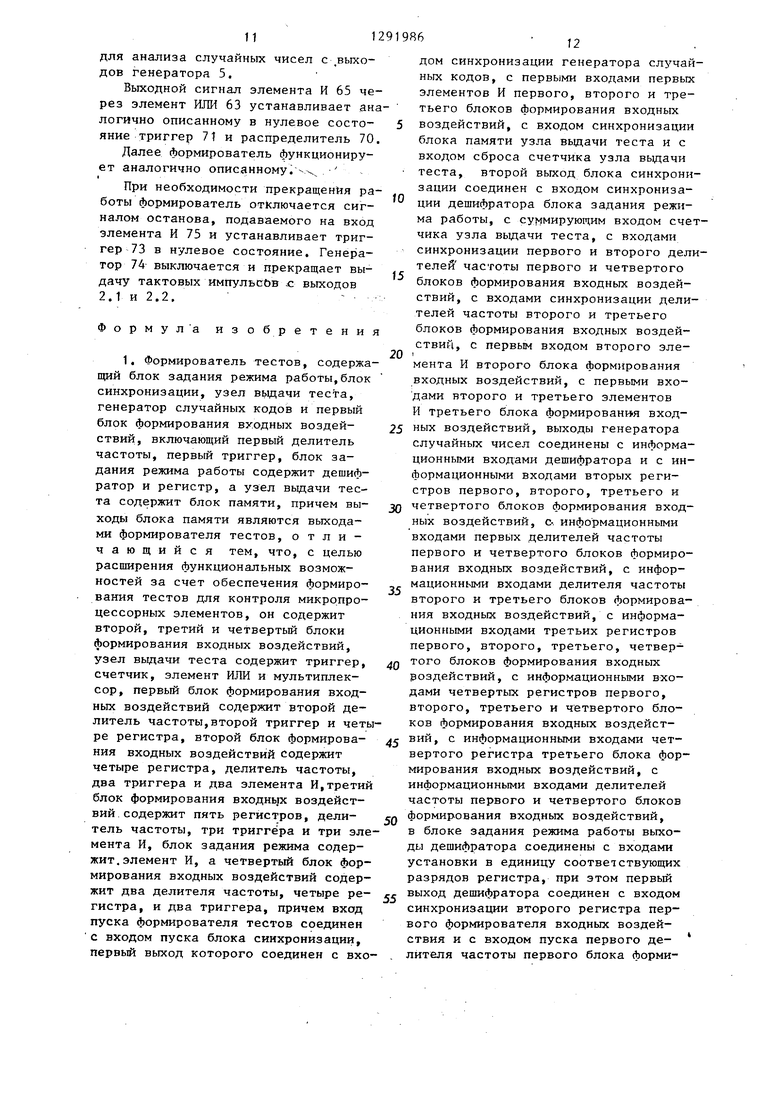

Для пояснения работы формирователя тестов, формирующего команды различных форматов для микропроцессора указанного tипa, используется структура форматов команд микропроцессора (фиг,9),

Поскольку структуры форматов (число и назначение) полей команд первого (фиг,9, 3,1) и второго (фиг,9, 3,2) форматов отличаются только разрядностью, то в качестве примера предлагается реализация блоков 3,1 и 3,2 по одной и той же функциональной схеме. Отличие между схемами двух этих блоков состоит только в разрядности обрабатываемой информации.

Блок 1 задания режима работы (фиг,1 и 2) предназначен для формирования случайной последовательности типов форматов и кодов чисел, поступающих с выходов генератора 5 (фиг,1),

Дешифратор 7 (фиг,2) предназначен для выбора из случайной последователь-- ности чисел, которые можно использовать для формирования кодов операций тестовых команд,Каждый из элементов ИЛИ 8,1,.,,,8,4 объединяет выходы Д1,,,,,Д4 дешифратора 7, соответствующие командам с первого - четвер- .того форматов. Элементы И 9,1,,,,, 9,4 предназначены для формирования

форматов на основании выходных сигналов элементов ИЖ 8,1,.,,,8,4 и кодов случайных чисел от генерато3

pa 5. Сигналом с выходов 9.1,...,9. элементов И 9.1,...,9,4 выбирается соответствующий блок 3.1,...,3.4 формирования первого - четвертого форматов команд (фиг.1).

Триггеры 10.1,...,10.4 (фиг.2) предназначены для хранения признака формирования тестовой команды первого - четвертого форматов до завершения этой операции.

Элемент И 11 закрывает дешифратор 7 до момента окончания формирования полного формата тестовой команды,t

Блоки 3.1,...,3.4 предназначены для формирования первого - четвертого форматов (фиг.9) команд для проверки микропроцессора.

Структура блоков 3.1 и 3.2 ан.а- логична, отличие между блоками со- стоит только в разрядности обрабатываемой информации.

Регистры 12, 33 и 4б (фиг.3-5) предназначены для хранения кода операции команд первого (второго), тре- тьего и четвертого форматов соответственно.

Дешифраторы 20, 24, 30 и 43 предназначены для выявления среди последовательности случайных чисел с вы- ходов генератора 5 блоков 3.1(3.2), разрешенных кода значения первого, второго операндов для первого (второго) форматов команд, кода значения первого операнда для третьего формат команды и значения кода условия- для четвертого формата команды.

Дешифраторы срабатывают только при наличии сигналов на управляющих входах и v, .

В регистры 35, 48 и 49 возможна запись информации только при одновременном наличии синхросигнала на С-входе и разрешающего сигнала на V-входе,.

Триггеры 19, 16, 17, 29, 39, 38, 42, 50, 51, 52 и 55 предназначены для блокировки следующего этапа формирования формата команды до завершения формирования текущего элемен- та формата. Например, триггер 6 (фиг.З) нулевым выходом разрешает формирование кода первого операнда в регистре 13, а единичным - формирование второго операнда в регист- ре 14.

Регистры 15, 40 и 56 предназначены для хранения полного формата тестовой команды.

864

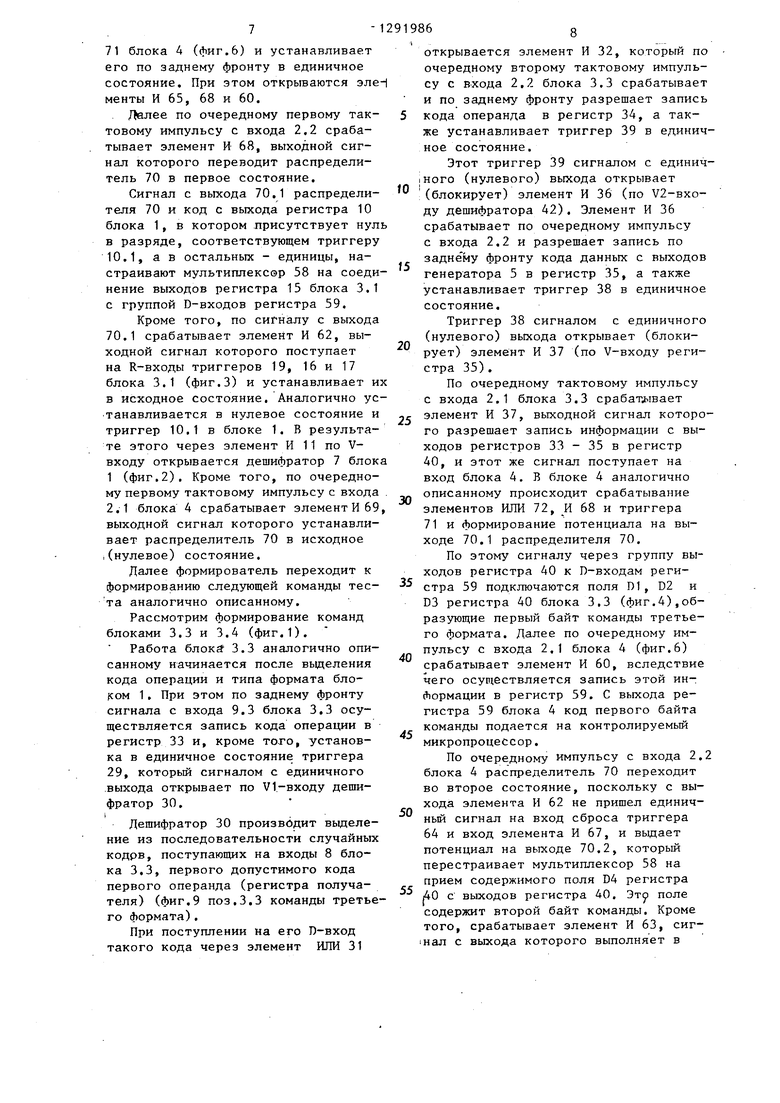

Блок 4 (фиг,6) предназначен для организации потактной выдачи кода тестовой команды, сформированной в одном из блоков 3,1,,,,,3.4. Тестовая команда вьщается из регистра 59,

Элементы И 62 - 65 предназначены для формирования сигналов установки в исходное состояние соответствующих блоков 3.1,,,,,3,4,

Мультиплексор 8 блока 57 памяти реализует следующую логическую функцию Z:

Z . (D1D2D3) X +

.110.1

+ Y, D1X+

0.115 2 1О 9

+ Y D2 X +

ТО.115.2 10.2.

V3 D3,,., -ь

+ V, (D1D2D3), Х. +

«о-з

Y,,D4 Х, -ь

,„,(D1D2D3)5, Х +

Y,,D4 Х, -ь

- Y,.,(D5)s, Х,„ ,

7o.i сигнал ; выхода 70 i

(i е 1,3) распределителя D1,D2,D3,

D4,D5 - поля регистров 15, 40 и 56 блоков 3,1(3,2), 3,3 V . и 3,4, (,.,, ,Dj) - означает, что код содержит разряды полей D. ,, ,, ,nj- , вьщаваёмых с выходов регистров 15,1 (15,2), 40 и 56; X,Q ; сигнал с выхода триггера 10,1 блока 1 (ie1). По каждому сигналу Y происходит передача одного байта формата команды с одной из групп входов (15,1) (15,2) 40 и 56 в регистр 53

блока 57 памяти,

I

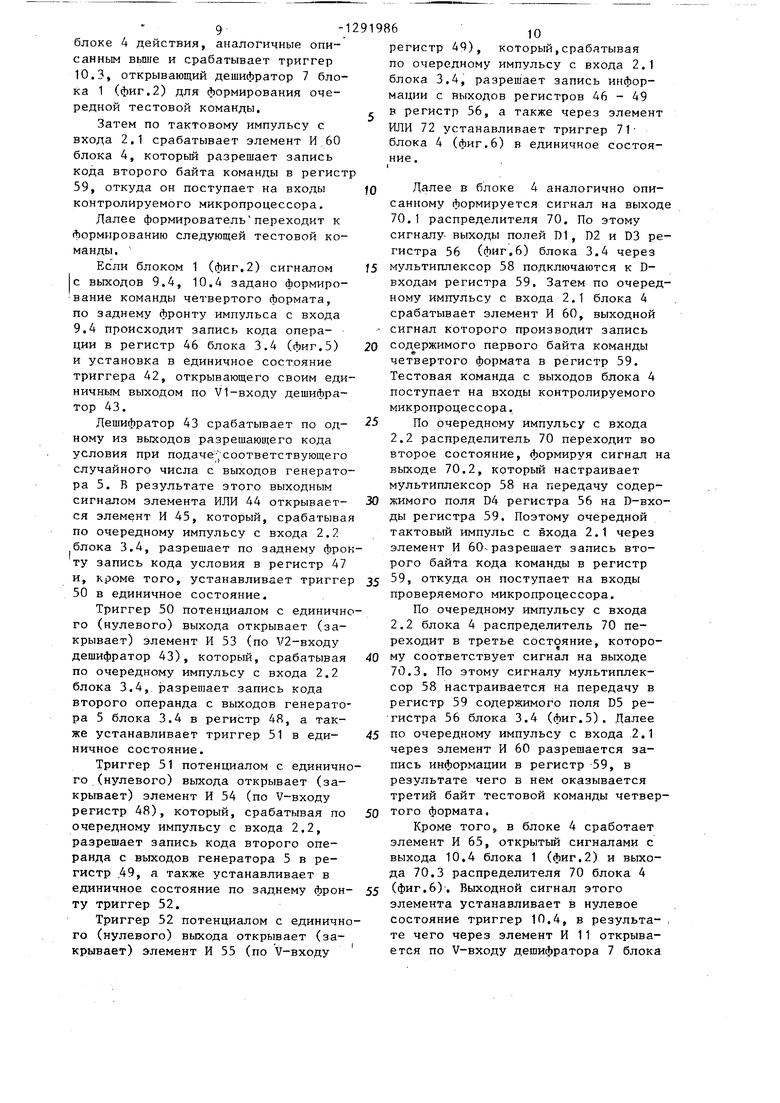

Блок 2 (фиг,7) предназначен для формирования двух последовательностей сдвинутых друг относительно друга тактовьпс импульсов на выходах 2. 1 и 2,2 соответственно.

Наличие сдвигового, например,m - разрядного регистра 76 позволяет формировать последовательность чисел дли ной ( ) . При 2 8 длина (период) последовательности равна 255 чисел.

Форматы команд (фиг,9) формирует формирователь. При этом обозначения позиций фиг,9 - 3.1 соответствует i-му (i С 1,А) формату команды. Обозначения полей П . (J е 1,5) в соответствующих позициях фиг.9 соответствуют полям выходных регистров 25, 40 и 56 блоков 3.1 (3.2), 3.3 и 3.4

Кроме того, на- фиг.9 использованы обозначения: КОП - код операции; Рд - получ. (источ.) - код регистра получателя (источника); мл (ст.) - младшие (старшие); КОД УСЛ. - код условия.

Формирователь работает следующим образом.

В исходном со стоянии все элементы памяти установлены в нулевое состояние (цепи начальной установки не показаны). По сигналу пуска триггер 75 блока 2 (фиг,7) устанавливается в единичное состояние и включает генератор 74, который начинает формирование тактовых импульсов на выходах 2,1 и 2.2.

По каждому тактовому импульсу с выхода 2.1 блока 2 осуществляется сдвиг информации в регистре 76 генератора 5 и формирование нового кода случайного числа на группе выходов генератора 5 (фиг.8)

Каждьй случайный код с выхода генератора 5 (фиг.1) поступает на

входы дешифратора 7 блока 1,

При обнаружении очередного допустимого кода операции команды i-ro формата срабатывает один из элементов ИЛИ 8.1, выходной сигнал которого открывает-элемент И 9.1,

Если в это же время на 1-м входе дешифратора 7 присутствует единичный сигнал, элемент И 9,1 срабатывает по импульсу со входа 2,2 и устанавливает соответствующий триггер 10,1 в единичное состояние. Поэтому сигнал с выхода элемента И 11 снимается, и, следовательно, дешифратор 7 закрывается по V-входу до момента окончания формирования комады выбранного формата.

Одновременно выходной сигнал элемента И 9.1 через выход 9,1 блока 1 поступает на одноименный вход соответствующего блока 3.

Предположим, что блоком 1 выход- ным сигналом с выхода 9,1 задано

формирование команды первого форма- | та (фиг,9, поз,3,1). Поэтому по заднему фронту второго импульса с выхода 2.2 блока 2 происходит запись по

сигналу с входа 9.1 блока 3,1 кода операции команды с выходов генератора 5 блока 3.1 (фиг.З) в регистр 12. Кроме того, этим же сигналом триггер 19 устанавливается в единичное состояние и открывает по входу VI дешифратор 20.

По очередному первому тактовому импульсу генератор 5 (фиг.1) формирует следуюп1ее случайное число. Если это число.соответствует допусти- . мому коду первого операнда, сигнал с выхода дешифратора 20 через элемент ИЛИ 21 открывает элемент И 22, Элемент И 22 срабатывает по очеpeд oмy второму тактовому импульсу с входа 2.2 блока 3,1 и разрешает запись по заднему фронту этого импульса кода операнда в регистр 13, а также устанавливает триггер 16 в

единичное состояние. Этот триггер 16 закрывает (открывает) сигналом с нулевого (единичного) выхода дешифратор 20 (дешифратор 24 по входу VI), .

Далее аналогично описанному формируется очередное случайное число генератором 5 (фиг,1) и осуществляется его анапиз дешифратором 24 (фиг.З), запись в регистр 14 и установка в единичное состояние триггера 17.

Если на этапе формирования первого или второго операнда очередное случайное число не соответствует до-s

(Пустимому коду соответствующего операнда, блок 3,1 (3.2) своего состояния не изменяет до тех.пор, пока с выходов генератора 5 не поступит до-, пустимое число,

После установки по заднему фронту соответствующего второго импульса триггера 17 в единичное состояние закрывает по входу V2 дешифратор 29 и открывается элемент И 27.

Этот элемент срабатывает по очередному второму тактовому импульсу с входа 2,1 блока 3,1 и разрешает запись информации с выходов регистров 12 - 14 в соответствующие поля D1,

D2 и D3 регистра 15.

Одновременно выходной сигнал элемента И 27 блока 3,1 поступает через элемент ИЛИ 72 на S-вход триггера

7

71 блока 4 (фиг.6) и устанавливает его по заднему фронту в единичное состояние. При этом открываются эл менты И 65, 68 и 60.

Далее по очередному первому тактовому импульсу с входа 2,2 срабатывает элемент И 6В, выходной сигнал которого переводит распределитель 70 в первое состояние.

Сигнал с выхода 70.1 распределителя 70 и код с выхода регистра 10 блока 1, в котором лрисутствует ну в разряде, соответствующем триггер 10.1, а в остальных - единицы, настраивают мультиплексор 58 на соеднение выходов регистра 15 блока 3. с группой D-входов регистра 59.

Кроме того, по сигналу с выход 70.1 срабатывает элемент И 62, выходной сигнал которого поступает на R-входы триггеров 19, 16 и 17 блока 3.1 (фиг.З) и устанавливает в исходное состояние. Аналогично у танавливается в нулевое состояние триггер 10.1 в блоке 1. В результате этого через элемент И 11 по V- входу открывается дешифратор 7 бло 1 (фиг.2). Кроме того, по очередному первому тактовому импульсу с вход 2.1 блока 4 срабатывает элемент И 6 выходной сигнал которого устанавливает распределитель 70 в исходное .(нулевое) состояние.

Далее формирователь переходит к формированию следующей команды тес та аналогично описанному.

Рассмотрим формирование команд блоками 3.3 и 3.4 (фиг.1).

Работа блокс 3.3 аналогично описанному начинается после вьщеления кода операции и типа формата бло- (сом 1. При этом по заднему фронту сигнала с входа 9.3 блока 3.3 осуществляется запись кода операции в регистр 33 и, кроме того, установка в единичное состояние триггера 29, который сигналом с единичного .выхода открывает по VI-входу дешифратор 30. I

Дешифратор 30 производит вьщеление из последовательности случайны кодрв, поступающих на входы 8 блока 3.3, первого допустимого кода первого операнда (регистра получателя) (фиг.9 поз.3.3 команды третьго формата).

При поступлении на его D-вход такого кода через элемент ИЛИ 31

0

5

0

5

1986

0

5

0

5

0

5

8

открывается элемент И 32, который по очередному второму тактовому импульсу с входа 2.2 блока 3.3 срабатывает и по заднему фронту разрешает запись кода операнда в регистр 34, а также устанавливает триггер 39 в единичное состояние.

Этот триггер 39 сигналом с единич- iHoro (нулевого) выхода открывает (блокирует) элемент И 36 (по V2-Bxo- ду дешифратора 42). Элемент И 36 срабатывает по очередному импульсу с входа 2.2 и разрешает запись по задне ну фронту кода данных с выходов генератора 5 в регистр 35, а также устанавливает триггер 38 в единичное состояние.

Триггер 38 сигналом с единичного (нулевого) выхода открывает (блокирует) элемент И 37 (по V-входу регистра 35) .

По очередному тактовому импульсу с входа 2.1 блока 3.3 срабатывает элемент И 37, выходной сигнал которого разрешает запись информации с выходов регистров 33 - 35 в регистр 40, и этот же сигнал поступает на вход блока 4. В блоке 4 аналогично описанному происходит срабатывание элементов ИЛИ 72, И 68 и триггера 71 и формирование потенциала на выходе 70.1 распределителя 70.

По этому сигналу через группу выходов регистра 40 к D-входам регистра 59 подключаются поля D1, D2 и D3 регистра 40 блока 3.3 (фиг.4),образующие первый байт команды третьего формата. Далее по очередному импульсу с входа 2.1 блока 4 (фиг.6) срабатывает элемент И 60, вследствие чего осуществляется запись этой ин- Лормации в регистр 59. С выхода регистра 59 блока 4 код первого байта команды подается на контролируемый микропроцессор.

По очередному импупьсу с входа 2.2 блока 4 распределитель 70 переходит во второе состояние, поскольку с выхода элемента И 62 не пришел единичный сигнал на вход сброса триггера 64 и вход элемента И 67, и вьщает потенциал на выходе 70.2, который перестраивает мультиплексор 58 на прием содержимого поля D4 регистра j40 с выходов регистра 40. Эт) поле содержит второй байт команды. Кроме того, срабатывает элемент И 63, сиг- нал с выхода которого выполняет в

-1291986

блоке 4 действия, аналогичные описанным выше и срабатывает триггер Ю.З, открывающий дешифратор 7 блока 1 (фиг.2) для формирования очередной тестовой команды.

Затем по тактовому импульсу с входа 2.1 срабатывает элемент И 60 блока 4, который разрешает запись кода второго байта команды в регистр 59, откуда он поступает на входы контролируемого микропроцессора.

Далее формирователь переходит к формированию следующей тестовой команды.

Если блоком 1 (фиг,2) сигналом с выходов 9.4, 10.4 задано формиро- вание команды четвертого формата, по заднему фронту импульса с входа 9,4 происходит запись кода операции в регистр 46 блока 3.4 (фиг.5) и установка в единичное состояние триггера 42, открывающего своим единичным выходом по V1-входу дешифратор 43.

Дешифратор 43 срабатывает по од- ному из выходов разрешающего кода условия при подаче соответствующего случайного числа с выходов генератора 5. В результате этого выходным сигналом элемента ИЛИ 44 открывает- ся элемент И 45, который, срабатывая по очередному импульсу с входа 2.2 блока 3.4, разрешает по заднему фронту запись кода условия в регистр 47 и, кроме того, устанавливает триггер 50 в единичное состояние.

Триггер 50 потенциалом с единичного (нулевого) выхода открывает (закрывает) элемент И 53 (по У2-входу дешифратор 43), который, срабатывая по очередному импульсу с входа 2.2 блока 3.4, разрешает запись кода второго операнда с выходов генератора 5 блока 3.4 в регистр 48, а также устанавливает триггер 51 в еди- ничное состояние.

Триггер 51 потенциалом с единичного (нулевого) выхода открывает (за- крьгоает) элемент И 54 (по V-входу регистр 48), который, срабатывая по очередному импульсу с входа 2.2, разрешает запись кода второго операнда с выходов генератора 5 в регистр 49, а также устанавливает в единичное состояние по заднему фрон- ту триггер 52.

Триггер 52 потенциалом с единичного (нулевого) выхода открывает (закрывает) элемент И 55 (по V-входу

10

регистр 49), который,срабатывая по очередному импульсу с входа 2.1 блока 3.4, разрешает запись информации с выходов регистров 46 - 49 в регистр 56, а также через элемент ШШ 72 устанавливает триггер 71 блока 4 (фиг.6) в единичное состояние . I

Далее в блоке 4 аналогично описанному формируется сигнал на выход 70.1 распределителя 70. По этому сигналу- выходы полей D1, D2 и D3 регистра 56 (фиг,6) блока 3.4 через мультиплексор 58 подключаются к D- входам регистра 59. Затем по очередному импульсу с входа 2.1 блока 4 срабатывает элемент И 60, выходной сигнал которого производит запись содержимого первого байта команды четвертого формата в регистр 59. Тестовая команда с выходов блока 4 поступает на входы контролируемого микропроцессора.

По очередному импульсу с входа 2.2 распределитель 70 переходит во второе состояние, формируя сигнал н вькоде 70.2, который настраивает мультиплексор 58 на передачу содержимого поля D4 регистра 56 на D-BXO ды регистра 59. Поэтому очередной тактовый импульс с входа 2.1 через элемент И 60-разрешает запись второго байта кода команды в регистр 39, откуда он поступает на входы проверяемого микропроцессора.

По очередному импульсу с входа 2.2 блока 4 распределитель 70 переходит в третье состояние, которому соответствует сигнал на выходе 70.3. По этому сигналу мультиплексор 58 настраивается на передачу в регистр 59 содержимого поля D5 регистра 56 блока 3.4 (фиг,5). Далее по очередному импульсу с входа 2,1 через элемент И 60 разрешается запись информации в регистр 59, в результате чего в нем оказывается третий байт тестовой команды четвертого формата.

Кроме того„ в блоке 4 сработает элемент И 65, открытый сигналами с выхода 10,4 блока 1 (фиг,2) и выхода 70.3 распре делителя 70 блока 4 (фиг.6), Выходной сигнал этого элемента устанавливает в нулевое состояние триггер 10.4, в результа- те чего через элемент И 11 открывается по V-входу дешифратора 7 блока

для анализа случайных чисел с .выходов генератора 5.

Выходной сигнал элемента И 65 через элемент ИЛИ 63 устанавливает анлогично описанному в нулевое состояние триггер 7t и распределитель 70

Далее формирователь функционирует аналогично описанному.-

I

При необходимости прекращения работы формирователь отключается сигналом останова, подаваемого на вход элемента И 75 и устанавливает триггер 73 в нулевое состояние. Генератор 74 выключается и прекращает выдачу тактовых импульсЬв jc выходов 2.1 и 2.2.

Формул а изо б р е т е н и

1. Формирователь тестов, содержащий блок задания режима работы,блок синхронизации, узел вьщачи теста, генератор случайных кодов и первый блок формирования входных воздействий, включающий первый делитель частоты, первый триггер, блок задания режима работы содержит дешифратор и регистр, а узел вьщачи теста содержит блок памяти, причем выходы блока памяти являются выходами формирователя тестов, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения формирования тестов для контроля микропроцессорных элементов, он содержит второй, третий и четвертый блоки формирования входных воздействий, узел вьщачи теста содержит триггер, счетчик, элемент ИЛИ и мультиплексор, первый блок формирования входных воздействий содержит второй делитель частоты,второй триггер и четыре регистра, второй блок формирования входных воздействий содержит четыре регистра, делитель частоты, два триггера и два элемента И,третий блок формирования входньрс воздействий, содержит пять регистров, делитель частоты, три триггера и три элемента И, блок задания режима содержит, элемент И, а четвертый блок формирования входных воздействий содержит два делителя частоты, четыре регистра, и два триггера, причем вход пуска формирователя тестов соединен с входом пуска блока синхронизации, первьй выход которого соединен с вхо

O

5

0

дом синхронизации генератора случайных кодов, с первыми входами первых элементов И первого, второго и третьего блоков формирования входных воздействий, с входом синхронизации блока памяти узла вьщачи теста и с входом сброса счетчика узла вьщачи теста, второй выход блока синхронизации соединен с входом синхронизации дешифратора блока задания режима работы, с суммирующим входом счетчика узла вьщачи теста, с входами синхронизации первого и второго делителей частоты первого и четвертого блоков формирования входных воздействий, с входами синхронизации делителей частоты второго и третьего блоков формирования входных воздействий, с первым входом второго эле- I

мента И второго блока формирования входных воздействий, с первыми входами второго и третьего элементов И третьего блока формирования вход5 ных воздействий, выходы генератора случайных чисел соединены с информационными входами дешифратора и с информационными входами вторых регистров первого, второго, третьего и

Q четвертого блоков формирования входных воздействий, с-, информационными входами первых делителей частоты первого и четвертого блоков формирования входных воздействий, с информационными входами делителя частоты второго и третьего блоков формирования входных воздействий, с информационными входами третьих регистров первого, второго, третьего, четвертого блоков формирования входных воздействий, с информационными входами четвертых регистров первого, второго, третьего и четвертого блоков формирования входных воздейст5

0

ВИЙ, с информационными входами четвертого регистра третьего блока формирования входных воздействий, с информационными входами делителей частоты первого и четвертого блоков формирования входных воздействий, в блоке задания режима работы выходы дешифратора соединены с входами установки в единицу соответствующих разрядов регистра, при этом первый выход дешифратора соединен с входом синхронизации второго регистра первого формирователя входных воздействия и с входом пуска первого делителя частоты первого блока форми

рования входных воздействий, второй выход дешифратора соединен с входом синхронизации второго регистра четвертого блока формирования входных воздействий и с входом пуска перво- го делителя частоты четвертого блока формирования входных воздействий, третий выход дешифратора соединен с входом синхронизации регистра второго блока формирования входных воздай |ствий и с входом пуска делителя частоты второго блока формирования входных воздействий, четвертый выход дешифратора соединен с входом синхронизации второго регистра третьего блока формирования входных воздействий и с входом пуска делителя частоты третьего блока формирования входных воздействий, группа инверс- ;ных выходов всех разрядов регистра блока задания режима работы соединена с входами элемента И блока зада- ия режима работы, с первой группой информационных входов блока памяти, узла выдачи теста и с информационными входами .мультиплексора блока выдачи теста, в котором управляющие входы мультиплексора соединены с разрядными выходами счетчика и с адресными входами блока памяти . узла выдачи теста, вторая группа информационных входов которого соединена с выходами первых регистров первого, второго, третьего и четвертого блоков формирования входных воздействий, выходы первых элементов И первого, второго, третьего и четвертого блоков формирования входных воздействий соединены с входами синхронизации первых регистров первого второго, третьего и четвертого блоков формирования входных воздействий соответственно, а также через элемент ИЛИ с входом установки в единицу триггера блока вьщачи теста, выход которого соединен с входами разрешения записи и считывания счетчика и блока памяти, узла выдачи тес

та, первый, второй, третий и четвертый выходы мультиплексора соединены с входами I установки в ноль соответствующих разрядов регистра блока задания режима работы, при этом первый выход мультиплексора соединен с входами записи первого делителя часто ты первого блока формирования входных воздействий и с входами установки в ноль первого и второго триггеров

5

0

5

0

5

0

5

0

5

первого блока формирования входного воздействия,, второй выход мультиплексора соединен с входом записи первого делителя частоты четвертого блока формирования входных воздействий, с входами установки в ноль первого и второго триггеров четвертого блока формирования входных воздействий, третий выход мультиплексора соединен с входом записи делителя частоты второго блока формирования входных воздействий и с входами установки в ноль первого и второго.триггеров второго блока формирования входных воздействий, четвертый выход мультиплексора соединен с входом записи делителя частоты третьего блока формирования входного воздействия, с входами установки в ноль первого, второго и третьего триггеров третьего блока формирования входных воздействий, пятый выход мультиплексора соединен с входом установки в ноль триггера блока выдачи теста и с входом сброса счетчика блока выдачи теста, выход элемента И блока задания режима работы соединен с входом разрешения дешифратора, выходы вторых регистров первого,, и четвертого блоков формирования входных воздействий соединены с первыми группами входов первых регистров первого и четвертого блоков формирования входных воздействий соответственно, выходы третьих регистров первого и четвертого блока сформирования входных воздействий соединены с вторыми группами информационных входов первых регистров первого и четвертого блоков формирования входных воздействий соответственно, выходы четвертых регистров первого и четвертого блоков формирования входных воздействий соединены с третьими группами информационных входов первых регистров первого и четвертого блоков формирования входных воздействий соответственно,входы блокировки первых делителей частоты первого и четвертого блока формирования входных воздействий соединены с инверсными выходами первых триггеров первого и четвертого блоков формирования входных воздействий соответственно, выходы первых делителей частоты первого и четвертого блоков формирования входных i воздействий соединены с входами синхронизации третьих регистров и входами установки в единицу первых тригеров первого и четвертого блоков фор трования входных воздействий соответственно, прямые выходы первых триггеров первого и четвертого блоков формирования входных воздействий соединены с входами записи вторых делителей частоты первого и четвертого блоков формирования входных воздействий соответственно, выходы вторых делителей частоты первого и четвертого блоков формирования входных воздействий соединены с входами синхронизации четвертых регистров и входами установки в единицу вторых триггеров первого и четвертого блоков формирования входных воздействий соответственно, прямые выходы вторых триггеров первого и четвертого блоков формирования входных воздействий соединены с входами разделения синхронизации первых регистров первого и четвертого блоков формирования входных воздействий, инверсные выходы вторых триггеров первого и четвертого блоков формирования входных воздействий соединены с входами блокировки вторых делителей частоты первого и четвер- тго блоков формирования входных воздействий соответственно, во втором блоке формирования входных воздействий первая и вторая группы выходов второго регистра соединены с первой и второй группами информационных входов первого регистра, третья и четвертая группы информационных входов первого регистра соединены с выходами третьего и четвертого регистров соответственно, выход делителя частоты соединен с входом синхронизации третьего регистра и входом установки в единицу первого триггера, прямой выход первого триггера соединен с вторым входом второго элемента И, выход которого соединен с входом установки в единицу второго триг г ера и входом синхронизации четвертого регистра, прямой и инверсный выходы второго триггера соединены с вторым входом первого элемента И и входом разрешения четвертого регистра соответственно, а инверсный выход первого триггера соединен с входом блокировки делителя частоты, в

5

0

5

0

5

0

5

0

5

третьем блоке формирования входных воздействий первая и вторая группа выходов первого регистра соединены с первой и второй группами информационных входов пятого регистра, группы выходов второго, третьего и четвертого регистров соединены с третьей, четвертой и пятой группами информационных входов пятого регистра, выход делителя частоты соединен с входом синхронизации третьего регистра и входом установки в единицу первого триггера, прямой и инверсный в ыходы которого соединены с вторым входом второго элемента И и входом блокировки делители частоты, выход второго элемента И соединен с входом синхронизации четвертого регистра и с входом установки в единицу третьего триггера, прямой и инверсный выходы которого соединены с вторым входом третьего элемента И и входом разрешения четвертого регистра соответственно, выход третьего элемента И соединен с входом синхронизации пятого регистра и входом установки .в единицу второго триггера, прямой и инверсный выходы которого соединены с вторым входом первого элемента И и входом разрешения пятого регистра соответственно, а вход останова блока синхронизации соединен с входом останова формирователя тестов.

.. Формирователь по п.1, отличающийся тем, что делитель частоты содержит триггер, дешифратор, элемент И и элемент ИЛИ, причем вход пуска делителя частоты соединен с входом установки триггера, вход установки в ноль которого соединен с входом блокировки делителя частоты, выход триггера соединен с вхо- дом разрешения дешифратора, выходы которого соединены с входами элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которого является выходом делителя частоты, второй вход элемента И соединен с входом синхронизации делителя частоты, вход разрешения которого соединен с входом разрешения дешифратора, вход блокировки которого соединен с выходом триггера.

X

12

-09.1 -097 -05.3 -09.//

.2

3.f(3

/5.;

нЬ J

УГ

20

Т12

V2

25

/5

г.

13

1

2

Р

ft

Put.f

X

2.1

72

7/

flLJ

67

7(7

0m Ю

58

59

К 1НМ

70.2

К1

JV

Ч

Ч

62

6J

S6

Ч

,W

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1555705A1 |

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано в радиоэлектронной промышленности в процессе серийного производства микропроцессов. Целью изобретения яв- расширение функциональных возможностей за счет обеспечения формирования тестов для контроля микропроцессорных элементов. Формирователь тестов содержит блок задания режима работы 1, блок синхронизации 2, блоки формирования входных воздействий 3.1,...,3.п, узел выдачи теста 4, генератор псевдослучайных кодов 5. Поставленная цель достигается введением дополнительных блоков формирования входных воздействий, измерением структуры и блока выдачи теста, что позволяет формировать команды различных форматов для микропроцессора, указанного типа. 1 з.п. ф-лы, 9 ил. § (Л 1C со со сх о:

te.7

19

Форматы команд S1 D2J7J

fPu2.9

Редактор Н.Рогулич

Составитель А.Сиротская

Техред И.Попович Корректор Н,Король

Заказ 272/48Тираж 673 Подписное

ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

VLLZ.8

| Четвериков Б.П | |||

| и др | |||

| Вычислительная техника для статического моделирования | |||

| - М.: Советское радио, 1978, с.234, рис.6.1 | |||

| Устройство для задания тестов | 1981 |

|

SU1010632A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-04-04—Подача