1

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и управления, контроля и диагностики.

Целью изобретения является расширение функциональных возможностей за счет формирования переменной частоты следования импульсов с произвольно задаваемым числом импульсов в каждой последовательности и регулируемой длительностью импульсов и повышение надежности его работы за счет исключения возможного искажения первого импульса последовательности при переходе с большей частоты следования импульсов на меньшую.

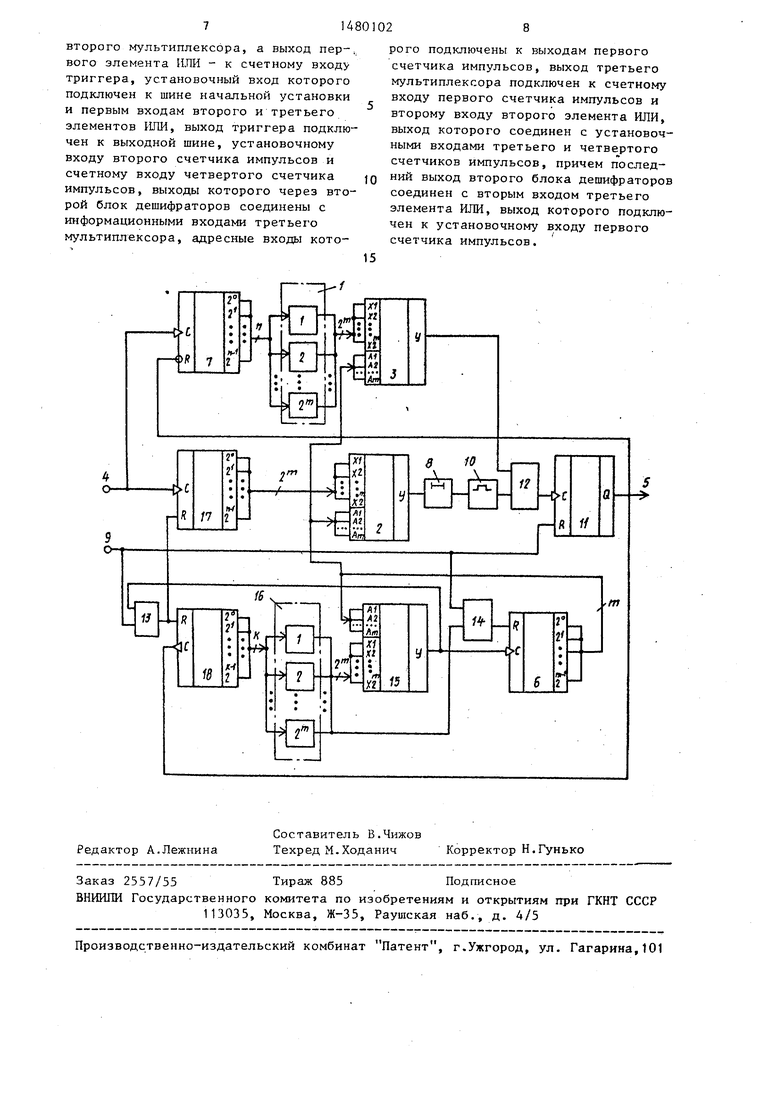

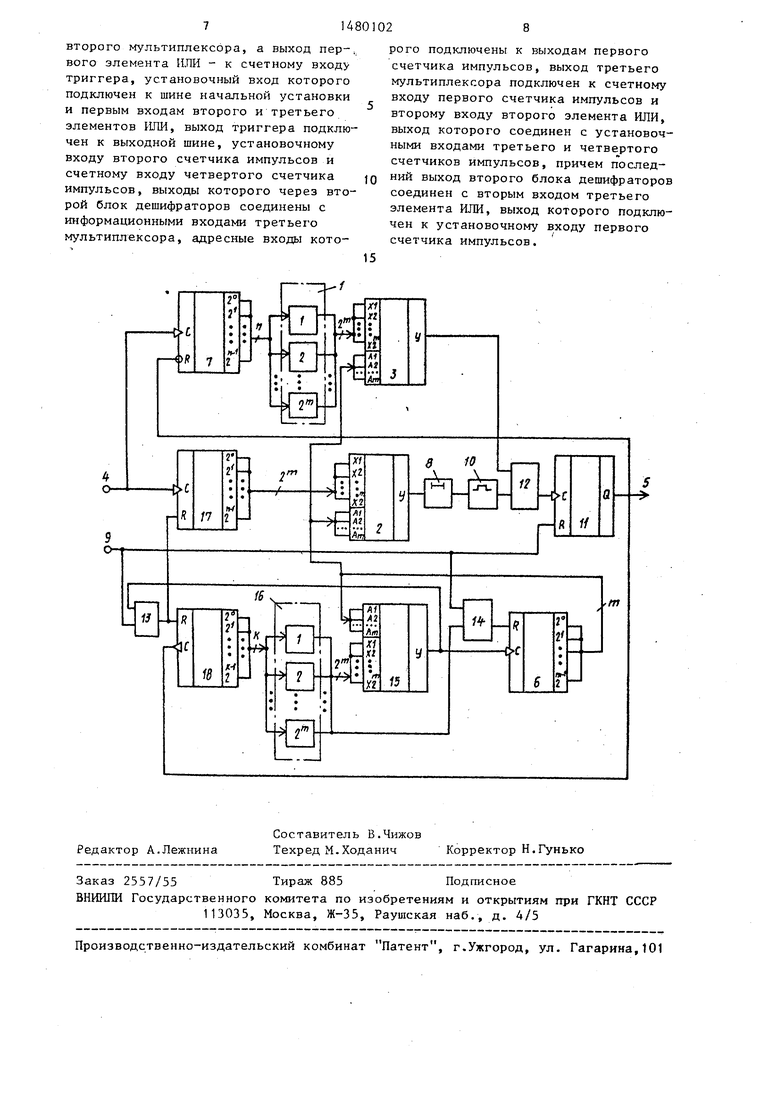

На чертеже представлена функциональная схема формирователя последовательностей импульсов.

Формирователь последовательностей импульсов содержит первый блок 1 дешифраторов, первый и второй мультиплексоры 2 и 3, входную и выходную шины 4 и 5, первый и второй счетчики 6 и 7 импульсов, счетный вход второго из которых подключен к входной шине 4, а выходы через первый блок 1 дешифраторов - к информационным входам второго мультиплексора 3, адресные входы которого соединены с выходами первого счетчика 6 и адресными входами первого мультиплексора 2, элемент 8 задержки, шину 9 начальной установки, одновибратор 10, триггер 11, первый, второй и третий элементы ИЛИ 12,13 и 14, третий мультиплексор 15, второй блок 16 дешифраторов, третий и четвертый счетчики 17 и 18 имЈ

00

to

т14

пульсов, счетный вход перваго из которых соединен с входной шиной 4, а выходы - с информационными входами первого мультиплексора 2, выход которого через элемент 8 задержки и одно- вибратор 10 соединен с первым входом первого элемента 11ЛИ 12, второй вход которого подключен к выходу второго мультиплексора 3, а выход - к счетному входу триггера 11, установочный вход которого подключен к шине 9 начальной установки и первым входам второго и третьего элементов ИЛИ 13 и 14, а выход - к выходной шине 5, установочному входу второго и счетному входу четвертого счетчиков 7 и 18 импульсов, выходы последнего из которых через второй блок 16 дешифраторов соединены с информационными входами третьего мультиплексора 15, адресные входы которого подключены к выходам первого счетчика 6, а выход - к счетному входу первого счетчика 6 импульсов и второму входу второго эле- мента ИЛИ 13, выход которого соединен с установочными входами третьего и четвертого счетчиков 17 и 18 импульсов, причем последний выход второго блока 16 дешифраторов соединен с вторым входом третьего элемента ИЛИ 14, выход которого подключен к установочному входу первого счетчика 6 импульсов .

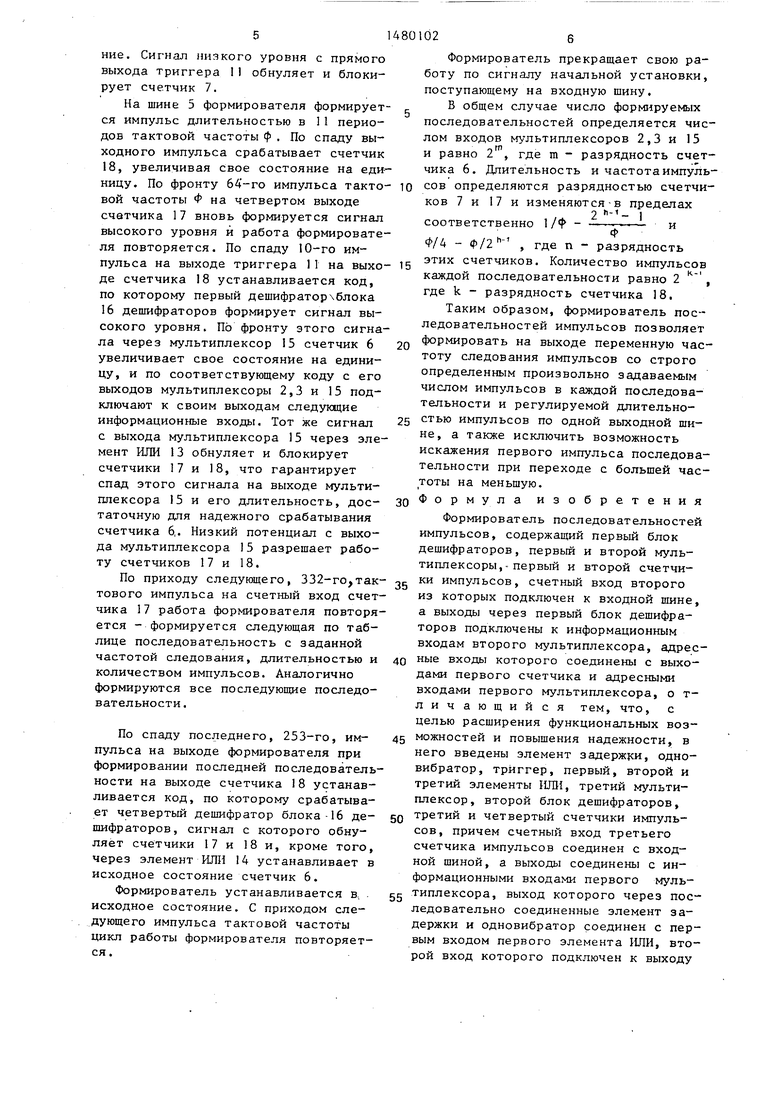

В таблице приведены построение и работа формирователя последовательностей импульсов.

Длительность задержки элемента 8 задержки определяется из необходимости согласования работы счетчиков 7 и 17 и зависит от тактовой частоты Ф, а также от времени срабатывания счетчиков 7 и 12, мультиплексора 2, элемента ИЛИ 12, триггера 11 и одно- вибратора 10. Длительность импульса должна быть минимальной и определяется временем надежного срабатывания выходного триггера 11.

5

01

5 5

0

0

5

0

5

024

Формирователь последовательностей импульсов работает следующим образом.

Импульсы тактовой частоты Ф по шине 4 подаются на счетные входы счетчиков 7 и 17.

Сигнал начальной установки длительностью не менее одного периода тактовой частоты Ф, подаваемый по шине 9 начальной установки на R-вход триггера 11,устанавливает его в исходное состояние. На выходной шине 5 формирователя устанавливается сигнал низкого уровня, снимаемый с прямого выхода триггера 11, этим же сигналом устанавливается в исходное состояние и блокируется по R-входу счетчик 7. Кроме того, сигнал начальной установки через элемент ИЛИ 14 устанавливает в исходное состояние счетчик 6, а через элемент ИЛИ 13 устанавливает в исходное состояние и блокирует счетчики 17 и 18.

Мультиплексоры 2,3 и 15 в соответствии с нулевым кодом, снимаемым с выходов счетчика 6 на свои адресные входы, подключают к выходам первые информационные входы. По спаду сигнала начальной установки импульсы так- |товой частоты Ф поступают на счетный вход счетчика 17. По фр онту 16-го импульса тактовой частоты Ф на четвертом выходе счетчика 17 появляется сигнал высокого уровня длительностью в 16 периодов тактовой частоты Ф. Этот сигнал, пройдя через мультиплексор 2 и элемент 8 задержки, поступает на вход одновибратора 10, который формирует импульс определенной минимальной длительности, поступающий через элемент ИЛИ 12 на счетный вход

триггера 11. i

Последний устанавливается в единичное состояние. На шине 5 формирователя формируется сигнал высокого уровня, снимаемый с прямого выхода триггера 1I, разрешая по R-входу работу счетчика 7. Отсчитав десять следующих импульсов (по фронту 26-го импульса тактовой частоты Ф от начала работы формирователя по спаду сигнала начальной установки), счетчик 7 устанавливает на своих выходах код, по которому дешифратор блока 1 дешифраторов формирует импульс длительностью в период тактовой частоты Ф. Этот импульс, пройдя через мультиплексор 3 и элемент ИЛИ 12, устанавливает триггер 11 в нулевое состоя51

ние. Сигнал низкого уровня с прямого выхода триггера 11 обнуляет и блокирует счетчик 7.

На шине 5 формирователя формирует- ся импульс длительностью в 11 периодов тактовой частоты ф, По спаду выходного импульса срабатывает счетчик 18, увеличивая свое состояние на единицу. По фронту 64 -го импульса такто- вой частоты Ф на четвертом выходе счетчика 17 вновь формируется сигнал высокого уровня и работа формирователя повторяется. По спаду 10-го импульса на выходе триггера 11 на выхо- де счетчика 18 устанавливается код, по которому первый дешифраторхблока 16 дешифраторов формирует сигнал высокого уровня. По фронту этого сигнала через мультиплексор 15 счетчик 6 увеличивает свое состояние на единицу, и по соответствующему коду с его выходов мультиплексоры 2,3 и 15 подключают к своим выходам следующие информационные входы. Тот же сигнал с выхода мультиплексора 15 через элемент ИЛИ 13 обнуляет и блокирует счетчики 17 и 18, что гарантирует спад этого сигнала на выходе мультиплексора 15 и его длительность, дос- таточную для надежного срабатывания счетчика 6,. Низкий потенциал с выхода мультиплексора 15 разрешает работу счетчиков 17 и 18.

По приходу следующего, 332-го,так- тового импульса на счетный вход счетчика 17 работа формирователя повторяется - формируется следующая по таблице последовательность с заданной частотой следования, длительностью и количеством импульсов. Аналогично формируются все последующие последовательности.

По спаду последнего, 253-го, им- пульса на выходе формирователя при формировании последней последовательности на выходе счетчика 18 устанавливается код, по которому срабатывает четвертый дешифратор блока-16 де- шифраторов, сигнал с которого обнуляет счетчики 17 и 18 и, кроме того, через элемент ИЛИ 14 устанавливает в исходное состояние счетчик 6.

Формирователь устанавливается в исходное состояние. С приходом следующего импульса тактовой частоты цикл работы формирователя повторяется.

2 h-i , 4

1026

Формирователь прекращает свою работу по сигналу начальной установки, поступающему на входную шину.

В общем случае число формируемых последовательностей определяется числом входов мультиплексоров 2,3 и 15 и равно 2ГП, где m - разрядность счетчика 6. Длительность и частота импульсов определяются разрядностью счетчиков 7 и 17 и изменяются-в пределах

о h-1.

соответственно I/Ф Ф/4 - , где п - разрядность этих счетчиков. Количество импульсов каждой последовательности равно 2 , где k - разрядность счетчика 18.

Таким образом, формирователь последовательностей импульсов позволяет формировать на выходе переменную частоту следования импульсов со строго определенным произвольно задаваемым числом импульсов в каждой последовательности и регулируемой длительностью импульсов по одной выходной шине, а также исключить возможность искажения первого импульса последовательности при переходе с большей частоты на меньшую. Формула изобретения

Формирователь последовательностей импульсов, содержащий первый блок дешифраторов, первый и второй мультиплексоры,- первый и второй счетчики импульсов, счетный вход второго из которых подключен к входной шине, а выходы через первый блок дешифраторов подключены к информационным входам второго мультиплексора, адресные входы которого соединены с выходами первого счетчика и адресными входами первого мультиплексора, о т- личающийся тем, что, с целью расширения функциональных возможностей и повышения надежности, в него введены элемент задержки, одно- вибратор, триггер, первый, второй и третий элементы ИЛИ, третий мультиплексор, второй блок дешифраторов, третий и четвертый счетчики импульсов, причем счетный вход третьего счетчика импульсов соединен с входной шиной, а выходы соединены с информационными входами первого мультиплексора, выход которого через последовательно соединенные элемент задержки и одновибратор соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу

второго мультиплексора, а выход пер-, вого элемента ИЛИ - к счетному входу триггера, установочный вход которого подключен к шине начальной установки и первым входам второго и третьего элементов ИЛИ, выход триггера подключен к выходной шине, установочному входу второго счетчика импульсов и счетному входу четвертого счетчика импульсов, выходы которого через второй блок дешифраторов соединены с информационными входами третьего мультиплексора, адресные входы кото

рого подключены к выходам первого счетчика импульсов, выход третьего мультиплексора подключен к счетному входу первого счетчика импульсов и второму входу второго элемента ИЛИ, выход которого соединен с установочными входами третьего и четвертого счетчиков импульсов, причем последний выход второго блока дешифраторов соединен с вторым входом третьего элемента ИЛИ, выход которого подключен к установочному входу первого счетчика импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1987 |

|

SU1476474A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1985 |

|

SU1367036A1 |

| Цифровое устройство для обработки информации частотных датчиков | 1987 |

|

SU1525609A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Программируемый многоканальный формирователь серий импульсов | 1991 |

|

SU1775846A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Устройство для ввода информации (его варианты) | 1985 |

|

SU1290286A1 |

Изобретение может быть использовано в устройствах автоматики и управления, контроля и диагностики. Цель изобретения - расширение функциональных возможностей за счет формирования переменной частоты следования импульсов со строго определенным произвольно задаваемым числом импульсов в каждой последовательности и регулируемой длительностью импульсов и повышение надежности его работы за счет исключения возможного искажения первого импульса последовательности при переходе с большей частоты следования импульсов на меньшую. Цель достигается тем, что в формирователь последовательности импульсов введены последовательно соединенные счетчик, блок дешифратор, мультиплексор, формирующие количество импульсов в последовательности, а также введены счетчик, элемент задержки, одновибратор, элемент ИЛИ, триггер. 1 ил.

| Формирователь последовательности импульсов | 1984 |

|

SU1226619A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-15—Публикация

1987-06-04—Подача