L...

««Јь

| название | год | авторы | номер документа |

|---|---|---|---|

| Станция локальной сети | 1990 |

|

SU1824640A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1566332A1 |

| Устройство для отладки программ | 1988 |

|

SU1624460A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1989 |

|

SU1698907A1 |

| Устройство интерполирования сигналов телевизионного изображения | 1989 |

|

SU1690213A1 |

| Программируемый таймер | 1987 |

|

SU1441407A1 |

| Устройство для ввода информации | 1986 |

|

SU1372317A1 |

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

| Устройство для сопряжения ЭВМ в сетях | 1986 |

|

SU1381535A1 |

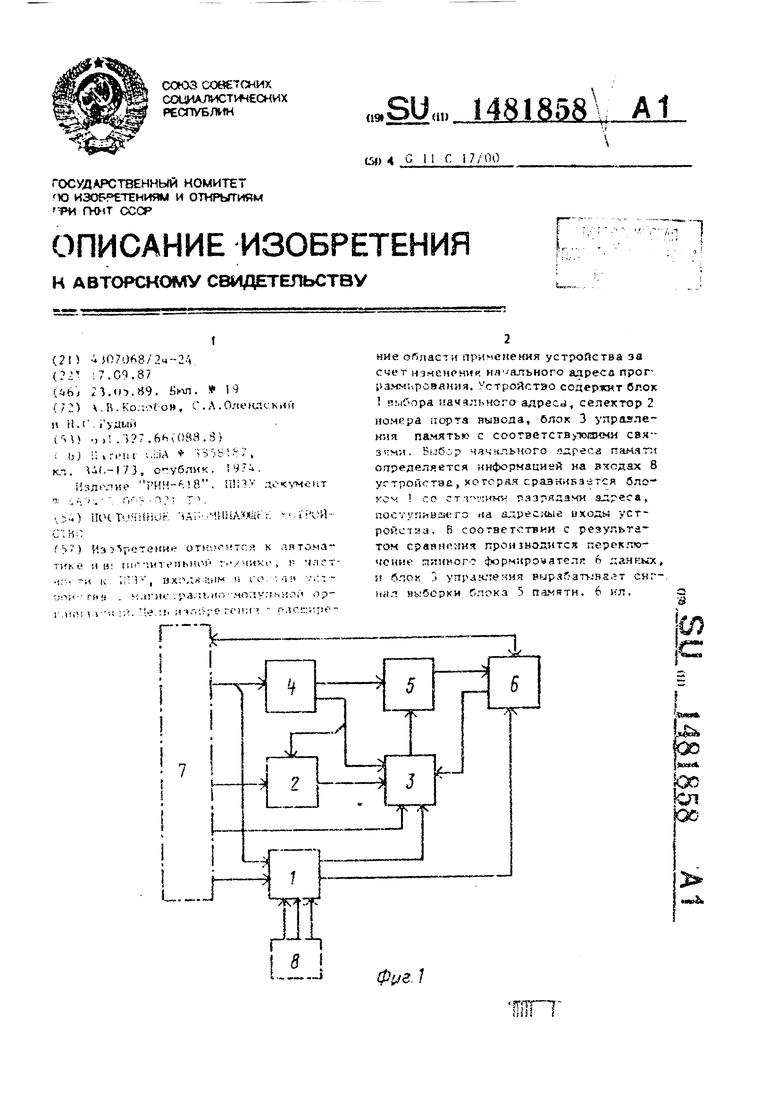

Изобретение относится к автоматике и вычислительной технике ,в частности, к ППЗУ, входящим в состав устройств с магистрально-модульной организацией. Цель изобретения - расширение области применения устройства за счет изменения начального адреса программирования. Устройство содержит блок 1 выбора начального адреса, селектор 2 номера порта вывода, блок 3 управления памятью с соответствующими связями. Выбор начального адреса памяти определяется информацией на входах 8 устройства, которая сравнивается блоком 1 со старшими разрядами адреса, поступившего на адресные входы устройства. В соответствии с результатом сравнения производится переключение шинного формирователя 6 данных, и блок 3 управления вырабатывает сигнал выборки блока 5 памяти. 6 ил.

I

i 8

.. |

Ф/г 7

TilTT148

;l ь Г рстеняе t-i UK гитек к автоматике и рччнсянтельмой техник, в частности h программируемым постоянным эапо- минамщим устройствам, входящим в состав микропроцессорных систем с маги- страпьно-модульной органичациеП.

Целью изобретения является расширенно области применения устройства яа счет обеспечения ичмекенни начального адреса программирочлння постоянного чапсмикамшего устройства.

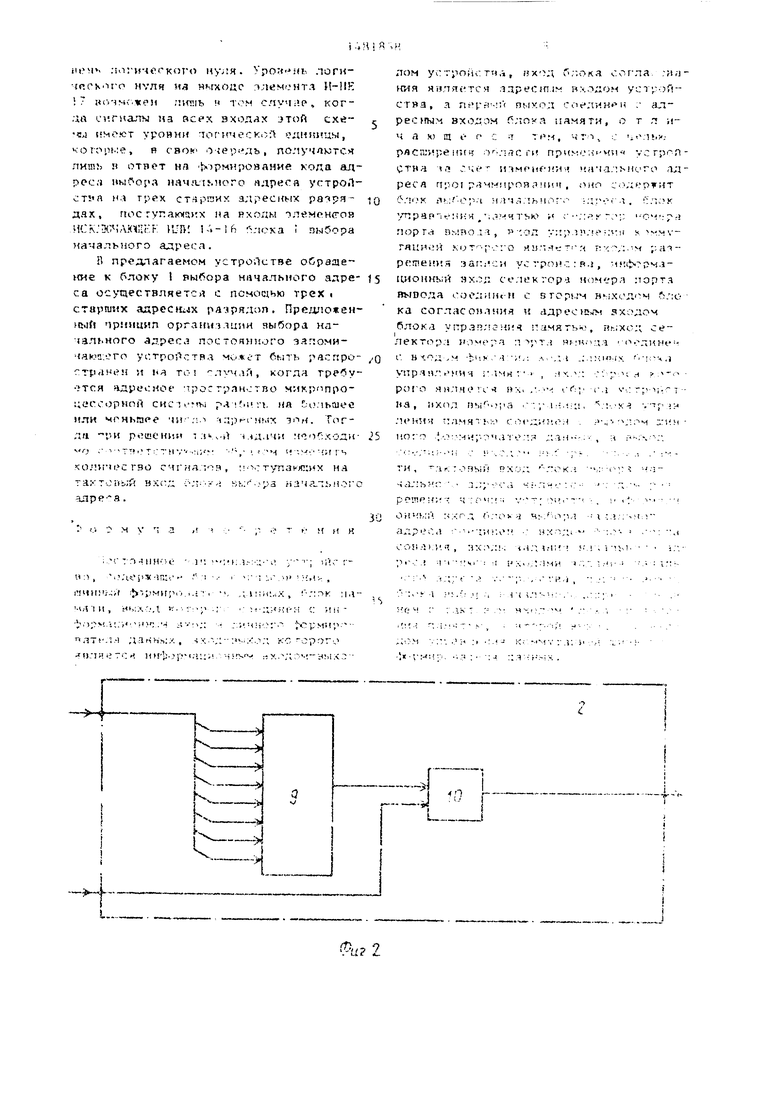

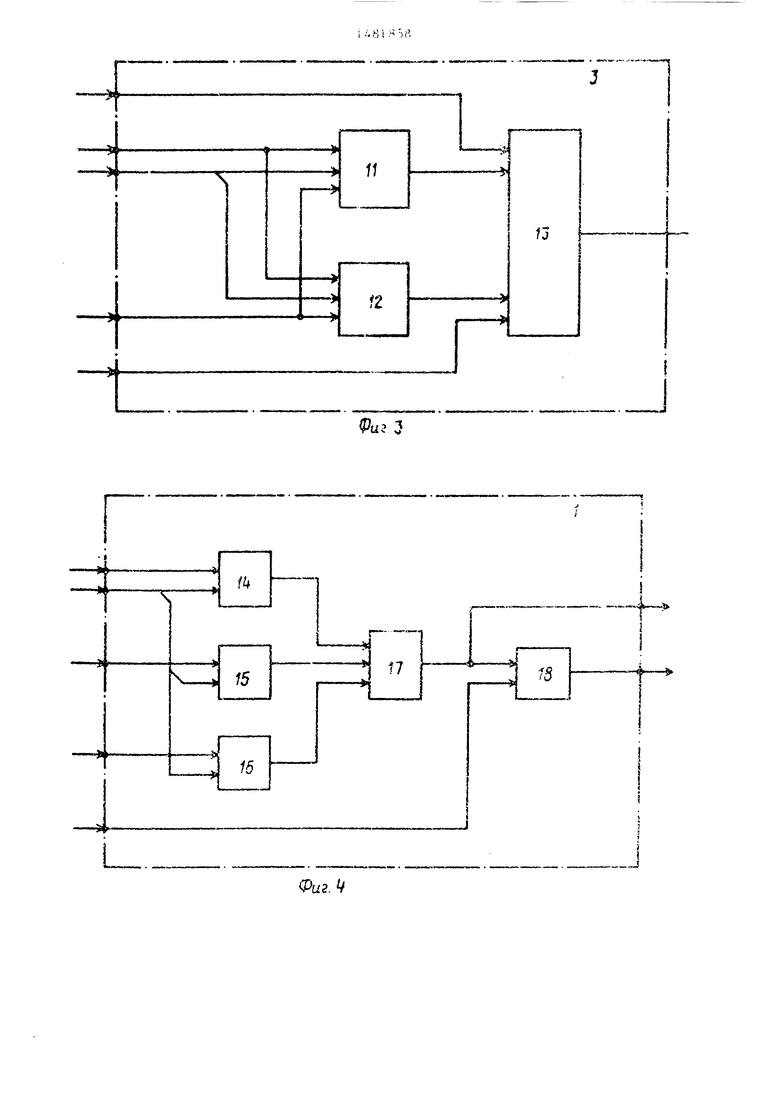

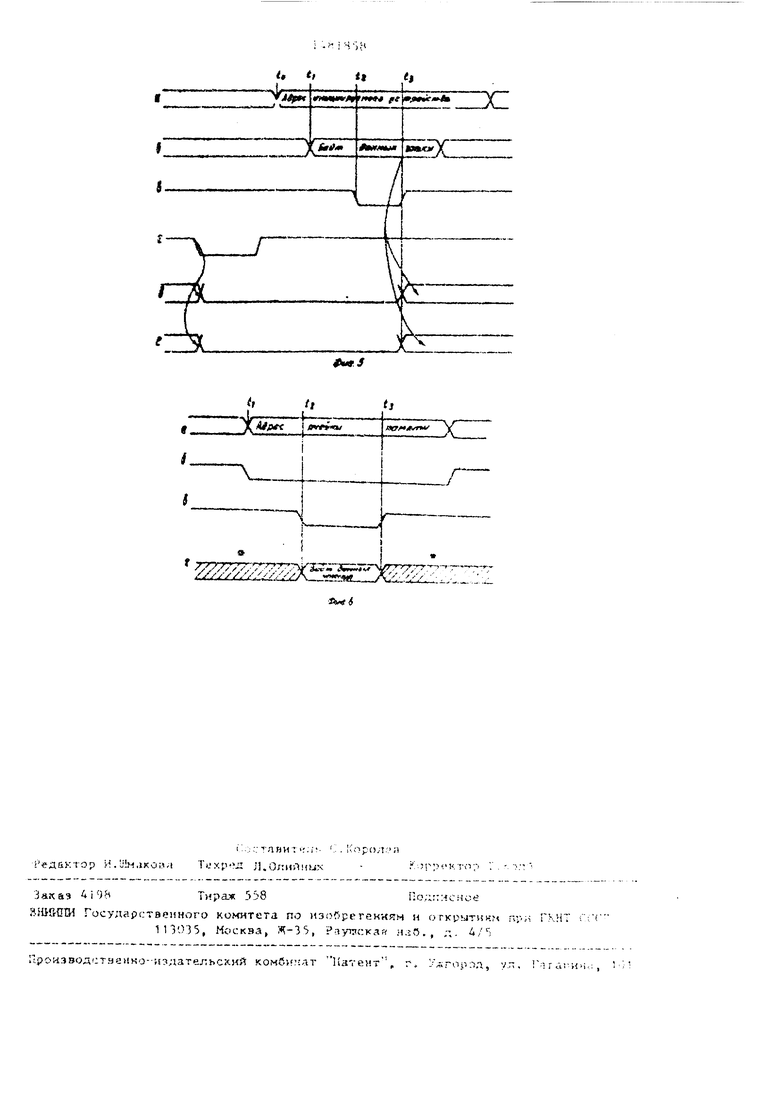

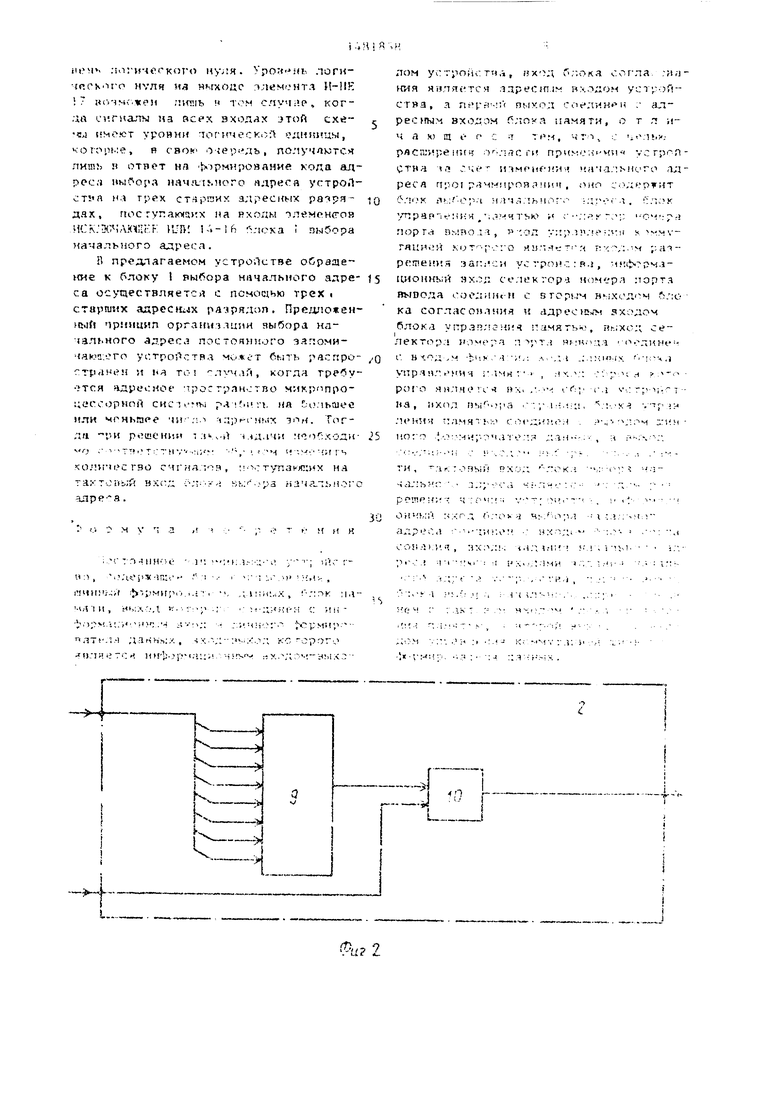

На фиг. I представлена блок-схема постоянного эапоминянмцего устройства; на фиг.2 - функциональная схема селектора номера пор га пывода; на фиг.3 - функционалы я ч схема блока управления памятью; на фиг.ч - фунх- циональная схема блока выбора начального адреса; на фиг- i време-ыые анаграммы работы устройства « роким 1 аьмлора етрлниць: памя я я в реаиме чтения HI фор«а::ни д-чнные че определены) .

Программируемое т- яннпс запоми- н.к т; ее v j . - ;. /«-ч- Г .ж БЫ- бора начального адро з, селектор 2 нсмеря порт .,zл, 3 управления ЛамЧТЬ1, .-« с-ог--;з- -.у -it.-j ff .

57 ч- с-- г. .. - , р SjTO.-ib 6 ;;ль -1}их. vT:pau .м.1лы устрой- стал (jyp7 M,V;V цомтр.-щького nycsirrcopa, .1 ягг(Л м .:i алрес р.осту- ::че- нл хо;;м В vc -/ i f-цч.

«лолтор J но«. rin-гд ьмлс-ла

со -ой- я-д -j- . Н-Ч1- 9 я .«лемгнгл И : .

;. 3 уп залечнч г.тия Ь -о состоит из триггеров : я 2 и дспг,;фра- тора 13.

Влок начального адреса состоит к трох Ч. гов ПГКЛЮЧАЮ- Ц7: . ,1V. Si-IS тт--м--г -а 17, Mcurj И.Г/ Я.

Плох 5 памяти f:, четыре страчиим памяти, гчнг чс1 :to мкости, i-f :f jc;;4«; РЛИИ- VI а;. HV .лтсгь, каж дач из ютпрых ::р : of Of матрицу 1ЛСМОНТПВ ::ртг.1ммируем.1Х

П ТО«ННьЛЕ ЧЦГТ TMHi - 1K4v Vf7pOfl T4 С

дя/мя управляу яз н -г-лячи.

Г-лок согл1 со лняч выполнен на лс нческлх -j. ifMfH rax ПК, ИМРЮИИХ большой коэффициент ра1Я«тзлеяня по вь ходу, лля поа,Ллемня нагрузочной с :ог.оСнссти Адресной л ним михропро- Uj-ccepHofl систе.ны, П янный формярона- 6 реализован на инверти83

руюшнх элементах с тремя состоя)гич- ми по выходу, управляющие входы которых позволяют организовать двунаправленный режим передачи данных.

Устройство работает в двух режимах: в режиме выбора стрянииы блока памяти и в режиме чтения информации. Аппаратное решение позволяет О.-.УQ ществлять переключение страниц Ллокл 5 памяти ня программном урорн. Чи.:- ло струни:: зависят от сложности решаемых задач и мотет быть доведено до . Ланнын режим выбора

5 блока 5 памяти (фнг.5) осуществляется следующим образом.

На устройстве по сигналу Сброс (фиг.5г), поступающему на вход сРроса блока 3 управления памятью, уста0 назлнвзетоя исходно состояние

фиг.Ьд,е. рогвегствукхцее выбору нулевой страницы блока 5 памяти. Переход микропроцессорной системы я ис- холное ссстсяние, вызваннь Я сигналом

5 СОрос, всегда сопровождается зь:5о- Р7м v-.i-Br-. i страницы блока памяти и не требует осуществления никаких предварительных операций npvf работе г устройство, которые обчзат льчг

0 р .VT--: .,ри переходе - Vl. ..rp,i- блока памяти на другую и ре- жзгме выбора страницы.

Номер страницы блока f памчтн оп- ред ется vna. CTuvn рачрпда«н ллк- , поступах-лнми на вход выборе страницы .i 3 управления ланч1-1- -, с ni-лсода важного формирозате.-т данных. На адресном нхоае устройо-ва г

момент времени to (Ьосмноуетсч код a;t- JQ реса постоянного заломннамптегсэ устройства (.фиг.За), который поступает череч блох 4 согласования на информационным яхса селектора номера порта вычода. Н следующий момечт яре- 4§ Me.iK с, си1-кал управления, пес ия с второго выхода блока выбпр. начального адреса на вход уг.ра.-.рнч- ксммутйцие пгянного фоемяроа, г данных и . ответствующнЛ уровчк глгя- чесхой единицы, приводит к отхрынг- НИЧ5 последнего я прохоядсни э (пчтор- мацни о выборе страницы памяти с гн- формацнонного входа-пыхода устройства на вход выбора страницы Ьлока 3 управления памятью (фиг.Зб). В момент времени t,, ка вход управле1тя коммутацией селектора 2 номера порта вывода поступает упразля оашй сигнал записи элемента яывода. Ссзокупностъ

5

50

юго упрлн и С1 гч 1гд рт ipoiaem записи, -юс rvnaioiict о рк гЛ РХОД ттемента И 1П, и curm м элемента И-МЧ 9 (фиг.2), активный уровень которого формируйся в ответ на раниты ьм к эд ад; era то-тсмчногс запоминаете о устройства, вьпыяает формирование на выходе элемента И 10 и ооотпстствонно 1 а выходе селектора потеря пор «-л вмнода ичпупыа, vpo- яень которо о соответствует потенциалу логического , а длительность равна длительности управляющего CHI - нала записи элемента вывода (фнг.Зв) По чаднему нарастающему фронту ттого импульса производится фиксапня кода данных и вибор номера матрицы памяти, (фн . ,е) в 3 праваеиич па- мя.ью. а ITOM ретг-ч выбора матрицы Г тка г ти-анчива тгя я даль- си РЬ.ПРТНЯР с н речгнм чтения ци 1 I-JHI . М

л ддрг ним n i,t- vv;o.i44i яна- . чин с4 , л i ч , . ii ь мо. нт вррчеНИ i , t V 1 Г(. | К

гр . - - , м-идише

( памчт

PJ э;м л. О г ро

- С М ас ч нч ; ., ) v i; titvi4 я v ,

ГЛЧЧТТ-)

L ,1 , -я i

- I Ч 1М ,1 III II

Г 1 }1 ,1 - J И ( Ч

. Ц ) М ЧЧ t - ( ,10 чч т

-. п.нг ; ллг (-«. i, -ч о v. че-ко;о н% -., f - 1,1 ос i -cii-t

ЛРЧ. rlT ) 1ч . i-

V 1. Ч 11 Т -JCpO б.О RVC1 ОТОК

il

-. а

;i ил

г рки

Ч -

. : |in, ч ,. ,

f I л t ,f

i-Т . fч(

С ) ч , i . ь

ч ; y.fvi i ( . . u a н M. V ,1 i4

.4 V ТЬ . В pi 5 Ч -( , i-K 1 r H ИМН1 t ф(3р 1,,4 n

r Т pi bi O r

( iri ) НК 5-ОРЧ I t, 1 1

sp : - HT 1 ,p IH JC (ЯН Г -, v. ,X РПРЯЯМВ Ч i t ,1 IV I . 1 ji « k f T 1 fc

i. f - i. r1 r m a мбсрs. к i- ,b,. /рглонь ко

Л , i Т . .

дг м - i: г .н: на- т . я заданноi- .. ч ( 1Т-11 п , , г .,,. , (

h 1МЯ

Н, И t ,, . н ч. i ,К

i v . , к м ;,М Л Т ч t Ш Ч -..; I Ь

i i L ч .;

, ii II, Vt (

,ч .. i i HJ 1- т r i -и и гь т ,е ,.1 Ч -Х Н МО,1 Р1 Pti-TJiN U СНЧ7Лf у.фэ тя О цего rvn паля Чтение за- почння)ГЕгих устройстз, что с ответст- чоменту времени t,.

Таким образом, сигнал, сформированный на выходе блока 3 управлеиич пзчятьк, поэзоляе- обращаться к ;тюво- му чяеминту выбранной страницы памя- Tif. Кол адреса, поданный ка вход

р лока памяти, служит для полицип ячеЛ/ и элгчента памяти, а по в- орсм-у управляющему снгкату ос тг;егт- впяется чтение записанной в ней информации.

5 Начальный адрес постоянного ззпо- минаюшего устройства в адресном пространстве микропроцессорной системы определяет блок 1 выбора начального адреса. На его информационный вход

Q по адресной Л1ННС постилают сигналы трех тлршнх адресных разрядов, де BLP влресио - пространство не pccf-мь равчыч части, каждая из кото- P ix -ожет С-ыть яыСрлна облзс ыо раs для постоянного iчпочнчаюшего -рс л i

Вь.р начального гдреса тобой и-i этих -я-тен о v. 4tt. твтчется посред- яоч игналов , OC viax sHv {д входы

r т na4,vbi oro Адреса блока i нлчатьного алресд. 3 ит PXOW по iat -гч «РоичиыЯ

4 Т, i . (jnMvjilp -ЦГН.1- С ЛОГН- Ч ч , р -р .J u я , . , э до чо i -i ,« apcc cS- я с г .j --п ,| - i,i OMHHi.if

, о , -potU -н я в i -, , д},ь ,,Orjpo eccopi o --истечи. При . чодутя , про- :. v ,c- 4v n oкe 1 аыбо- рэ начэтьссто ад, происходит срав- Hei ne .ч -и , постч-таюаих го п. ч a, ы о-ни s j I VOIOB чле- ч(«ч.-ч ; ; . -- i i 4- Ь, с гиг- ( i. 4«i , н охчпнчч i : иг n v

,vl s J hv I . il 1 ЦИ .41.

О ,л , i .( Ul Ч W( H r м р Чц- t H 1 , , КI 1 i. n i WT О -

p- H. i ( г р in , rt ч v к i ч i ит г, от - ченр О1 i J - 1 -I4i 4i- 4.i x: , i ч - i чую- nis PI iv рччненич. fc хпдиие J- i н ч татем

HI НХОД ч |оч« j ч- ,- I j .1Г . I ) ,

;нг in. , ч рартч 1

ч

О

д е . р а

л г Ч б i j п

Г voi t Ht ч{ш .

I-1-1/ ; - ИО .П

tn-tu T г.,

npi t ЧОДЧ- си ri. i ;св , 1C нчег- . ро||(ЛМ 1 И lOi KOT О НЧ Я. % РОЧ - П 1ОГНIOPS ч: о НУЛЯ ил чнхоцс т1 м нтч H-llp

1 wo 14 Л ч 1 гЧ IV I P, итналм на пссх входах этой ехе- « смеют юг нче -к ) дмш цы,

ОГ11М , Р С ВО 0 ДЬ , ПО Ч1МТСЧ

чипр) : ответ на Ј рм ронанир хода ад пс ) ыпоря наччлмюго ядрегя угтроП ni грех cT-ip TMv адресньк дчх, по с гугакиа на Р ли 1енон гов Ч N Ut i- l.-lf- -Me va i начального адреса.

{1 предлагаемом строЛ тве обращение к блоку 1 выбора ничатыюго адре са осуществляет:) с помощью трех « старших адресных разряд п. Пррдлонеи Ы( принцип oprimmmiH нд- MTfHoro алрог n L-оянн jr о эчточи- tHiKis то у i ч M.t.T , pain 4 я Я TI i (, когда 1тгя -uipov not во чяхг-ппро- .«ассоряои CUV. рд ., i НА о ibaiec или чгньгаео in - i jjii-i чм- члн Гог;tl V И рОШСНИИ Л 1 4Д 1. 4rt 1Г)ДН v /-i- т - i,. I. v ;, I t,

O Ui ) i во синя -ч , ч T-v T ai. ш

ТЧ- т tlbf Чм .ii. flMV-S O

гдрр-ч.

. Ч , Л ,

i

т i i

М ),

) И .

( , I 1

; i

. t

tl - - р )- ,

. v k i , v -

..,

lj С А„

дТ)м у pofu тч i, Г or та ,, ь{ия Я|Ля«-геч nptTini н у т r ifi сгва, я л ч н ( iie. 1Д r i° . памяти, Р т ,1

Ч Л Ч) Д I- %7 РЧ, i Т 1 г .t 1 У

ряст; 1; е r TCIK при1- vbi Ct и iMdif ня аи HI. 1Д ре, я a; oi р 11пн, ii(i i f отлт

s ir K Л 1 ) 1 I i тпЧ .Л1Г

- ч . - SK r юр г -t ч TI х i , Р тд

-ЯЦИ. Ч ( О ЯЧ 1ррте1«) ч sar « ,1 )

Ч

I Г Ч V4 -

11 М t П R i, ф.-рм г

15 ЦЛОННЬИ , tflUk Op Л Ч ) 1 1ОРТЧ

Bt-mo ia i и i. nropi M H xt л м - с ка соп1СО1пчлд ч sx Р TOh i . гр з с ii4 ам ь , Хч ; се

ТеК(р 1

I Ь ,, v

vnp лм poi л ч и -ч

f i t- i

I -IH

v Ч

Ч Н i

;i о тине

I 14л )

на, .ixm , ,

Н 1 14 Ч i ( ° J т -1., 41

i 4 1 (

л i Ч411

,( О t

1 i It I I чН if,)

ij j ь

41

1

f

г

tt

f

7 7777Г ПЈе Г&

//luvA,

Авторы

Даты

1989-05-23—Публикация

1987-09-17—Подача