Изобретение относится к вычислительной технике, а именно к устройствам обнаружения ошибок ь блоках памяти.

Цель изогреги. ::я - повышение надежности устройст«г.

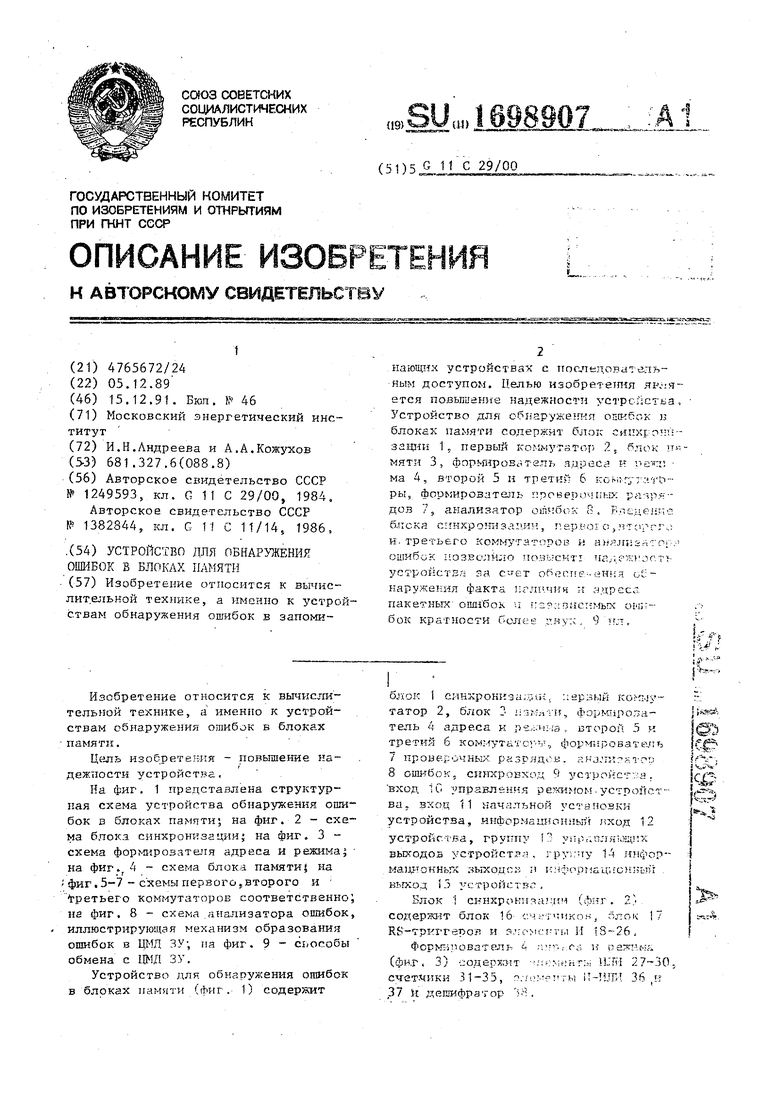

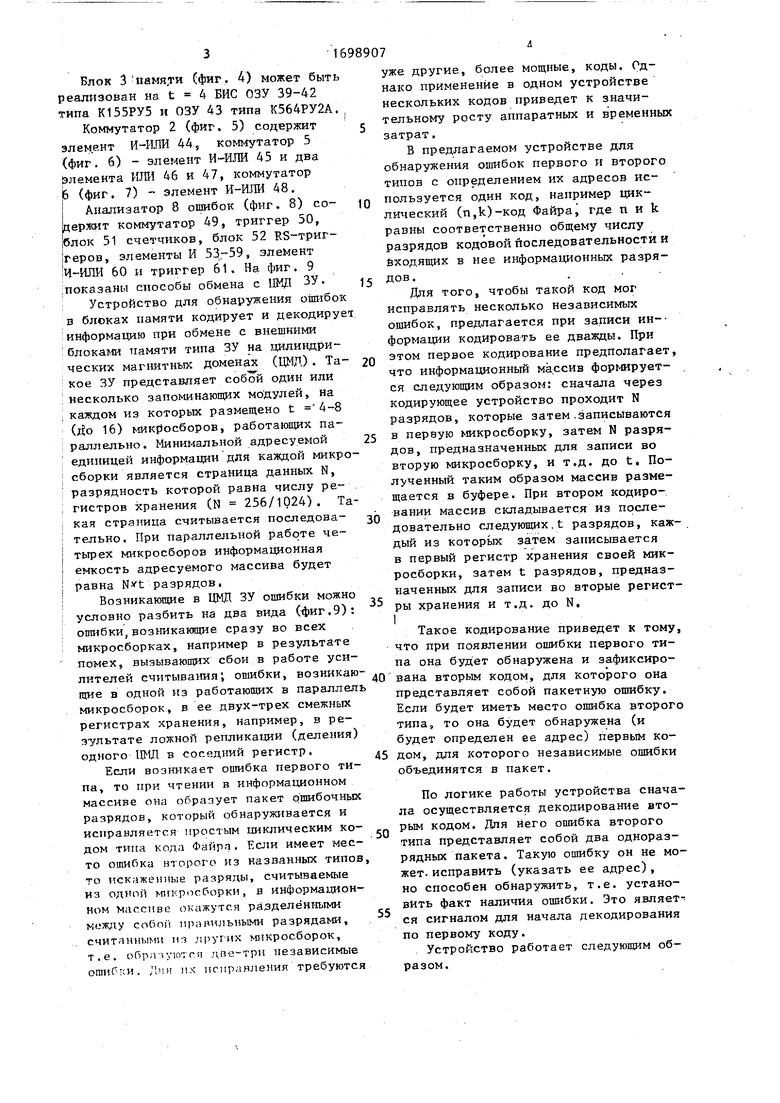

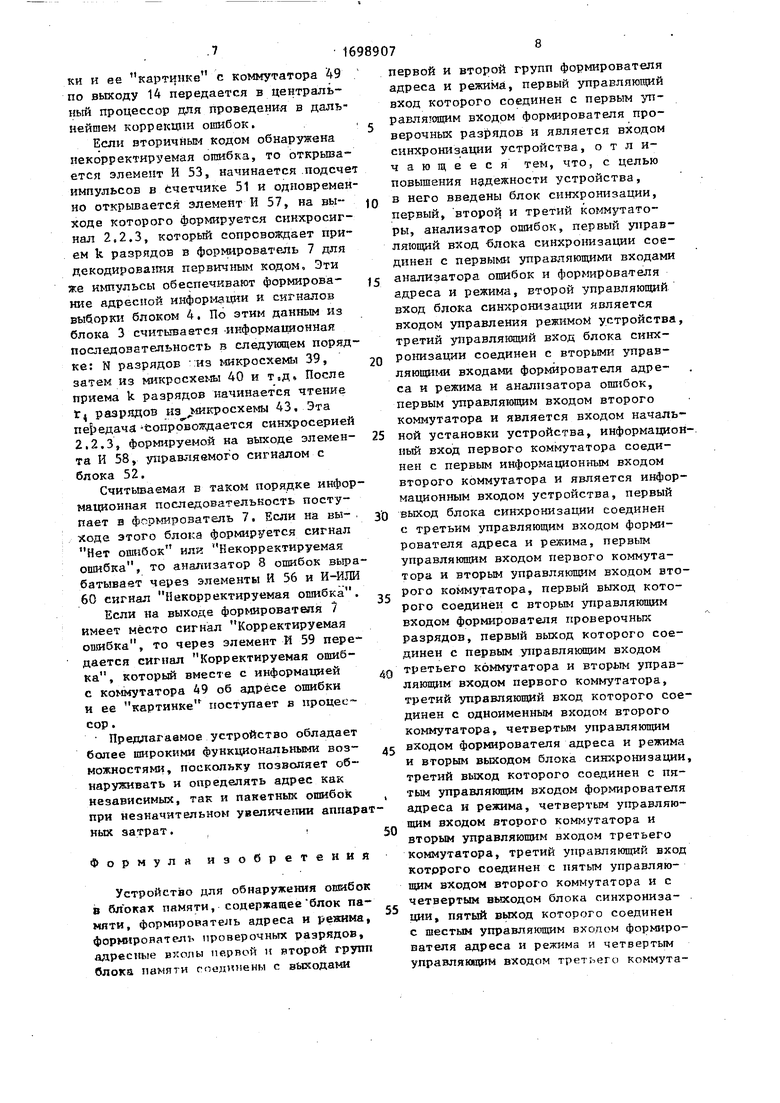

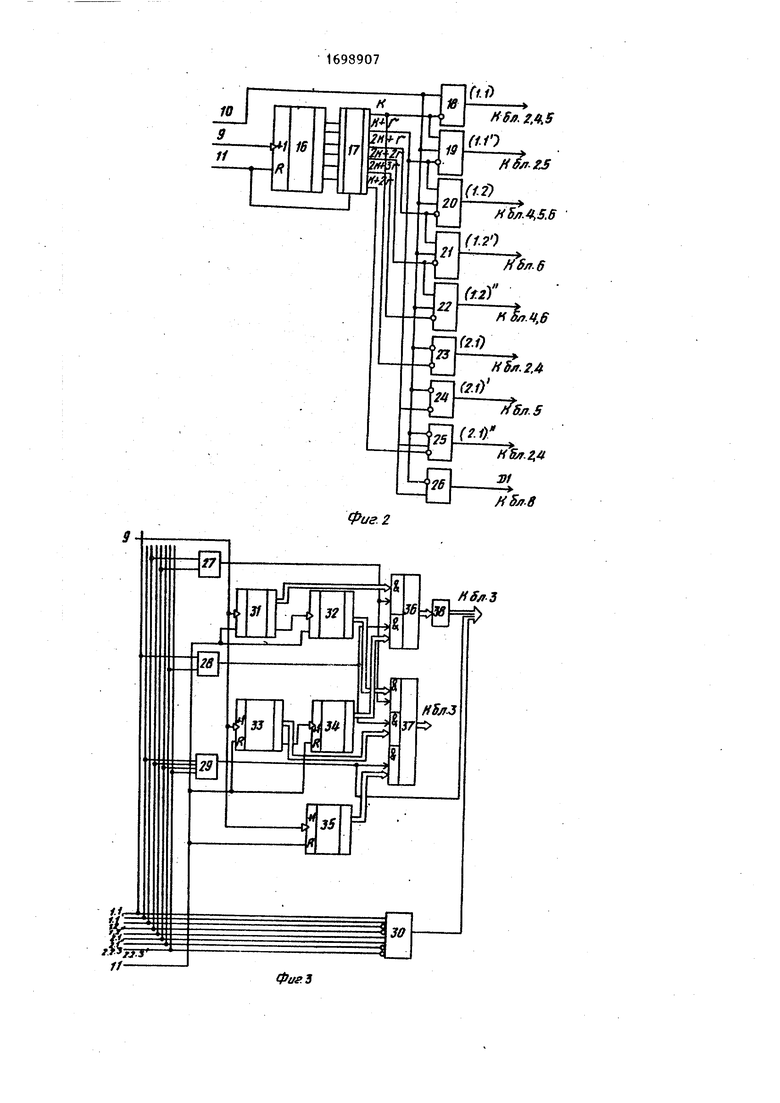

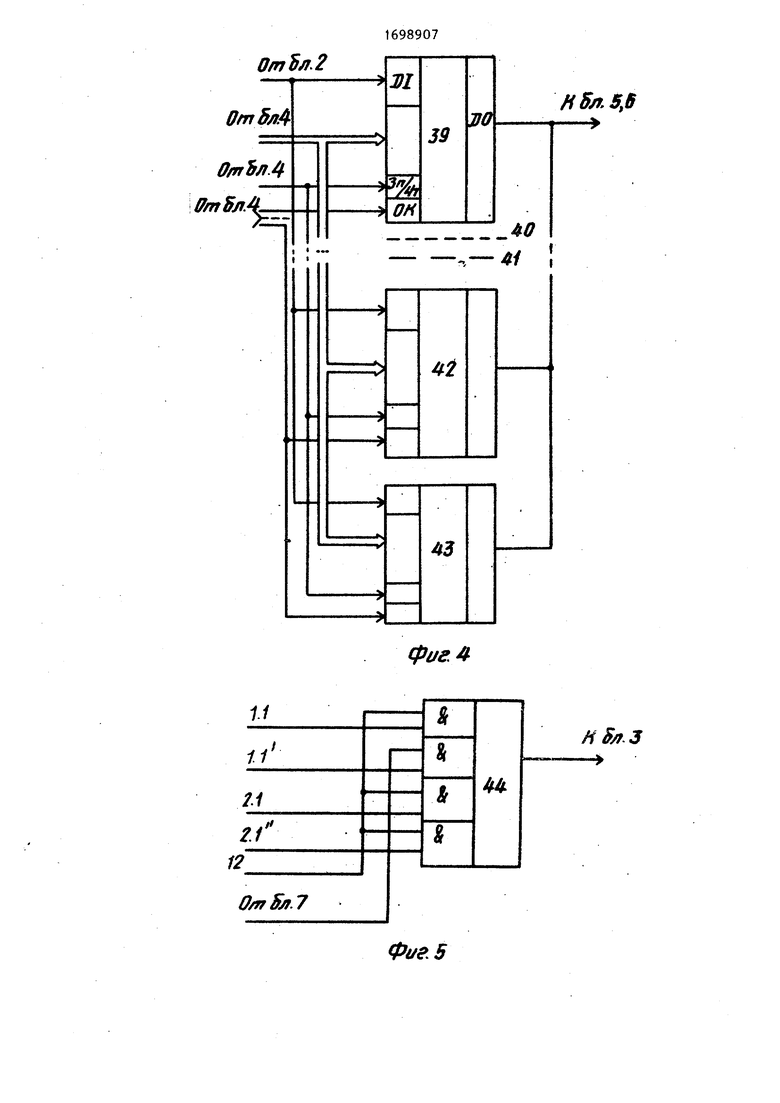

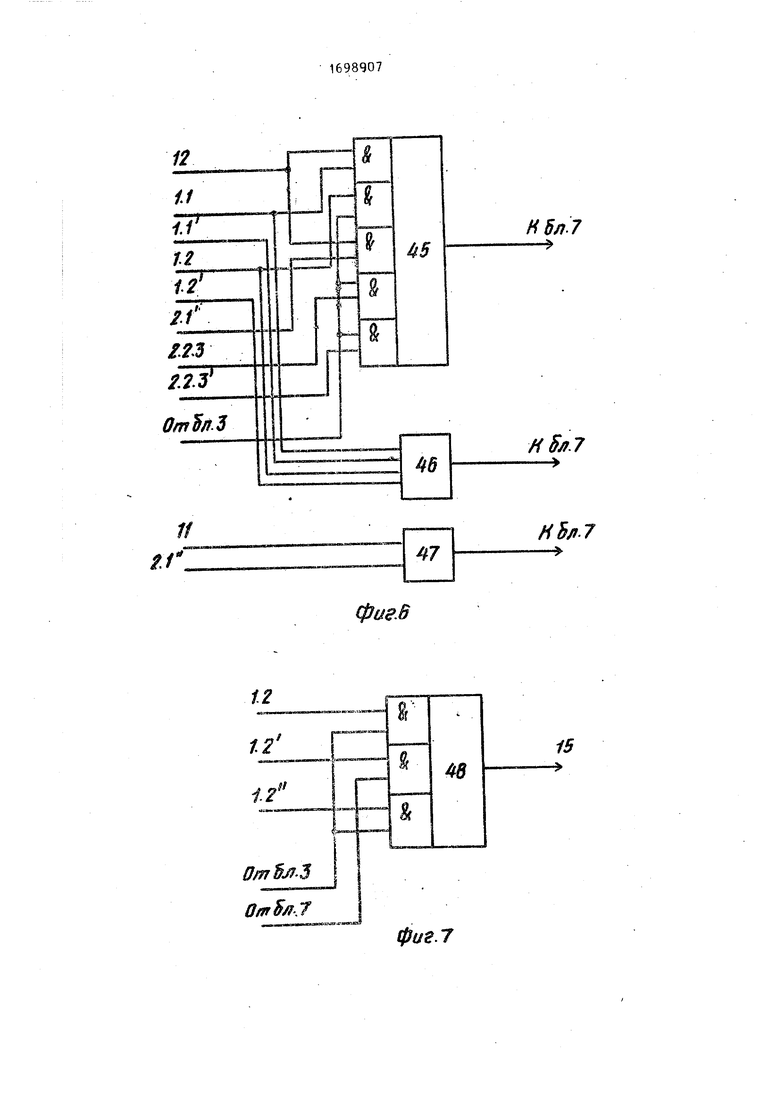

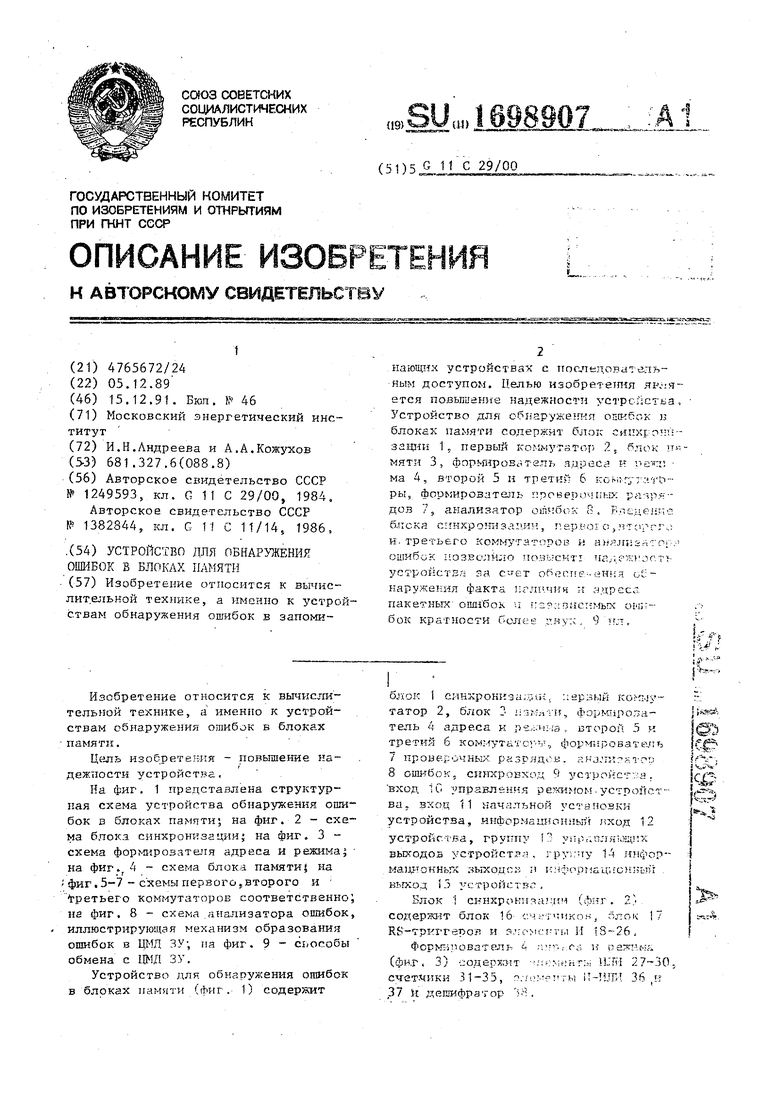

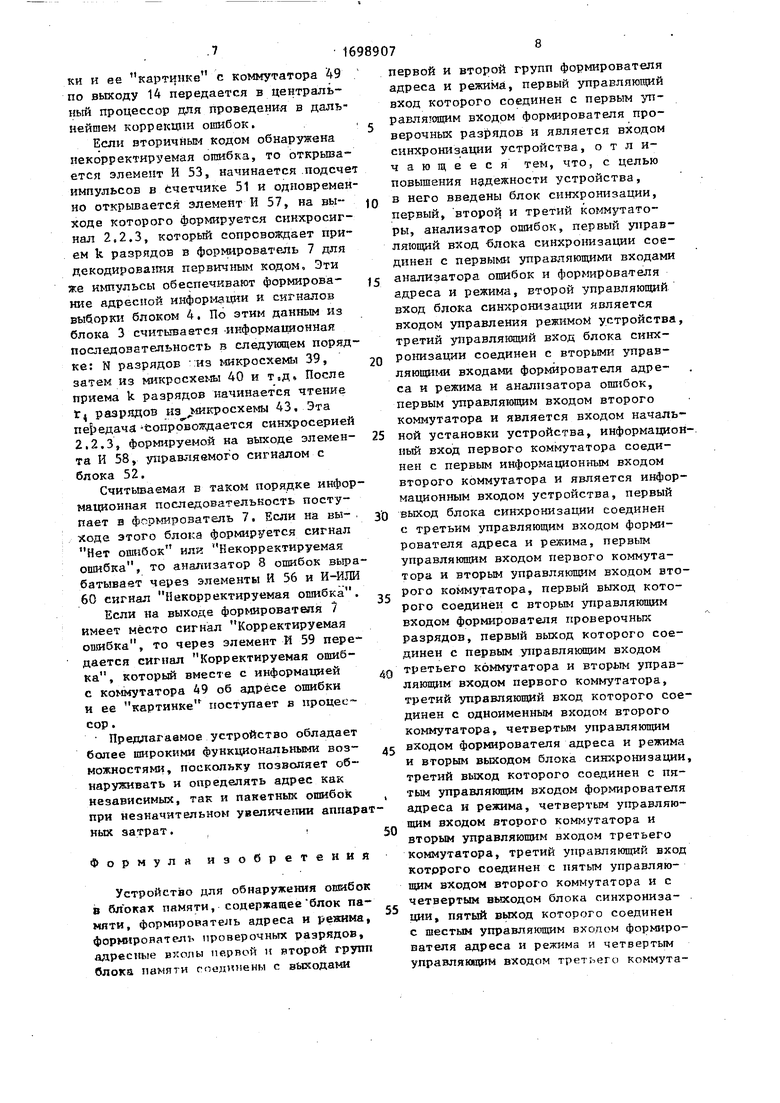

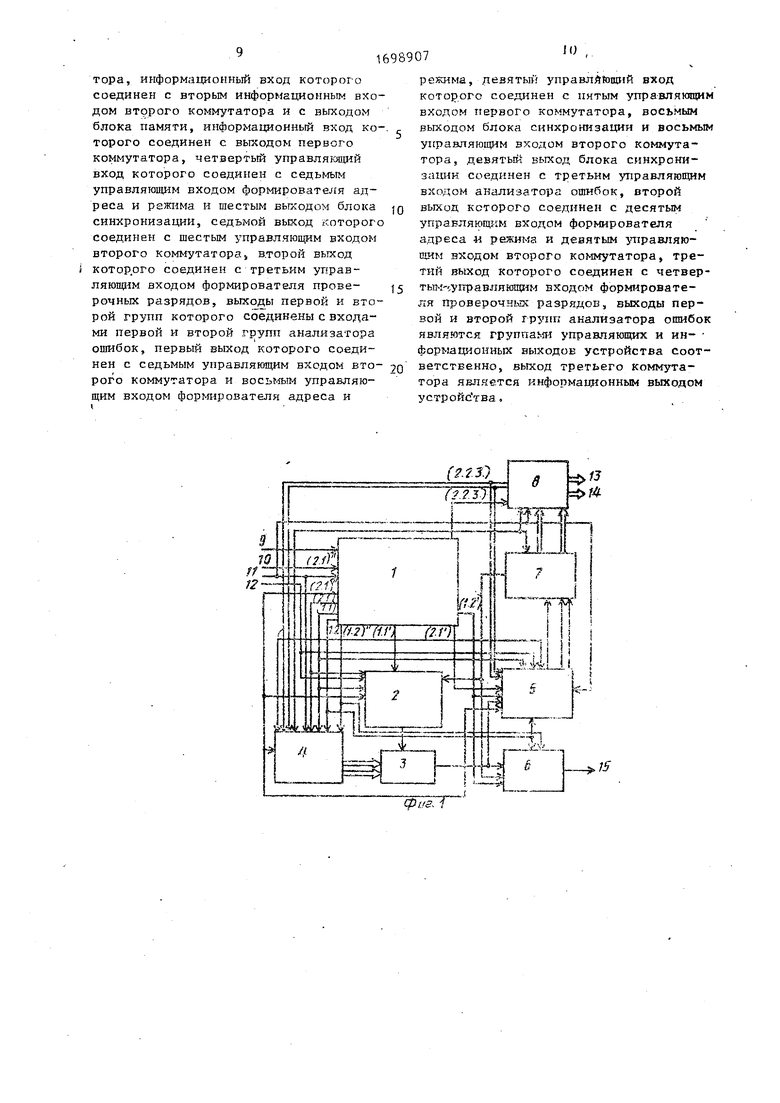

На фиг. 1 представлена структурная схэма ус ройгтва обнаружения ошибок а блоках памяти; на фиг. 2 - схема блока синхронизации; на фиг. 3 - схема формирователя адреса и режима на фиг. 4 - схема блока памяти на фиг.5-7 - схемы первого8второго и третьего коммутаторов соответственно на фиг. 8 - схема анализатора ошибок, иллюстрирующая т еханизм образования ошибок в ЦИЦ НУ; на фиг. 9 - способы обмена с 11МД 3V.

Устройство для обнаоукения ошибок в блоках памяти (. Ьиг . 1) содержит

&

блок I синхроннзсч,ги,, ар ,ый ко /- татор 2, блок 2 1.11 ,t нч i--к «

т ель адреса к ч , второГ 5 и1§Ь

третей 6 . i ci , фпрм ь

7про в е-ручных 1%ч.зрчл1 ° . н :; - п л

8ошибсп , син:-:р вход ci -wci .4-11-7 ч j. вход 1С з пвавленчя ус1.поиг- ва, вхоц 11 начальной усг ячейки устройства, ин4ор.мац1-ч наыт : ход 12 устроит iBa, гругпу Р у.-.i м . выходов усгройстп, j р у маи;- онньгх лыхоигв и i nv аи, :, г выход S3 vi ,

Блок 1 ci- нхроFinai лм -т . Г содержит блок 1о - .-г ч 17 RJi-ттятг inop и 3 -к i , i И 5-Г6

г ani г . . .. (фьг, 3) .оцегяит-. r,- n T I ,: iOсч-етчики 31-35, , ь . 37 U дешифратор .

-1 Л

Блок 3 памя.ти (фиг. 4) может быть реализован на t 4 БИС ОЗУ 39-42 типа К155РУ5 и ОЗУ 43 типа К564РУ2А.

Коммутатор 2 (фиг. 5) содержит элемент И-ИЛИ 44, коммутатор 5 (фиг. 6) - элемент И-ИЛИ 45 и два элемента ИЛИ 46 и 47, коммутатор 6 (фиг. 7) - элемент И-ИЛИ 48.

Анализатор 8 ошибок (фиг. 8) содержит коммутатор 49, триггер 50, блок 51 счетчиков, блок 52 RS-триг- геров, элементы И 531™59, элемент И-ИЛИ 60 и триггер 61. На фиг. 9 показаны способы обмена с НМД ЗУ.

Устройство для обнаружения ошибок в блоках памяти кодирует и декодируе информацию при обмене с внешними блоками памяти типа ЗУ на цилиндрических магнитных доменах (ЦМД). Такое ЗУ представляет собсш один или несколько запоминающих модулей, на каждом из которых размещено t 4-8 (До 16) микр осборов, работающих параллельно. Минимальной адресуемой единицей информации для каждой микросборки является страница данных N, разрядность которой равна числу регистров хранения (N 256/1024). Такая страница считывается последовательно. При параллельной работе четырех микросборов информационная емкость адресуемого массива будет равна разрядов.

Возникающие в ЦМД ЗУ ошибки можно условно разбить на два вида (фиг.9): ошибки,возникающие сразу во всех микросборках, например в результате помех, вызывающих сбои в работе усилителей считывания; ошибки, возникаю щие в одной из работающих в параллел микросборок, в ее двух-трех смежных регистрах хранения, например, в результате ложной репликации (деления) одного НМД в соседний регистр.

Если возникает ошибка первого типа, то при чтении в информационном массиве она образует пакет ошибочных разрядов, который обнаруживается и исправляется простым циклическим кодом типа кода Файра. Если имеет место ошибка второго из названных типов PQ искаженные разряды, считываемые из одной микросборки, в информационном массиве окажутся разделёнными между собон правильными разрядами, считанными in других микросборок, т.е. образуются две-три независимые ошиГ-чи. Л ч я пх исправления требуются

0

5

0

5

,

0

35

уже другие, более мощные, коды. Однако применение в одном устройстве нескольких кодов приведет к значительному росту аппаратных и временных затрат.

В предлагаемом устройстве для обнаружения ошибок первого и второго типов с определением их адресов используется один код, например циклический (п,к)-код Файра, где п и k равны соответственно общему числу разрядов кодовой последовательности и входящих в нее информационных разрядов.

Для того, чтобы такой код мог исправлять несколько независимых ошибок, предлагается при записи ин-- формации кодировать ее дважды. При этом первое кодирование предполагает, что информационный массив формируется следующим образом: сначала через кодирующее устройство проходит N разрядов, которые затем.записываются в первую микросборку, затем N разрядов, предназначенных для записи во вторую микросборку, и т.д. до t. Полученный таким образом массив размещается в буфере. При втором кодировании массив складывается из последовательно следующих,t разрядов, каждый из которых затем записывается в первый регистр хранения своей микросборки, затем t разрядов, предназначенных для записи во вторые регистры хранения и т.д. до N.

Такое кодирование приведет к тому, что при появлении ошибки первого типа она будет обнаружена и зафиксирована вторым кодом, для которого она представляет собой пакетную ошибку. Если будет иметь место ошибка второго типа, то она будет обнаружена (и будет определен ее адрес) первым ко- 5 дом, для которого независимые ошибки объединятся в пакет.

По логике работы устройства сначала осуществляется декодирование вторым кодом. Для него ошибка второго типа представляет собой два одноразрядных пакета. Такую ошибку он не может- исправить (указать ее адрес), но способен обнаружить, т.е. установить факт наличия ошибки. Это является сигналом для начала декодирования по первому коду.

Устройство работает следующим образом.

0

5

Перед началом работы производится начальная установка путем обнуле- ния счетчиков 16, 31-35 и 51, триггеров 50 и 61 и соответствующих эле- ментов блока обнаружения ошибок.

Кодирование информации осуществляется в два этапа.

На первом этапе блок данных из k N-t (где N - разрядность страницы данных одной ЦМД-микросборки, t - число ЦМД-микросборок, работающих параллельно) разрядов поступает в буферный блок 3 памяти и одновременно в формирователь 7. При этом в блок 3 памяти данные записываются через коммутатор 2 последовательно по N 256 разрядов в каждую из t А микросхем 39-42, что обеспечивается подачей адресной информации, сигнала выборки ВК и зп/чч от блока 4. Пересчет адресов для каждой микросхемы осуществляется в счетчике 33, а выбор микросхем производится через счетчик 34, ком-. мутатор 36 и дешифратор 38. Разрешающим сигнал-ом на весь этот этап является сигнал 1.1, формируемый в блоке 1 синхронизации. В то же время данные через коммутатор 5 проходят через формирователь 1, котором через k тактов будут сформированы г провероч ных разрядов кода - первичное кодирование. Эти разряды из формирователя 7 через коммутатор 2 записываются в блок 3 памяти в микросхемы 43. Управление записью огущаствляртся блоком 4 через счетчик 35, элементы №И 29 и 30 при сопровождении синхросигнала 1.1.

I

Нд втором этгпе информация поступает на запись из блока 3 памяти ао внешнее ЗУ на ТШД, состоящее из t микросборок, и одновременно в формирователь 7. Но теперь кодируемый мае- сиз из k Hxt разрядов формируется иначе. Скачапа считывается первый разряд из микросхемы 39, затем первый разряд из . ibi АО и далее из микросхем 1 и 42, ::тн разряды, соб- ракные в cnoso , пдраллелтэным кодом записываются в 11-Щ ЯУ (эта часть контроллера НМЛ 3- не показана). Далее считываются последовательно вторые разряды из т- кросхем 3, 40, 41 и 42, При этом адресная информация формируется н счетчике 32, а сигнал выборки со счетчика 31 поступает через коммутатор 36 на дешифратор 38.

5

Q 50

0

5

Управляющим сигналом является сигнал .- 1.2.

В такой последовательности разряды поступают в формирователь 7, где они кодируются тем же кодом. Сформированные через k тактов проверочные разряды (гЈ) из формирователя 7, сопровождаемые синхросигналом 1,2, поступают на запись в ЦМД ЗУ - вторичное кодирование. Поскольку в обоих случаях используется тот же код, то г гя, Процедура кодирования заканчивается передались из блока 3 (микросхемы А3)- через коммутатор 6 проверочных разрядов i-j в Ш1Д ЗУ. При этом сигнал выборки формируется из сигнала 1.2 блока 2 синхронизации.

Декодирование информации также осуществляется в два этапа.

Информационный блок из n k + + г Ј + г 4 разрядов от ПМД ЗУ принимается в устройство. Первые k разрядов записываются в блок 3 памяти (микросхемы 39-42) по сигналу 2.1. При этом считываемые разряды сначала по одному записываются в первую микросхему 39, затем в микросхемы 40, 4 v 42, Следующие разряды снова по одному чагп:сызггггся в микросхемы -9, 40, 41 к 42, 1;чгрмнроьание адресов осугД(гт2лк зтся счетчиком 32 че u-jj кочиута °ог 37, игнлты выборки микросхем - счег - лхок 31 через ком-

МУТЙ ГС Р 36 ЦЕа ЧО/раГОр 38 .

Одновременно k г/- разрядов через комму т л г от; i поступают в блок обнаружения е ьР-р- . в котором осуществляется /;-.- Oitiipон нио информации.

г ort - ви цаетея , г лицом прове. s . отся на за r;i . в блок 3 па- ; 4-s грлвляющим , ; , Адресная инфор -.ацля: , етсч счетчиком 35. В то «о вромч спадом сигнала 2,1 сбрас «гзется Е О блок обнаружения

ОШ ОСЗ1 .

Содеруа - ле блока об} -ш: хегшя ошибок поел приема U - ); у г зрчдов апалИо руется в блоке Ь. Рели оши- Ьок вторичным KV дом ье обнаружено, то на выходе зпе1 iii.i И 5 появляетс сигнал Ошибок не , Јстг обнаружена корре :тируемая оггибьл, тс блок 8 Bbipa6a Tbipae.T спотчет гзуг.щнй сигнал то выходу элсме ;та И ГЛ, юторый вместе с HHibci M u:uj o ацресе огййб

ки и ее картинке с коммутатора 49 по выходу 14 передается в центральный процессор для проведения в дальнейшем коррекции ошибок.

Если вторичным кодом обнаружена некорректируемая ошибка, то открывается элемент И 53, начинается подсче импульсов в счетчике 51 и одновременно открывается элемент И 57, на выходе которого формируется синхросигнал 2.2.3, который сопровождает прием k разрядов в формирователь 7 для декодирования первичным кодом. Эти же импульсы обеспечивают формирова- кие адресной информации и сигналов выборки блоком 4. По этим данным из блока 3 считывается -информационная последовательность в следующем порядке: N разрядов из микросхемы 39, затем из микросхемы 40 и т,д. После приема k разрядов начинается чтение t разрядов из микросхемы 43. Эта передача -сопровождается синхросерией 2.2.3, формируемой на выходе элемен- та И 58, управляемого сигналом с блока 52.

Считываемая в таком порядке информационная последовательность поступает в формирователь 7. Если на вы-, ходе этого блока формируется сигнал Нет ошибок или Некорректируемая ошибка, то анализатор 8 ошибок вырабатывает через элементы И 56 и И-ЙЛИ 60 сигнал Некорректируемая ошибка.

Если на выходе формирователя 7 имеет место сигнал Корректируемая ошибка, то через элемент и 59 передается сигнал Корректируемая ошибка , который вместе с информацией с коммутатора 49 об адресе ошибки и ее картинке поступает в процее сор.

Предлагаемое устройство обладает более широкими функциональными воз- нежностями, поскольку позволяет обнаруживать и определять адрес как независимых, так и пакетных ошибок при незначительном увеличении аппара

ных затрат.

Формула изобретения

Устройство для обнаружения ошибок в бл оках памяти, содержащее блок памяти, формирователь адреса и режима, формирователь проверочных разрядов, адресные вхолы первой н второй групп блока памяти соединены с выходами

0 5

О

5

0

0

5

первой и второй групп формирователя адреса и режима, первый управляющий вход которого соединен с первым управляющим входом формирователя проверочных разрядов и является входом синхронизации устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены блок синхронизации, первый, второй и третий коммутаторы, анализатор ошибок, первый управляющий вход блока синхронизации соединен с первыми управляющими входами анализатора ошибок и формирователя адреса и режима, второй управляющий вход блока синхронизации является входом управления режимом устройства, третий управляющий вход блока синхронизации соединен с вторыми управляющими входами формирователя адреса и режима и анализатора ошибок, первым управляющим входом второго коммутатора и является входом начальной установки устройства, информационный вход первого коммутатора соединен с первым информационным входом второго коммутатора и является информационным входом устройства, первый выход блока синхронизации соединен с третьим управляющим входом формирователя адреса и режима, первым управляющим входом первого коммутатора и вторым управляющим входом второго коммутатора, первый выход которого соединен с вторым управляющим входом формирователя проверочных разрядов, первый выход которого соединен с первым управляющим входом третьего коммутатора и вторым управляющим входом первого коммутатора, третий управляющий вход которого соединен с одноименным входом второго коммутатора, четвертым управляющим входом формирователя адреса и режима и вторым выходом блока синхронизации, третий выход которого соединен с пя:- тым управляющим входом формирователя адреса и режима, четвертым управляющим входом второго коммутатора и вторым управляющим входом третьего коммутатора, третий управляющий вход которого соединен с пятым управляющим входом второго коммутатора и с четвертым выходом блока г.инхрониэа- ции, пятый выход которого соединен с шестым управляющим входом формирователя адреса и режима и четвертым управляющим входом третьего коммута

тора, информационный вход которого соединен с вторым информационным входом второго коммутатора и с выходом блока памяти, информационный вход которого соединен с выходом первого коммутатора, четвертый управляющий вход которого соединен с седьмым управляющим входом формирователя адреса и режима и шестым выходом блока синхронизации, седьмой выход которого соединен с шестым управляющим входом второго коммутатораs второй выход которого соединен с третьим управляющим входом формирователя проверочных разрядов, выходы первой и второй групп которого соединены с входами первой и второй групп анализатора ошибок, первый выход которого соединен с седьмым управляющим входом вто- рого коммутатора и восьмым управляющим входом формирователя адреса и

10

20

890710

режима, девятый управляющий вход которого соединен с пятым управляющим входом первого коммутатора, восьмым выходом блока синхронизации и восьмым управляющим входом второго коммутатора, девятый выход блока синхронизации соединен с третьим управляющим входом анализатора ошибок, второй выход которого соединен с десятым управляющим входом формирователя адреса « режима и девятым управляющим входом второго коммутатора, третий выход которого соединен с четвер- тым-,управляющим входом формирователя проверочных разрядов, выходы первой и второй групп анализатора ошибок являются группами управляющих и ин- форыационных выходов устройства соответственно, выход третьего коммутатора является информационным выходом устройства.

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357967A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Устройство для управления доменной памятью | 1985 |

|

SU1304076A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357968A1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357966A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

Изобретение относится к вычислительной технике, а именно к устройствам обнаружения ошибок в запоминающих устройствах с по ель IORJI атт-- ным доступом. Целью изобре ешм ЛР. Ч ется повышение надежности vci pt mta Згстройство для с ьаруле н блоках сопержш блок сьП хт о1 ч - зации 1 „ первый ке ичут тот 7, бчок Ti- мяти 3, (Ьорчнровотетъ изе .т ма 4, вюрои 5 н трети - Ь ск;-., - ры, Формирователь товео i-i дов 7, анализатор omnci Г-, м i - бпска е чхрэчнзлт И1Г, TIITJ о,-м ч и третьего coMbfj rJT - noL t1 сшибиг I o ptMMoio чоз. гы: УСТРОЙСТВ - Гс) наружеьия Факт- т пакетных i : бок кратности оол4е л 1н 41 - и , 1 1 , ч v L -1 (р 3IJC о О:

.13 4

cpi tTi

Фие.2

HSfl.3

ff/пЬл.

фиг 4

Фиг. 5

tT

U

МЯ

ОтЫЗ

11

М

45

К5л7 -

46

Н 5/f.7 -

47

Hbfl.7 -

фие.В

фиг.7

ОтЪп.7

ОтВл.7

фиЗ-8

--/ ОшиЬочнне

1/n$afH(Hftfon te Заиные

flattern auttfSoff

JB4

ищЕ

.

| Устройство для обнаружения ошибок в блоках памяти | 1985 |

|

SU1249593A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-12-15—Публикация

1989-12-05—Подача