Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем.

Цель изобретения - повышение достоверности контроля микропроцессорной системы в процессе ее функционирования .

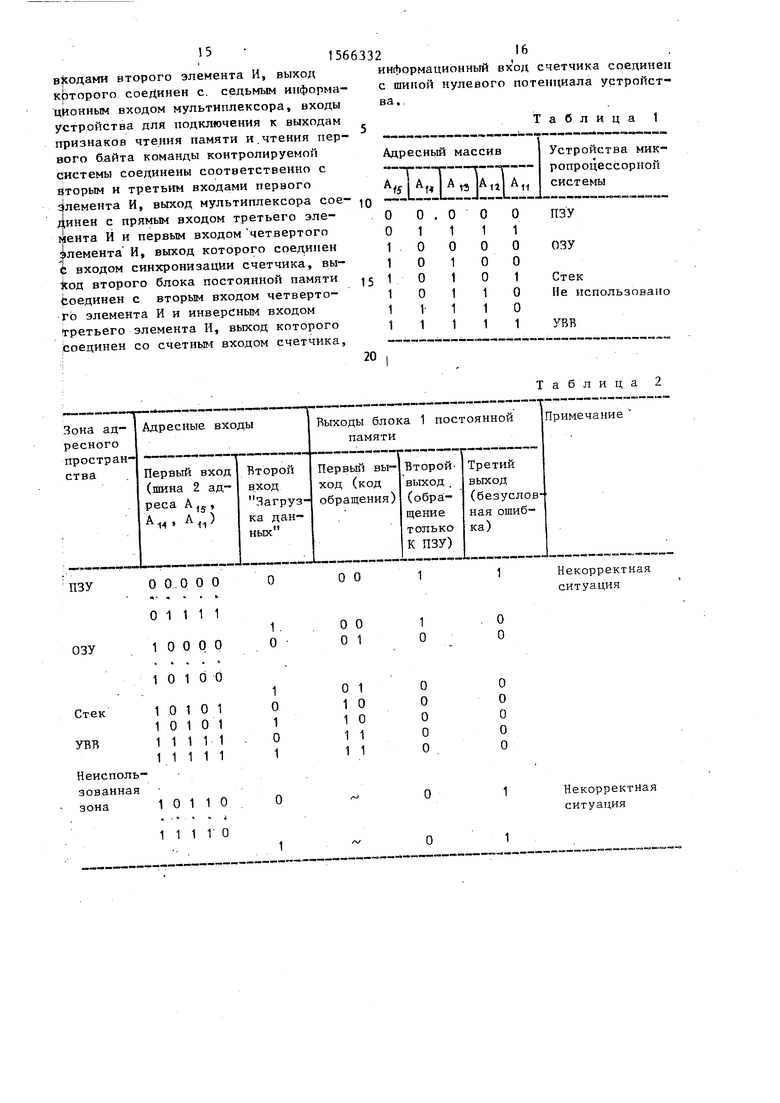

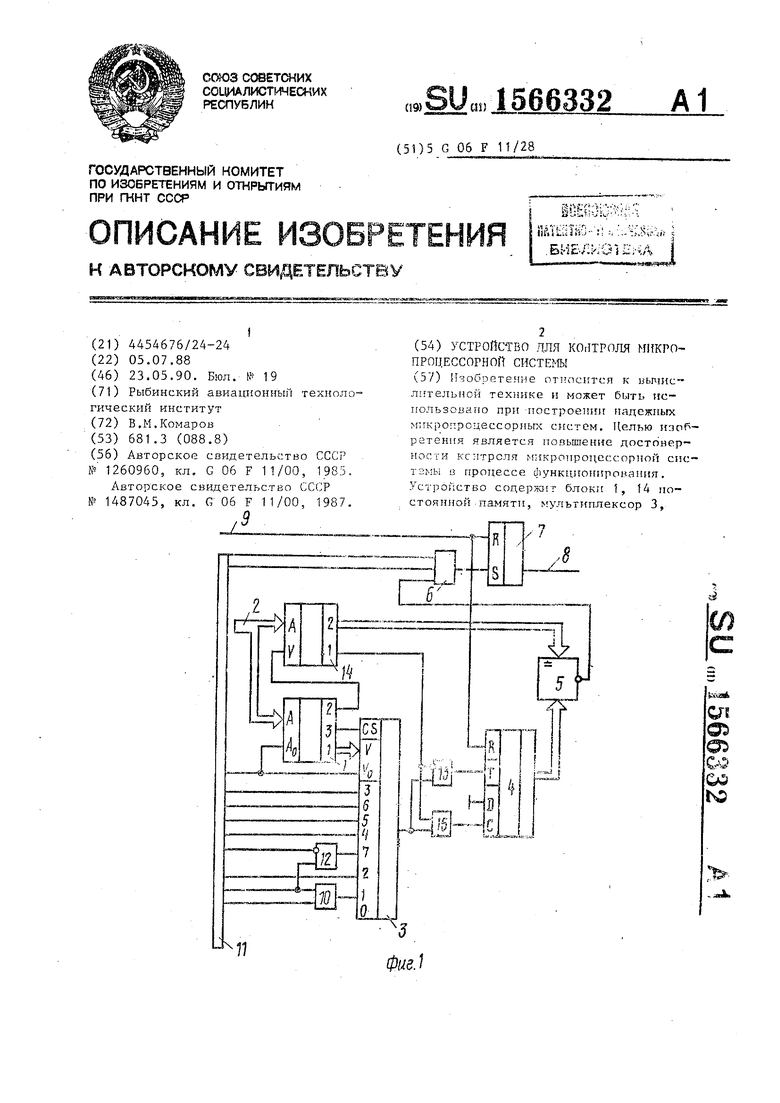

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - временные диаграммы его функционирования.

Устройство для контроля микропроцессорной системы содержит (Лиг. 1) первый блок 1 постоянной памяти, первый адресный вход которого соединен с первой группой линий адресного входа 2 устройства, мультиплексор 3, первый управляющий вход которого соединен с первым выходом первого блока 1 постоянной памяти, последовательно соединенные счетчик 4, схему 5 сравнения, первый элемент И 6 и триггер 7, выход которого является выходом 8 ошибки устройства, а вход сброса соединен с входом сброса счетчика 4 и входом 9 сброса устройства, элемент ИЛИ 10, выход которого соединен с первым информационным входом мультиплексора 3, первый вход - с входом Подтверждение прерывания, а второй вход - с входом Чтение памяти информационного входа 11 устройства, второй информационный вход мультиплексора 3 соединен с входом Запись в память, четвертый информационный вход - с входом Запись в стек, пятый информационный вход - с входом Чтение стека, шестой информационный вход - с входом Вывод, третий информационный вход ;- с входом Ввод в второй управляющий вход - с входом

0

5

0

5

0

5

0

5

Загрузка данных устройства и нн рым адресным входом jiepeoro блока 1 постоянной памяти, второй 12 и третий 13 элементы И, второй блок 14 постоянной памяти, адресный вход которого соединен с вторсй группой адресно о входа 2 устройства, а вход вькч.ркн - с вторым выходом первого блока 1 постоянной памяти, третий выход которого соединен с входом стробироваиия мультиплексора 3, седьмой шторме - ционный вход которого соединен с выходом второго элемента И 12, прямой вход которого соединен с вторым входом первого элемента И 6 и линией Чтение памяти инЛормационного входа 11 устройства, а инверсный вход - с третьим входом первого элемента 46 и линией Чтение памяти ингЪормацнон- кого входа 11 устройства, четвертый элемент И 15, выход которого соединен с входом синхронизации счетчика 4, информационный вход которого подключен к входу логического нуля, а счетный вход - к выходу третьего элемента И 13, прямой вход которого гоеди- - нен с первым входом четвертого элемента И 15 и выходом мультиплексора 3, а инверсный вход - с вторым входом четвертого элемента И 15 и первым выходом второго блока 14 постоянной памяти, второй выход которого соединен с вторым входом схемы 5 сравнения .

Устройство обеспечивает контроль наиболее распространенной микропроцессорной системы с тремя шинами: шиной адреса, шиной данных и шиной управления. Цля обеспечения контроля микропроцессорной системы инбюрмаци- онный вход 11 предлагаемого устройства иплключастсн к управллюпей шине, а адресный иход 2 - к адресной шине контролируемой системы, вход сброса 9 - к входу сброс, микропроцессора, а выход сигнала ошибки 8 может подключаться к входу запроса прерывании микропроцессора или использоваться другим образом.

В общем случае контролируемая микропроцессорная система содержит блок постоянной памяти (ГПУ), блок оперативной памяти (ОЗУ), в которой организуется стек, и устройства нводт-вн- вода (УВВ). На стадии программирования программист должен распределить зону адресного простр шства микронрс- пессора и закрепить м калп м из устройств систем. опре eri Minvn ,дреенч-ю зону. При зтом, как правило, чтстг адресного простр шст на ос т ютсл неиспользованной.

обращения к конкретному устройству микропроцессор Лорнирует на шине a ipeca соогветс твмо шп ьот, обес печиваюиии актив тию п штн о устройств, и генерирует соотштстВУЮШГИ упр1ВЧЯЮШЧ1 I ИГН П. ГЯ Ц о -

цения с пс щги чнГпр и чт о у гр г j н i рас ире л, о пение а чрос г ч; ос м шс- г с п таким образом, чгооп по старшим ра ,- рядам адреса можно Гы го он оггедсЛИТГ УСТРОЙСТВО, К. КОГОрОЧ) lC I4tCrtiляется обращение. Количество чсчотп- зуемых т,ля зтого ri ршлх ра p юн определяется минимальным объемом .д- ресного пространства, закрепляемого

3d К 1ЬИМ-ЛИбО VCIpOIIo-IBOM МИКр МфОцессорнои сие темп. , ншрпмер, для индентификац.ги выгибаемого crpo.i ства системы использовано 5 азря ,ов:

Л

Л.

15 14 ны, и зоны

tj

Л

(

Л

а г росной ши-

1 фесного пространства распре гелены ч стотчетствии с табл. 1 Три таком составе контролируемой мпк- роир эцес.. орнои системы строист О, ь которому ос У| i с ТВ гяется оор ит.сние , может быть укi5ано двухразрялпым кодом. Перегоцнрование входного кода на старггнх разряд ix шины 2 адреса в код, /кавываюцин тип выбираемого уст- поиств,, ос ьлествтяет сч Гтоко( 1 PI)ГТОЯННОИ Пс МЯ-г-И. 1ГЯ ЭТОГО В ИРМ II гг -«о i нс i с т и1 i иг- а тр с ам х; т иг тс i г- ч

у С ГР ПГС ТВ М т) ij 10 С . С i I ) Л 1 i t ГЫ.

ПЧо ь KU TI JO, loi О . П ,

стек i 10, а - от, 1 1 . /

Я качестве М I V lf 1 О с Т.П(Ч Н01 О ГИ1

чала блока 1 rroctvi гг ной памяти

i-

10

15

20

30

J5

40

,

45

50

2

зуется управляющий снгн.п Чагручк.1 данных, указывающий нанравпенне перс дачи нн ормаьнн по пшне данных контролируемой микропроцессорной системы. При равенстве этот i сигнала ПОГИЧРС- кому нулю ннформак н по шипе данных передается из микропроцессора во внешние устройства, а при равенстве логической единице - нч впелних устройств в микропроцессор. Очевидно, что обращение к программному ГПУ в микропроцессорной системе возможно лишь при единичном значении сигнала Загрузка данных. Обращение к ПЗУ при нулевом значении этого сигнала свидететьс т вует о нарушении оЬункпиоНИР 11 ПИЯ М HTpl lllpVC ОН (.ИСТОМЫ.

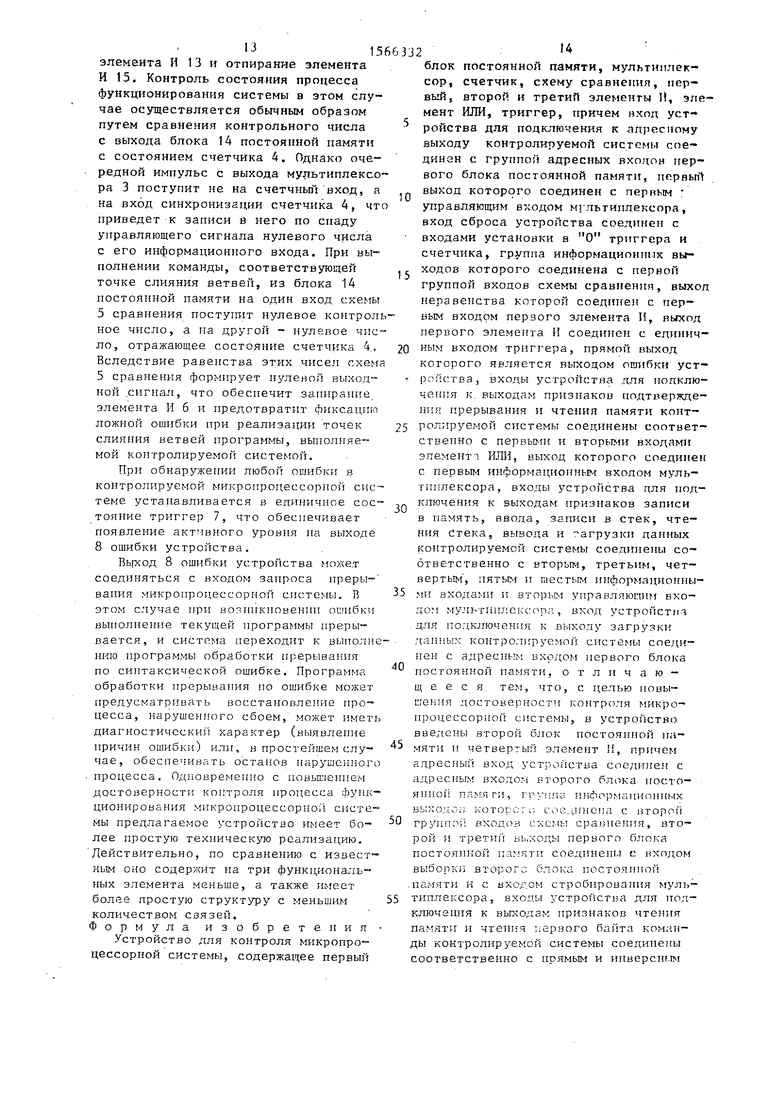

ОЬр nit Hirti к ост i т устройствам никрог роцс сс рпо)1 сиг темы являются корректными при люГом логическом зна- ЧРНПИ сигнала Загрчзт-а ганных. 06- раппнне ч неис по гьзованнои тоне адрес нот о простр иге i ва вс ег га пеьор- pei rrtci и с иилетельстпveT о нарушении Ь1 иг-циониров 1ния контролир с мой сис- т-емг . -т -я вняв тения р JCCMO тройных иск ippei гпыч гигуацн) испотьзуется i ii i i in reri cii.i о ыорп -рч пи ги выход I l i 1 пек тоянноч ичмяти, появление гоннп id и ееi i и единицы на ко- м р м Р i-ннтс-1 на натичие в контроip%iMi i микро ipoiiet системе in. ко pp- t г i in снтупшн такого тигга. Т бнгп) пот б 1 постоянной памяти ipf н таек на в . .

И рм inijHoe 1 ч-1 ионированпе контр Л р СМОГ М ГК ЧО ,СС О1ШОИ С НС1 С МЫ

(в та с я к втолгичню г- т- i г iipoi рам- мч, ) пт i еиной а программной памяти. П i этом в мнкропроцессоршгх система4 (ннримсг. , па микропроцес- с ) i I ГзЬ ТЬЯОА) i - .ля KoiMiiiii вы- по иг i i ся is ге гсш с нескольким iIJI HHHX 1П1КПОВ, Kc -fvbi1 3 KOTCPIiV СОСТОИТ и1 носко ыпч маглингчгх .ктон.

Ка М Me lUlHLIll 1ЦМ Л СВЯЗАЛ ( ilpiTieнием внешним по отноглению к принес- copy vcTfOHCTaaNr (IT3V, 03Vt СТЕКЛУ, УГЛ5) и, слетов ire гьно, npir норма тьчом гц с г . ровзнн системы в к 1жд м мл- . цикле г енерирон ьс я

( 7Н,1 ЧП-ВТЮШНП ИГН1Л, СТР Тс O lT -i ИИ С 1 , 1C ТВ, Гi i

or s р г ,ч |fjt j n с nr ic einie.

В CI LTlf1 LIUhL ll,5aBJ С ГИ i ТН И11

микропроцессорной системы вхоцтт с т ,х- ,д.,( (ИГНД Н, ОС lrL ОСТИ П1 П ИР Otl -

ращсннл к ге устройствам: Чтение п iмяти, Запись в память, Ввод, Вывод, Чтение стека,/ Запись в стек, Подтверждение прерывания. Для обращения к внешним устройствам все эти сигналы стробируются соответствующими строб-сигналами микропроцессора Прием или Выдача. Кроме этих сигналов в состав пины управления входят сигналы Чтение первого байта команды (М1) и Загрузка данных, которые используются в нестро- бируемом виде.

Нарушение соответствия между типом устройства, к которому осуществляется обращение по шине адреса, и активным управляющим сигналом в шине управления является некорректной ситуацией. Очевидно, что непоявление ожидаемого управляющего сигнала при обращении и некоторому устройству системы также является нарушением процесса нормального функционирования контролируемой системы. Для обнаружения некорректных ситуаций в контролируемой системе необходимо прежде всего сопоставить тип устройства, к которому осуществляется обращение в текущий момент времени, с типом управляющего сигнала в момент обращения и зафиксировать Аакт его активирования. Это осуществляется мультиплексором 3 и счетчиком 4 и реализуется следующим образом.

Тип выбранного устройства однозначно определяется кодом с первого выхода блока 1 постоянной памяти. Разряды этого кода поступают на управляющий вход мультиплексора 3. На один из управляющих входов мультиплексора 3 поступает сигнал Загрузка данных с шины управления, указывающий направление передачи информации по шипе данных контролируемой системы. Например, в микропроцессорной системе на базе микропроцессора КР580ИК80А в качестве сигнала Загрузка данных целесообразно использовать управляющий сигнал Запись-вывод. Использование этого сигнала позволяет отличить обращения к одному и тому же устройству контролируемой системы (например, ОЗУ, стеку, VBR) для чтения и записи информации. Таким образом, код, поступающий на управляющий вход мульти- плексора 3, обеспечивает выбор его соответствующего информационного входа, что осуществляет настройку ITOI о

0

5

0

5

0

5

5

0

мультиплексора на прием соответствующего управляющего сигнала, используемого для обращения к внешним устройствам.

Соответствие устройств с учетом принятого кодирования (табл. Л) и управляющих сигналов в контролируемой системе приведено в табл. . ,

Настройка мультиплексора 3 обеспечивает то, что ожидаемый упр ишяюгций сигнал в момент обращения к никотир - му устройству контролируемой системы всегда появляется на выбранном информационном входе мультиплексора 3 и проходит на его выход. В случде нарушения соответствия между типом устройства и управляющим сигналом активный уровень появляется на невыбранном информационном входе мультиплексора 3, и сигнал на его выходе не формируется. В случае, есчи при обращении к устройству контролируемой системы ожидаемый управляющий сигнал не появляется, то выход мумь- типлексора 3 также не активируется. В случае обращения к неиспользуемой зоне адресного пространства гктиви- руется третий выход блока 1 постоянной памяти (табл. 2), запнраклшн мультиплексор 3 по входу стробирова- ния. При этом какой бы управляющий сигнал не появился на информационны входах мультиплексора 3, он не пройдет на его выход. Отсюда следует, что при корректном выполнении текущего машинного цикла обращения к какому-либо устройству контролируемой системы, па выходе мультиплексора 3 всегда Формируется активный сигнал, а при некорректном выпопнепин сигнал на выходе мультиплексора 3 не формируется.

При этом факт появления сигнала на выходе мультиплексора 3 всеглч фиксируется в счетчике 4 HVTGM изменения его состояния. Суммирование входных сигналов в счетчике 4 огупе- ствляется по какому-либо модулю (например, модулю 256), что опрегеляется разрядностью этого счетчика. Т пи некорректных обращениях ь контролируемой системе состояние счетчика 4 не изменяется. Отсюда следует, что состояние счетчика 4 постоянно отражает предысторию процесса Функционирования контролируемой системы по обращению к ее устройствам н течение длительного интервата времени. Оче

видно, что чем ботьше разрядность этого счетчика, т.е. больше модуль суммирования сходных сигналов, тем более iлубокая пре ысторня процесса накапливается в нем.

Для обеспечения контроля в предлагаемом устройстве каждой команде программы, исполняемой коптролиру мо системой, ставится и соответствие некоторое контрп гыюр число. Эго чис вычисляется заранее как с VMMа по том же модулю, что и реализуемый счетчиком 4, количества машинных диклор всех комчнд, пре niiei твуюгшх пишпи команде. КОНТРОЛЕ fib -1 чис id i гче го

рЧбэТП УСТРОЙСТВ РГ ч GIIlnifT В I

14 К С Г ЯШТГ И I if 1 I h I )i

Г 1ОЬ Ч I TI iH pVPT Ч С Т IM IOM II ( С BI 1XO I I r OKI 1 ПО( 1 О ИНГ ) I iM5U

лишь в момент т ч пени Р npoi р.м- мному Ч (t if . О ЧРИ i ом реснии вход б шка 1ч нос i оянноь ч iМЯТИ ПОП ТОчеН К ТСМ 6 М ЫДПИМ D11- РЯ I М 11441 I pPCi f Ир i. M HI СНС С Г14, Ч ГО И npOI p IMM IC)t- ЧТ , it 1 фРС I I Я CMHspM Г НИМ . 1 l jJ I ро II HL а ЧЧС II I I, t 1111 1Ь Т Т В Я С Ч ОЧО 1 ц С I 114 )П 1 Я1 ,11

ь o i орим в при PIMM ГТТ pill tНЫ IH pel к Г 111 I t f Г М Н ( .

В прг I С С t С (1 Ч ) J 1 1 Г 1 К IIIIinp у с i с и i ем i i о) ii I Н (Н Н 11 I С Т И tII If I i 4

п j п и и сп чин II т г т i m

СЧС i ilth 1 + . Ь С 1П f 3 - ILT i III О-

H НИ If i С I ИГО TI 1 Iх I 1 1

IIreiurcH i IB 01 i норм i о и v - in ни о limn i он г о Iиpve и ст .

ПОГЧВНОМ L ie И Т ip 1I1CHIIC IUJPM-Э 1ЫЮ1 ) ()j, 1КЦИОНИ,)Г В 111ИЯ

ci CTCMti. Сигнал, с вил етел ств 1 |цип

0ее точнии DV. ( ее с ч dbyn шгпипов i и

1II 1 I Р С 1itLMI I С ШЦ1 |) т 51 ill 1 t Mil (p ВНЬНИЯ И О U НИL ь i г в ii ни ч п пи i i-

t 1 J(IИ ipoi I l

i .)C С H II LIThCl Ifl -

в i i M iо ч a t /( - i т cp в ни i Lii iii i и Ч.енн первого б ,г-

i i Li 11) и Чт ние ч iM ти с

II 1C Г Ю TbNir II ll 6 .

P pi ti ; aC ; ьредт irdCMoro

S I I IT i 1 1 H( Ь О 1 OpuM Ш1ГС b ill in HIM L.H i I ovtMon систем i

( i . 2) f в ре и г L f

Ul J1I ) 3 В ( iCT H Kf1

lu и if рое число, пест п i HI i i i с с емы 5 cp i P спия. В i p i L с с pc i im и TPI nei о i

12

IU

10

г

5

5

0

5

О

5

на ацресньгй вход 2 поступает адрес устройства микропроцессорной системы, к которому будет осуществляться обра- шенне в текущем малинном цикле. По ст ютим разрядам кола адреса выбирается информационный эход мультиплексора 3, сооттетсгвующнй ожидаемому уирав- ЛЯЮПРМУ сигнал/. При появлении этого ci rmna on :фоходу т через открытый в от мо ент элемент И 13 на счетный счетчика 4, увеличивая по гпаду eiо состояние па единицу. Одновременно по младшим разрядам кода aiprci f блока 14 постоянно памяти мтнтекается какое-тп число, поступи IF i на яругой в од схемы сравнения.

Iс л i i л М i ппп1 цш i пе являет- ч пть юм вмборки черного байта коман-

ц|, п. это число моке- быть произ- ВОЛЕ М. R ITOM случае схема 5 срав- i м.ия обцipvT iuaeT неравенство чисел i i ее входах н формирует на выходе е чп1 Р ч: лоп ческий уровень. Однако Р ,г юмент i не оценивается (, шкчыцня сигнти в Ml п Чтение г яти равн i нучю, и элемент И 6 ч i рмт ) , что i тврапшет бньсацию

ii ив iриг ре 7. Лпачогнч- м г n IM е тi с -ро Л in дноннрует f i ч м i lux пик i i, пе являю м ни i i 1 к т мт впборки пер- i п i i . При чтим ill l f i и i n ч te it пес твпя- cr ii с чьи ьочтроль на от- i к HI IM i i Ml, так как чтение t г ии п Т 3 о змшчно лишь при i t 431 енпн пого сигналя. Тто

tci f п в н « тем, i,i о типь при

II- Ь 1 r-MPi T И 12 открыт и сигнал 4itiiiit п1 (яти проходит на выход

--vTbTHn ексора 3, (J)И cиpyяcь в счетчике 4 ,

Ь Miin i % ; i выборки первого i i ч мип юксор 3 так ке

п i г i 11 тг i с я (i i рнем с жи ( ICMOPO У ir л i с v. i id 4rtB)ie памяти

f i in to i с прерывания). Пд- 1 „бло 1 j iDLTOHHHon памяти

i т г MI с ч ь извчекается и о ы ог делип е контрольное число. 1 i JTO iCHTjcTMioe число совпадает с .т ячнсм с югчика 4, то m ни- х с с i ri сраин HIM d) т 11( гсл п , i )ч MI , ш рчпцьп э гемент

Ч i, i i IM/ гечт идейки с ост t - 7 п1 Р i в i о ruo njpvcMoii сиг i е-

счм i ч 4i f т смспта И 6 но гоннц-тгя Сф ir. и не фнк

111W

сируется, т.е. триггер 7 остается в исходном нулевом состоянии, установлением через вход 9 сброса перед началом работы устройства. По спаду сигнала Чтение памяти (Подтверж- денне прерывания) состояние счетчика 4 увеличивается на единицу так же, как и во всех остальных манииных циклах.

Нарушение нормального функционирования контролируемой микропроцессорной системы может быть вызвано, например, сбоями программного счетчика, счетчика машинных циклов, указателей косвенных адресов микропроцессора, а также отказом лиши н адресной н управляющей шинах системы. Это может приводить к пропуску целых команд или машинных циклов в одной команде, попыткам извлечения команд из зоны ОЗУ, попыткам записи чисел в зону ПЗУ и т.п.

Предлагаемое устройство обеспечивает выявление подобных причин на- рушения процесса функционирования .контролируемой системы. Действительно при пропуске целого количества команд программы в результате сбоя программного счетчика микропроцессора или „ некоторого количества машинных циклов в одной команде в результате сбоя его счетчика машинных циклов состояние счетчика 4 в момент очередной оценки состояния процесса будет не равно контрольному числу, извлекаемому из блока 14 постоянной памяти. При сбоях указателей косвенного адреса, отказах линий шин адреса и управления возникает несоответствие между адресными и управляющими сигналами. В этом случае в момент оценки состояния процесса состояние счетчика 4 также не будет равно контрольному числу, извлекаемому из блока 14. Во всех случаях на выходе схемы сравнения устанавливается единичный уровень, открывающий элемент И 6. В результате этого в момент оценки состояния процесса в контролируемой системе на выходе элемента И 6 появляется сигнал, устанавливающий триггер 7 в единичное состояние, что приводит к активированию выхода ошибки устройства и фиксации нарушения процесса нормального функционирования в контролируе- мой системе.

Описанным образом устройство Функционирует только при воспроизведении

0

5 Q 5

0

5

0

линейных участков программа, -i содержащих точек слияния ветвей. Н этой случае каждой команде из программного ПЗУ может быть поставлено n com нет- ствие только одно контрольное число. Однако реальные программы всем :., имеют гораздо более сложные вОтняциееч и циклические структуры и со: , точки слияния ветвей. R этих ,-пк.х значения контрольных чисел з.п.к ii от того, по какой ветви была вгмчинч1- на программа. В общем случае I.PH риль- ные числа при прохождении различных ветвей не совпадают. Это прт- шпт к тому, что каждой точке сдияш л цогиен должно быть поставлено в сOOTJCTCгвне несколько контрольных чисел. ; i и мтс- ла должны выбираться в конце ресишп- ции соответствующих ветвей программа и размешаться по одному адресу Пч ч, ;i 14 постоянной памяти, что н мм- чо i m,. При невыполнении же этого трпбг..,,пп;-; устройство зафиксировало бы ч,ц, упе- ние процесса функционирования К -нгро- лируемой системы, хотя такового пет.

Для устранения этого противоречия в предлагаемом устройстве т о ч, и - нил ветвей программы отмечав -у, н гчг - выми контрольными числами, . пспеi их реализацией осуществляется предыстории процесса контроля. Ппн этого в блоке 14 постоянном .:амяти для каждой такой точки по a.ipei v, .1; которому в программном ПТУ yp -Mi, первый байт команды, общей -ц; мсс-. объединяемых в данной точке MCI . программы, размещается путевое кпчт- рольное число. При этом по всем адресам, по которым в программном ЧТУ хранятся команды, предшествующе по всем ветвям точке слияния, в разляд блока 14 постоянной памяти, управляющий первым его выходом, зипкчл- вается логическая единица, что не влияет на значения остальных разрядов выходных слов блока 14 по этим адресам. По всем остальным адресам в этом разряде записывается логический нуль, что обеспечивает открытое состояние элемента И 13 при выполнении линейных участков программы.

В результате этого при выполнении контролируемой системой команды, предшествующей по любой ветви точке слияние ветвей, на первом выходе блока 14 постоянней памяти появляется уровень логической единицы (фиг. 2), что обеспечивает запирание

ISfi

элемента И 1J и отпирание элемента И 15. Контроль состояния процесса функционирования системы в этом случае осуществляется обычным образом путем сравнения контрольного числа с выхода блока 14 постоянной памяти с состоянием счетчика 4. Однако очередной импульс с выхода мультиплексора 3 поступит не на счетчный вход, а на вход синхронизации счетчика 4, что приведет к записи в него по спаду управляющего сигнала нулевого числа с его информационного входа. При выполнении команды, соответствуюцей точке с шяния ветвей, из блока 14 постоянной тмяти н i о чш рмн 5 сравнения поступи путевое i онтроп ное число, i на тр и - н., i псе мч - ло, отр 1жтюшсе состояние счегшг- . t ВСЛРГГТВИР равенства тт и iiicen г чон i

5 С р IHIU ПИЯ ор Г) С Т Н , )П I ной с иг н ш, что обе с печит ) imif эк мм г И 6 и прс 1,огьрат1п I IHKC пч ЛОАНОП при peci тп i цин 10ЧС1

СЛИЯНИЯ НОТИС,1 I pOIplMMH, ВИНО НЯ1 - МОИ I ОН I ПО IHp vPMOIl СИС ГСП Ml.

При оонар t и i ч f п1 i f i

КОНТрО 1Пп ч Ч II HIT f i ,и lit ( OP) II ( Hi теме vc гапр в чш 11 i с « с ипчгг1 e с с тоянис т-1 IM i г ) 7, 4i ififc ччпвает появление 1ьг Minor Ч1сыпя HI 8 ус троне тн .

Rl f О Г 8 ОШИБКИ VC прОИ( ГН 1 И UT

сосминягься с i iin. пррргВ И I Ч Н v1 Г I 1 ( III. В

1 Г i М I I i Щ Н III I II (

н in чп HiH rriMi i ni i грамчп incpnII r Г С , И С 14 I t M i ИМ О 1П I 1ШПО I t HI I 1 Ilpf Г p X MM (U) 1 (HI l It i t pt H 1 I И I

nr f пи i i i- ( и ic t KC i i ииРь e. Про р пи

0Op ибо i F и n pi in i i пня ii о i llHi t, MO KI i

1Г P I1 Г IН С f 1 TH I It U III) Ht CC J ,H il L i II С I PL И , М С 1 iIMC I ДИ 1. I 1,1 К С I I I11 lip l nMHli I IlHt. I PI ill I H illill, 1I I 1 ( М С П - Ч It , I( I I11 i 1 Ij I L I I 1

npi, 11, ( с i , it г н fi i i i

(ОС Г lit II С 1 I t lit tll I Hi i он i , ы i i ib I D( I I Iт ML I 1 1 L I -

лее iii c - h ft ни ted о i in iaiuin.

leiiCriHI I i , ЧС С p il HCHIIlO С И u i- i U iiU ,) Г 1 1 И ) 1ч I ll 1

ы j i iLiir i till, i также i l с г

UO 1 J JlpOi Г I) с Тр v f Г j Л С U ill 11.

КОЛИЧС i 1 riO i С н jtJH .

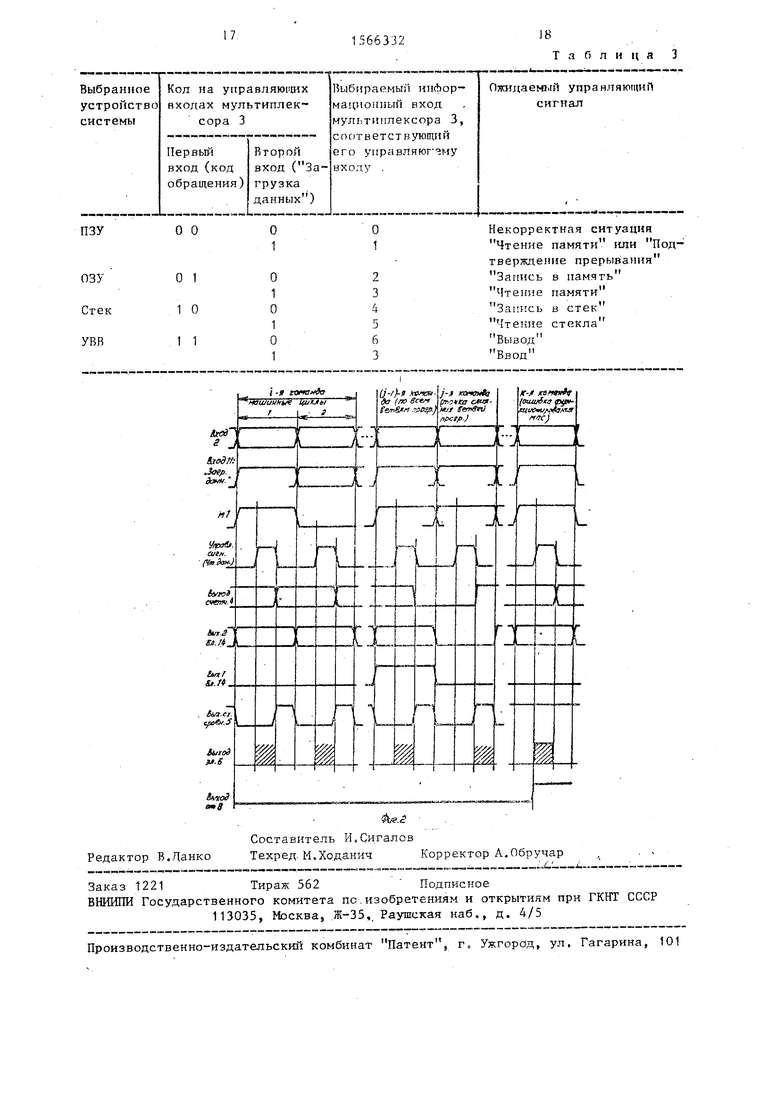

Форм f i и э о r i e т е н и

VCTDOI-TH i гя кочгр п инкропртцесгорнои ГНСТРМН, coieppanpe перрпп

0

5

J

s

2l4

блок постоянной памяти, мультиплексор, счетчик, схему сравнения, первый, второй н третий элементы И, элемент ИЛИ, триггер, причем вход устройства для подключения к адресному выходу контролируемой системы соединен с группой адресных яхоцон первого блока постоянной памяти, первый выход которого соединен с первым управляющим входом MIтьтиплексора, вход сброса устройства соединен с входами установки в О триг гера и счетчика, группа инАормационних выходов которого соединена с первой группой входов схемы сравнения, выход нертвенства которой соединен с первым входом первого члемента И, выход перьо о тчемонта II соединен с единичным входом трип ера, прямой ниход когс того янгяпся выходом ошибки устI Т j ВМ1ГЦ VC. , ПС Tii 1 Ч 1Я 1ГСШКЛЮ41 i i piivpi- VI пртн.-iKon подтвержде- н i i i ерыванич и чтения памяти копт-

i i ip r- on системы соединены соответ- r- ML нно г пег вил1 и BTOPIWH входами - rieiiT HJIii, них од которого соединен с гк ПРЬГМ ин орм чиюнтпгм нхопом МУЧЬ- fiii refcopi, BXCI ь устройства для под- i пюирчиа Y выходам npiMiuiKOB записи в , ввода, Зсмшси в стек, чтения Сте i, вннода и - ii PVTMI данных i М1гролпруем t системы сое ШИРИН со- 01ВЕ7С гненно с нтор IM, третьим, четВ(-РТ1ГМ, 1ЯТЫМ И ТИ.СТЧМ IIIIchojlM 1ЦИ01ГНЫ- М С 1 1ПН Н Hi 1 ) П V 1ф -1Н I Ч НИМ bv О -

1 М Y П ill С, И i I Т р ПС ТН 1

, I 11 -I I ГН ОН Я It О IS II 1 М (I llI ЧН Гр( II p t МОП с, 41 1 L МР С ОС I tlHt i i tin r HI i v 11 и М ii (i б юка п i 10ЯЧНОИ гпмяти, о г 1 н ч а к -

Ц L. С СИ FL.M, ЧГИ, С ЦС1 II Ю 1И НИ- It M I J U I 1 Н t. Ml Hip 1Я 1ГИЬ ,)( - IIH С pli II I ML t ИМ, В ЧСТ НМСТВО

вне it in HI p i нч постоянной на -

III i 7 HCIIT

, рпчгм

L г не п i i i i не ч с

I i l P П ОI l Ь i 110 С 1 О -

1 ,J I lil 1IIMIV

1

L

1 L I1 l, 1

I,U l 1 , НТП -

1 I III 1 Ь t

I Ot ,.H(.HI 1 ( I(1M

1iil ll t Tp iC Ppim 1НП i M 1)ь г i i г гро u i t 1Я ч к нЫчО а1 притн 1коч чтения п пи п лрчт i , fin1- i IM in- All котролч vf on системн с оедшн ни ее ответственно с ппчмьгм и ичнергЧ1гм

входами второго элемента И, выход которого соединен с седьмым информационным входом мультиплексора, входы устройства для подключения к выходам признаков чтения памяти и чтения первого байта команды контролируемой системы соединены соответственно с вторым и третьим входами первого элемента И, выход мультиплексора соединен с прямым входом третьего элемента И и первым входом четвертого элемента И, выход которого соединен с входом синхронизации счетчика, выход второго блока постоянной памяти соединен с вторым входом четвертого элемента И и инверсным входом третьего элемента И, выход которого соединен со счетным входом счетчика,

информационный вход счетчика соединен с шиной нулевого потенциала устройства.

Таблиц

1

Адресный массив

-i-г- - -

AfJ Al« Art An А„

I-l -t-HI-M .. -J MIHlL ДЦ,|

Устройства микропроцессорнойсистемы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для отладки программ | 1988 |

|

SU1624460A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1481775A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем. Целью изобретения является повышение достоверности контроля микропроцессорной системы в процессе функционирования. Устройство содержит блоки 1, 14 постоянной памяти, мультиплексор 3, счетчик 4, схему 5 сравнения, элементы И 6, 12, 13 и 15, триггер 7 и элемент ИЛИ 10. Устройство обеспечивает контроль микропроцессорных систем с тремя шинами. При этом обнаруживаются два типа некорректных ситуаций. Устройство обеспечивает обнаружение некорректных обращений к устройствам контролируемой микропроцессорной системы, а также обнаружение некорректных ситуаций, связанных с пропуском полностью команд программы или машинных циклов в выполняемой команде. При наличии любой некорректной ситуации активизируется выход ошибки устройства, который может соединяться с входом запроса прерывания процессора системы. В этом случае обеспечивается переход к выполнению подпрограммы обработки прерывания по ошибке с целью принятия необходимых действий. 2 ил., 3 табл.

Тона адресногопространства

00000 01111 10000 10100

10101 10101

11111 11111

1 О

1 о 1 о

1

Неиспользованнаязона1

1

Таблица

о о

Некорректная ситуация

о о

О 1

1 о

о о

о

о о о о

о о о

о о

Некорректная ситуация

Т а б л и ц а 3

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-23—Публикация

1988-07-05—Подача