Изобретение относится к вычислительной технике и может быть использовано для отладки программ микроЭВМ и микропроцессорных устройств в реальном масштабе времени.

Цель изобретения - повышение достоверности контроля хода программы.

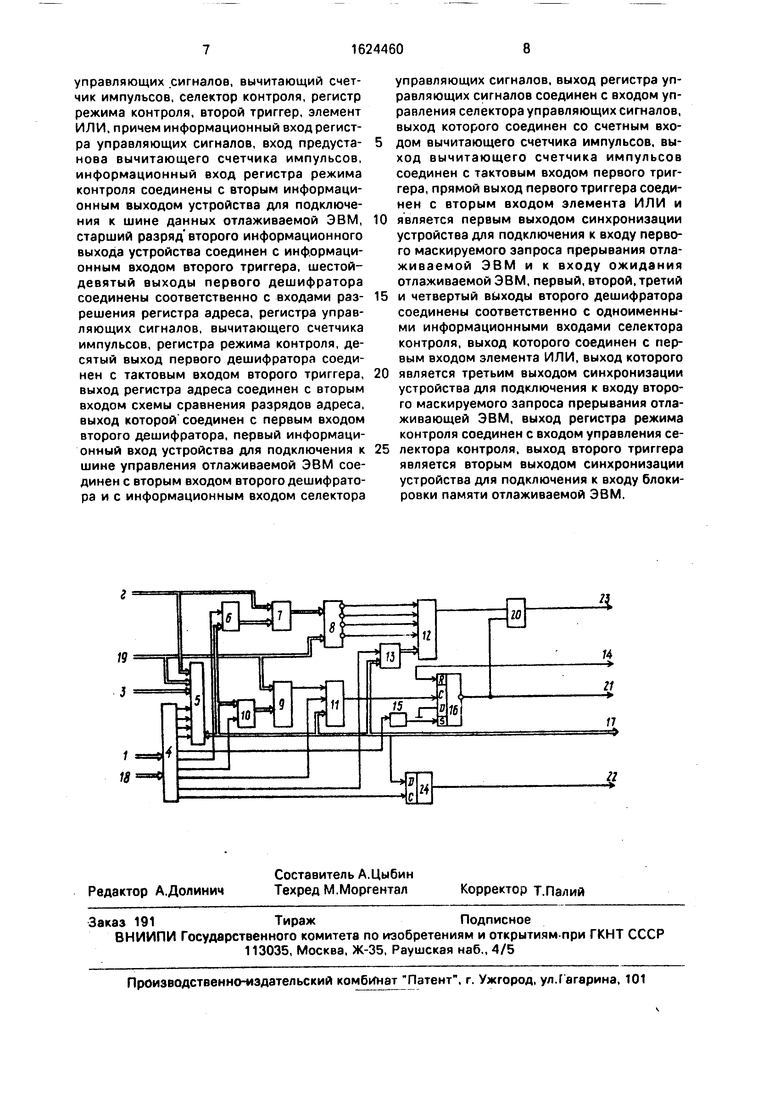

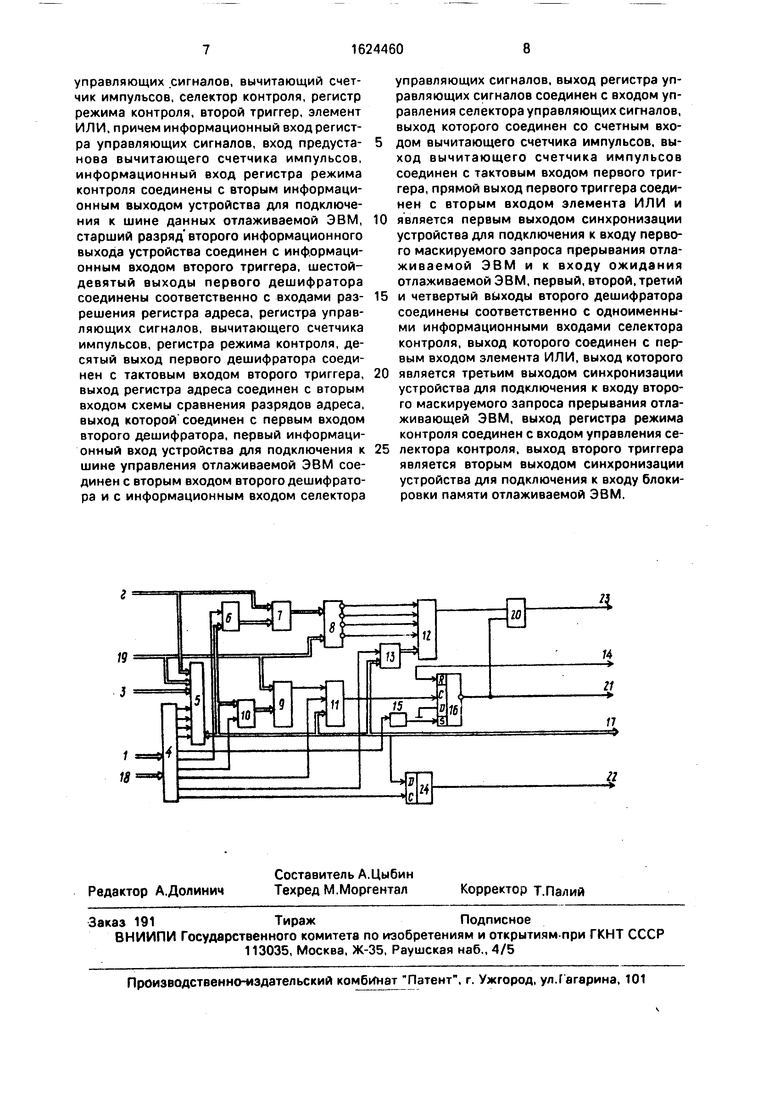

На чертеже представлена структурная схема устройства для отладки программ.

Устройство содержит первый и второй информационный входы 1 и 2 устройства соответственно, первый информационный выход 3 устройства, первый дешифратор 4, мультиплексор 5 магистралей, регистр 6 адреса, схему 7 сравнения разрядов адреса, второй дешифратор 8, селектор 9 управляющих сигналов, регистр 10 управляющих сигналов, вычитающий счетчик 11 импульсов, селектор 12 контроля, регистр 13 режима контроля, вход 14 начальной установки устройства, формирователь 15 короткого импульса, первый триггер 16, второй информационный выход 17, адресный вход 18 уст- ройства, третий информационный вход 19 устройства, элемент ИЛИ 20, первый выход 21 синхронизации устройства, второй и третий выходы 22 и 23 синхронизации устройства соответственно, второй триггер 24.

При включении питания одиночный импульс с входа начальной установки устройства 14 поступает на нулевой вход (R-входа) первого триггера 16 и устанавливает его нулевое состояние. Первый триггер 16 формирует сигнал, поступающий через первый выход 21 синхронизации устройства в отлаживаемую микропроцессорную систему в виде сигнала WAIT (ожидать) и в отлаживающую миниЭВМ в виде нулевого первого маскируемого сигнала на прерывание INT1, а также на второй вход элемента ИЛИ 20 поступает через третий выход 23 синхронизации устройства в отлаживаюсо

с

k

ю

Ј

СХ

о

ц jo миниЭБМ а виде второго маскируемо го сигнала на прерывание

Через первый ш формацио.нный вход 1 устройства на первый вход первого дешифратора 4 поступают сигналы шснсЛ упртвле- ния отлаживающей миниЭВМ На второй вход первого дешифратора 4 через здоес- ный вход 18 устройства поступают младшие разряды адресной шины отлаживающей мм- ниЭУМ.

При поступлении ta первый дешифра- 4 соео- упчост и сигналов разрядов адре- ст сигналов управления Запись в устройство пвода-вь.впда, Чтение уст- ргйстр рвода-вывода в зависимости от кода, поступившего на вход первого дешифратора 4, возб, «дается один из выходов первого дешифратора 4.

Поступающий код на вы оде первого дешифратора 4 может быть десяти типов В соответствии с описанном ниже работой ус- тройс вз дня отладки программы обозначим кажд11й из одоз символами а, Ь, с, d, e, f, g, h j При поступлении нз вход первого / шифратора 4 кодов а, Ь, с возбуждается соответственно первый второй, третий выходы пеового дешифратора 4, которые сое- дичони соответственно с первым вторым «ретьии вводами упровтения мультиплексора 5 магистралей Hpii наличии кодер а, Ь с. н пход| первого дешифратора 4 муг.ь- типлрксор 5 магистралей обеспечивает к n.iMVT-пдию соответственно второго ин- рмациот ого пхода 2 /сфойстна, третье i L Ферма онно о ву-.дч 19 устройства, первого ин юрмационного выхода 3 устрой- стгп на втооой информационный выход 17 уст( ойстьг) Коде1 возбуждает соответственно метпергыи выход первого дешифратора л, , соединен соответственно с чет вер.ым вхэдом управления мультиплексора г магистралей При аличии кода d на входах первого дешифратора л мультиплексор 5 магистралей сЬеспечивает коммутацию информационного выхода 17 устройства со- огветсгвенно ia перпый информационный аыход 3 устройства.

Код е возбуждает пятый выход первого рятора 4, который соединен с входом формирователя 1Ь короткого импульса. Код е, запуская формирователь 15 короткого импульса, переводит первый триггер 16 по ус- тачсаочному входу (S-вход) в гдиничное состояние, снимая тем самым сигнал WA Т с ервого выхода 21 синхронизации устройства и осуществляя автоматический запуск отлаживаемой микропроцессорной С1лстемы после останова

Коды f, q h I возбуждают соответственно и-естой седы/ои, восьмой девятый вычоды первою дешифратора 4, которые подключены , входам разрешения записи соответственно регистра 6 адреса, регистра 10 управляющих сигналов, вычитающего счетчика 11 импульсов, регистра 13 режима контроля. При наличии кодов f, g, h, I на входе первого дешифратора 4 последний сигналами на шестом, седьмом, восьмом, девятом своих выходах разрешает запись информа0 ции из второго информационного выхода 17 устройства соответственно а регистр 6 адреса, регистр 10 управляющих сигналов, вычитающий счетчик 11 импульсов, регистр 13 режима контроля.

5 Кед J возбуждает десятый выход первого дешифратора 4, который подключен к так- товому входу второго триггера 24. При наличии кода j на входе первого дешифратора 4 последний сигналом на десятом сво

0 ем выходе, поступающим на тактовый вход (С-вход) второго триггера 24, разрешает запись информации из линии старшего разряда второго информационного выхода 17 устройства во второй триггер 24 через его

5 информационный вход (D-вход).

Регистр 6 адреса предназначен для сохранения адреса очередной контрольной точки отлаживаемой программы

Схема 7 сравнения разрядов адреса выO рабатывает нулевые сигналы при совпадении старших и младших разрядов адреса, соответственно поступающих из регистра б адреса (разряды адреса очередной контрольной точки отлаживаемой программы) и

5 из второго информационного входа 2 устройства (разряды текущего адреса обращения)

При поступлении на второй дешифратор 8 совокупности сигналов, разрядов

П управления из отлаживаемой микропроцессорной системы через третий информационный вход 19 устройства и сигналов со схемы 7 сравнения разрядов адреса в зависимости от кода, поступающего на входы

5 второго дешифратора 8, возбуждается один

из четырех выходов второго дешифратора 8.

Поступающий код может быть четырех

типов и соответствует четырем ситуациям в

отлаживаемой микропроцессорной систе0 ме: чтение памяти с определенным адресом, запись в память с определенным адресом, чтение устройства ввода-вывода с определенным адресом, запись в устройство ввода-вывода с определенным адресом, и

5 соответственно этому возбуждает сигнал на первом, втором, третьем и четвертом выхо- д х второго дешифратора 8.

Под воздействием комбинации сигналов, хранящейся в регистре 10 управляющих сигналов, селектор 9 управляющих

сигналов пропускает только один определенный разряд управления с третьего информационного входа 19 устройства на счетный вход вычитающего счетчика 11 чм- пульсов, который по входу предустзноаа устанавливается нз подсчет определенного числа импульсов в пределах от 1 до 2П, где п - число двоичных разрядов входа пред- установа вычитающего счетчика 1 импульсов. При поступлении на вычитающий счетчик 11 импульсов заданного к.опичеслва импульсов разряда упраь-.ния. пропускаемого селектором 9 управляющих сигналов с третьего информационного входа 19 устройства, вычитающий счетчик 11 импульсов возбуждает сигнал, поступающий на синхронизирующий вход (С-вход) первого триггера 16. На информационный вход (D-вход) первого триггера 16 подается лог, О. При поступлении сигнала на синхронизирующий вход (С-БХОД) первого трчгге-рз 16 последний устанавливается в путевое состояние, вырабатывая сигнал VVAI f для отлаживаемой микропроцессорной системы и первый нулевой маскируемый сигнал INT1 для отлаживающей миниЗВМ на первом выходе 21 синхронизации устройст- па.

Под воздействием комбинации сигналов, хранящейся ь регистре 13 режима кон- трс.-я, селектор 12 контроля припускает нулевой сигнал с одного из ч vjpex at .ходов второго дешифратора 8 на первый вход элемента ИЛИ 20. С выхода парного триггера 1о поступает нулевой сигнал из второй вход элемента ИЛИ 20. Элемент ИЛИ 20 только при наличии нулевых сигналов на с.юих входах выраба нулевой втооои москиру- емый сигнал прерывания NT2 для отлаживающей миниЭВМ на третьем выходе 23 синхронизации устройства.

Второй триггер 24 вырабатывает сигнал Блокировка памяти на втором выходе 22 синхронизации /стройства для оглаживающей микропроцессорной системы,блокирующий обращение к памяти налаживаемой микропроцессорной системы.

Для отладки поогрзмм к устройству подсоединяется миниЗВМ v гллаживззмая микропроцессорная система работает следующим образом. Адресная шина мини- ЭВМ подсоединяется к адресному аходу 18 устройства, шина управления к первому информационному входу 1 устройства, шина данных - ко второму информационному выходу 17 устройства, линия сигнала на первый м а с к и р у е м ь и запрос прерывания 1Г1Т1 - к первому н:,коду 21 синхронизации устройства, линия сигнала на второй маскируемый запрос прерывания )1МТ2 - к

третьему выходу 23 син г:ониззц;Ч1 ус тройства, линия сигнала начальной уст,;-нгзки - к входу 14 начальной у ; анор ;г уст юйс гва. Адресная шина отл-.хnF.seмой микро- 5 процессорной системы ПСА ООДИНЯЛТСЯ ко второму информзцио .чому входу 2 устройства, шина управления подсоединяется к третьему информационному входу 19 устройства, шина данных - к первому информа0 ционному выходу 3 уст pof C 1 ва, линия сигнала WAIT - к пепьому выходу 21 синхронизации устройств:) линия сигнала Блокировка памя и - ко второму выходу 22 синхронизации устройства.

5Форму л а изобретен и я

Устройство для отладки программ, содержащее схему ог;|ч .,:.-.р-. адрз- са, ексо ;-iar-1 ; -,:-j кш. первый дешифратор, формирогатол1- :. opoi кого им0 пульса, первый тои 1-чр, n w/ .M ад|/есный вход устройства длч :: ч1 .:; --он и г :. ..чине адресз отллж г :(н:;г: -, -L Ivl соедш-ои с пер- информ.-ли с I-IM первого дешифратора, зторо И1 форм :;|10нчый вход

5 которого соедин .1 z первым информационным входом устройства для подключения к шине упражнения отлэжпрэющей ЭВМ. второй инфсрмацио:1Н1,Й вход устройстз дгя подключения к шине адреса отлажипа0 ю;.цей ЭВМ сооди - й1; г.. г.ппь: чифор- м а ц и о i. с :.;- , в о; ом п L. г ; м i г, е ,- с о р а магистралей и схол. : -.сия сравнения разрядов дрс-са. т .У/т ч м-1:-. ; ср -..ци- онный вход устройства д/г-i ..чпни.с1 к

5 шине управления отллжш - ош й - соединен С ВТОрЬ.М . 01)..:М ПХО/;ОМ мульти лекссоа м-гисгр,. Г|(. ин- форг аиионный вылод yCTpoHCiO для подключения К IJJi lH , .iaiiHL X от;гс, . СЛОМОЙ

40

оодинен с третьим информационным

входом мультиплокс.лра маг;- :т эл(. м, пер- вь:й, второй, т ре it м и чет мл pi ып (;ычоды первого дешифратора соединены соо;вет- ственчо с о/ чпимгчными . iipai.-.q Gi. inMn

5 входами мультиплексор t- .з1. ист раггй, вы- хсд которого соединен с спорые информационным выходом устройства для подключения к шчно дг.чнь.х отлаживаемой ЭВМ, пчтый пглол. .ого .г-г ифратора

0 соединен через фо| мирова-ель короткого импуль-; с едини- -ЮД Л пог-т-о триггера, ijy/ieBOH РЧО,: ле: пого :r irrcp соединен с входом начально,: установки устройства, информационный вход первого

5 триггера соединен с шиной нулог-о-о потенциала устройства, с т л и ч а ю ш е е с я тем, что, с целью повышения досг{. : -:;|-ос Ч 1 контроля хода лпогпамм1,|. vc.roi ir ,o F-.ГЧ, ,е- ны регистр адреса.второй ,.,к.ратор, селектор управляющих civ . гогпстр

управляющих сигналов, вычитающий счетчик импульсов, селектор контроля, регистр режима контроля, второй триггер, элемент ИЛИ, причем информационный вход регистра управляющих сигналов, вход предуста- нова вычитающего счетчика импульсов, информационный вход регистра режима контроля соединены с вторым информационным выходом устройства для подключения к шине данных отлаживаемой ЭВМ, старший разряд второго информационного выхода устройства соединен с информационным входом второго триггера, шестой- девятый выходы первого дешифратора соединены соответственно с входами разрешения регистра адреса, регистра управляющих сигналов, вычитающего счетчика импульсов, регистра режима контроля, десятый выход первого дешифратора соединен с тактовым входом второго триггера, выход регистра адреса соединен с вторым входом схемы сравнения разрядов адреса, выход которой соединен с первым входом второго дешифратора, первый информационный вход устройства для подключения к шине управления отлаживаемой ЭВМ соединен с вторым входом второго дешифратора и с информационным входом селектора

управляющих сигналов, выход регистра управляющих сигналов соединен с входом управления селектора управляющих сигналов, выход которого соединен со счетным входом вычитающего счетчика импульсов, выход вычитающего счетчика импульсов соединен с тактовым входом первого триггера, прямой выход первого триггера соединен с вторым входом элемента ИЛИ и

является первым выходом синхронизации устройства для подключения к входу первого маскируемого запроса прерывания отлаживаемой ЭВМ и к входу ожидания отлаживаемой ЭВМ, первый, второй, третий

и четвертый выходы второго дешифратора соединены соответственно с одноименными информационными входами селектора контроля, выход которого соединен с первым входом элемента ИЛИ, выход которого

является третьим выходом синхронизации устройства для подключения к входу второго маскируемого запроса прерывания отлаживающей ЭВМ, выход регистра режима контроля соединен с входом управления селектора контроля, выход второго триггера является вторым выходом синхронизации устройства для подключения к входу блокировки памяти отлаживаемой ЭВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки микроЭВМ | 1989 |

|

SU1677708A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

Изобретение относится к вычислительной технике и может быть использовано для отладки программ микроЭВМ и микропроцессорных устройств. Цель изобретения - повышение достоверности контроля хода программы. Устройство для отладки программ содержит схему сравнения разрядов адреса, мультиплексор магистралей, первый дешифратор, формирователь короткого импульса, первый триггер, регистр адреса, второй дешифратор, селектор управляющих сигналов, регистр управляющих сигналов, вычитающий счетчик импульсов, селектор контроля, регистр режима контроля, второй триггер, элемент ИЛИ. Устройство автоматизирует процесс отладки программ за счет того, что позволяет контролировать очередной адрес операндов в текущей команде, задавать несколько адресов и условий останова. 1 ил.

Ј

| Устройство для отладки программ | 1982 |

|

SU1100627A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1984 |

|

SU1223236A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-30—Публикация

1988-05-25—Подача