Изобретение относится к импульсной .технике и может быть использовано в системах автоматики и измерительной техники.

Цель изобретения - расширение функциональных возможностей за счет обеспечения формирования выходной импульсной последовательности с частотой, пропорциональной сумме или разности частот двух входных импульсных последовательностей .

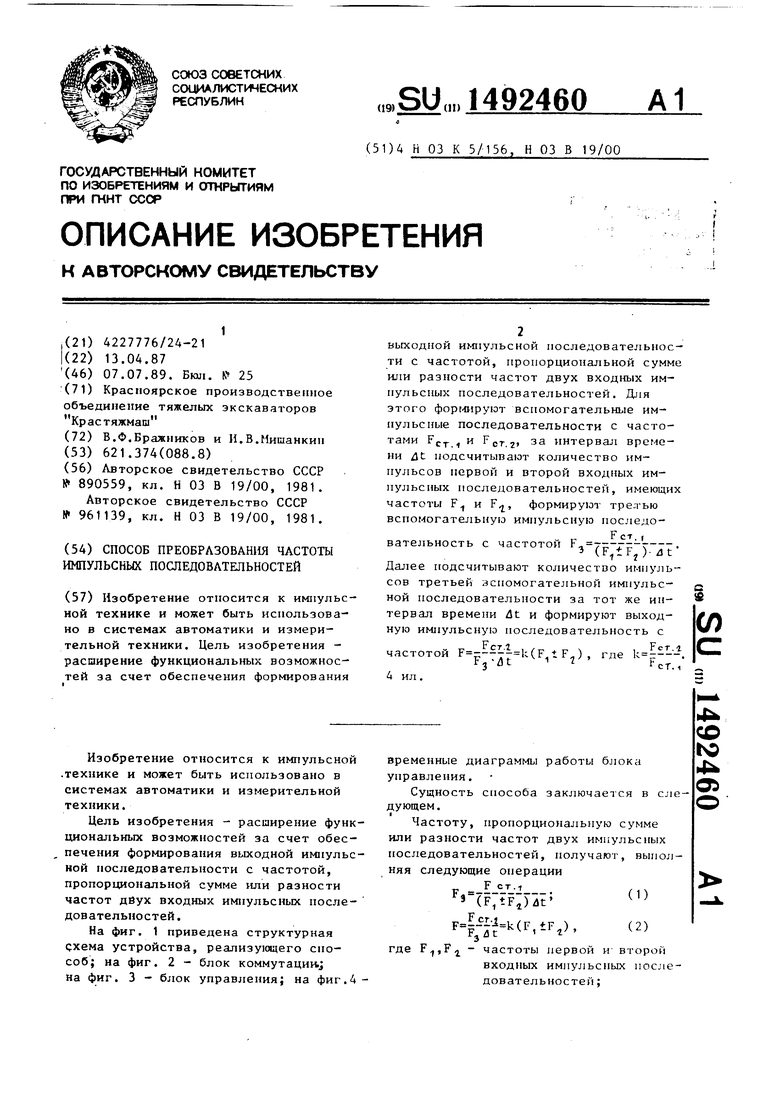

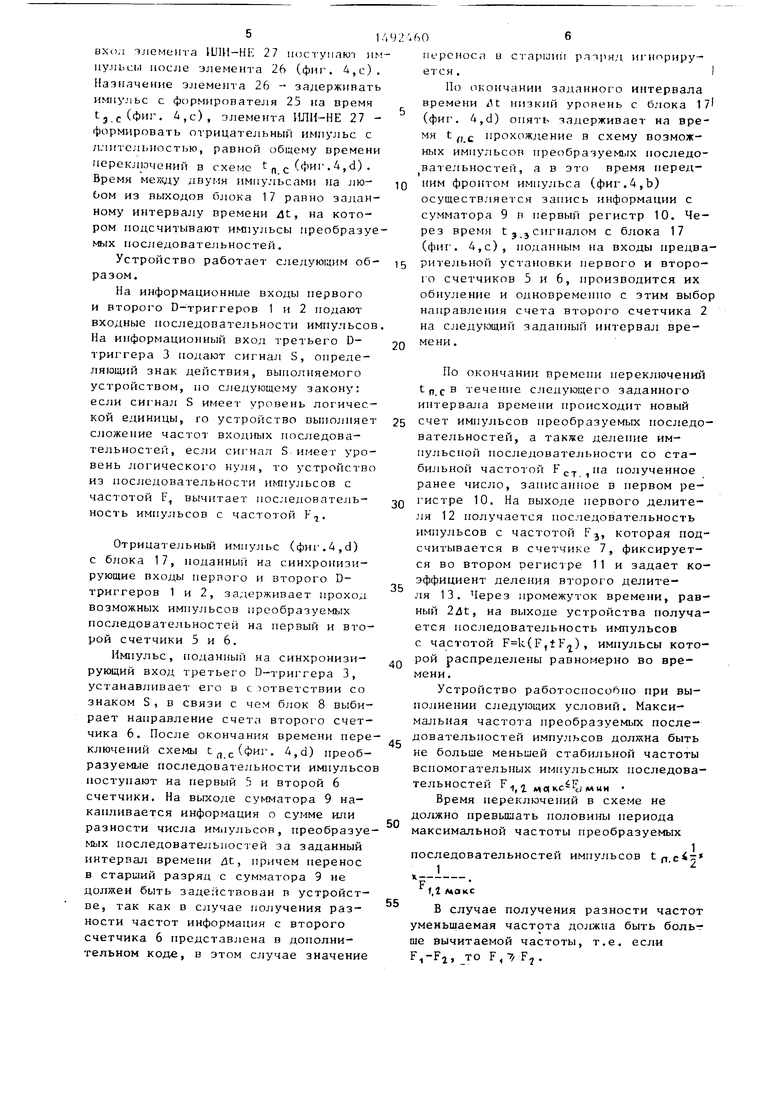

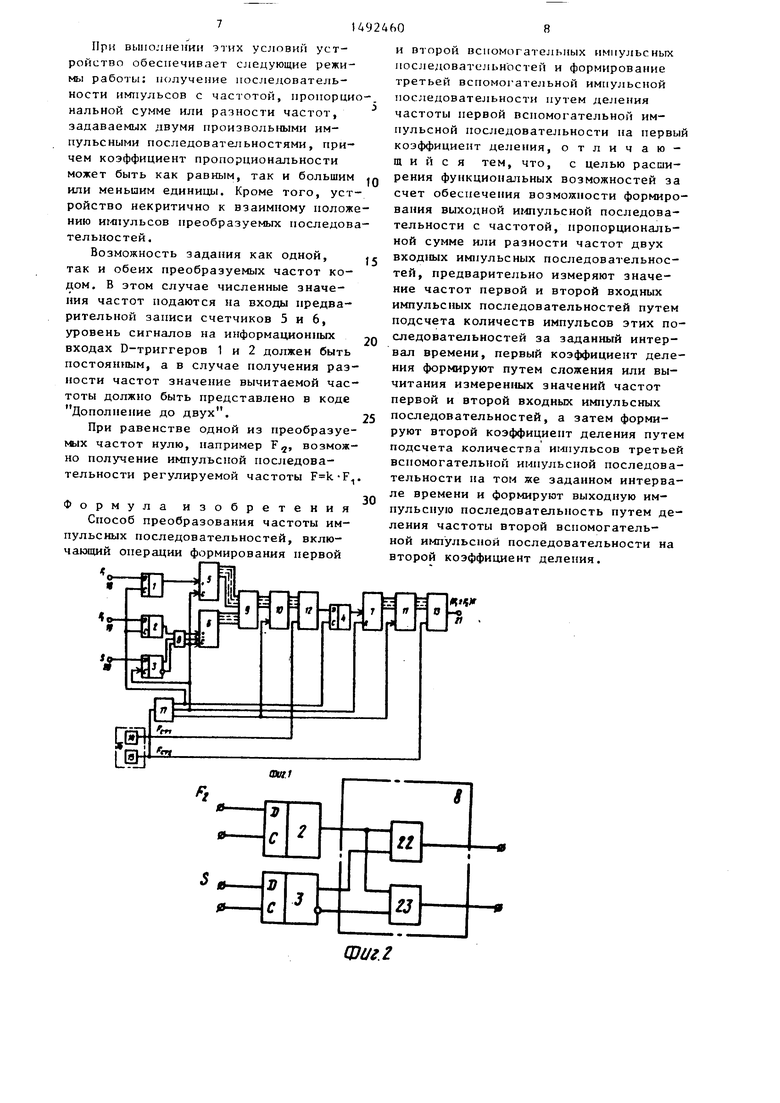

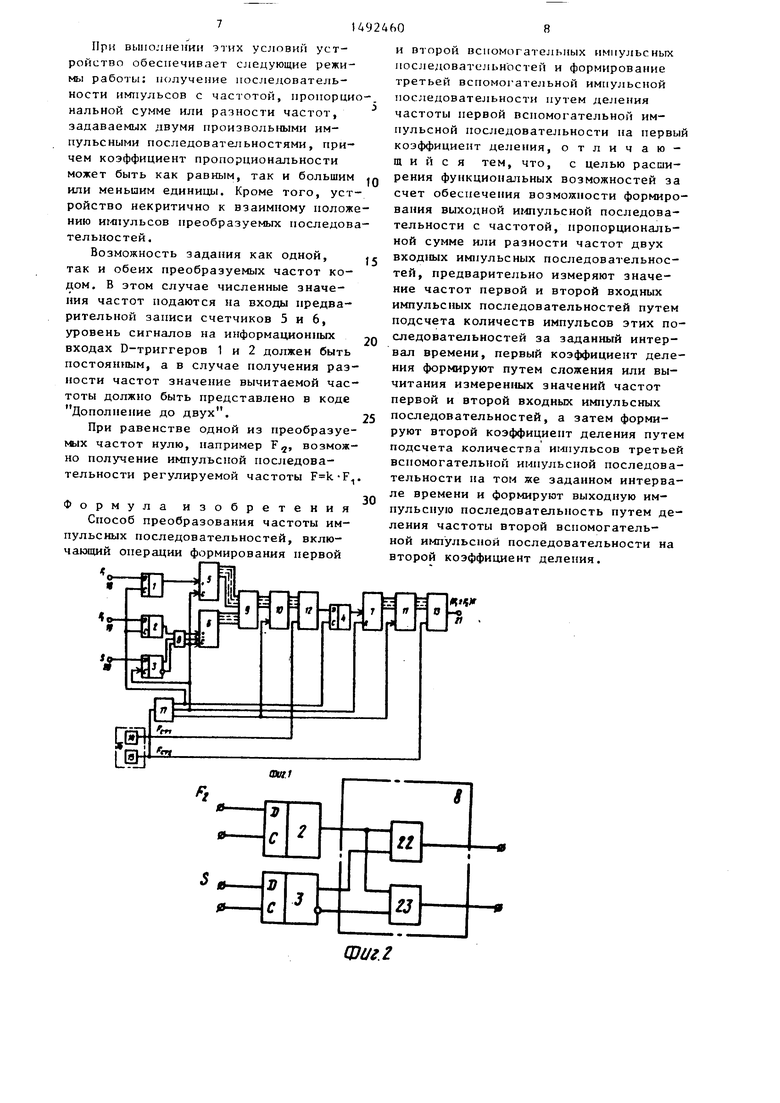

На фиг. 1 приведена структурная схема устройства, реализующего способ; на фиг. 2 - блок коммутации; на фиг. 3 - блок управления; на фиг.4

временные диаграммы работы блока управления.

Сущность способа заключается в следующем.

Частоту, пропорциональную сумме или разности частот двух импульсных последовательностей, получают, выполняя следующие операции F ст..

(F,tF)ut

F ----i k(F -«-F ) Fj/jt г

(1) (2)

1С

4

О)

где F,F - частоты первой и второй

входных импульсных последовательностей ;

F. 4t T.i .

частота третьей вспомогательной импульсной последовательности, полученной в результате операции (1) ;

заданный интервал времени, на котором подсчитывают числа импульсов входных последовательное-jg тей;

стабильные частоты первой и второй вспомогательных импульсных последовательностей;

. Fcr. 1 k--

r t 1

коэффициент пропорциональности между частотой выходной импульсной последовательности и частотой, равной сумме или разности частот входных импульсных последовательностей;

F - частота выходной импульс - ной последовательности, полученной в результате операции (2).

При Fji 0 частота выходной импульсой последовательности

,.

.е. этот способ позволяет получать мпульсную последовательность регуируемой частоты F при изменении F,. При частота выходной импульсой последовательности равна сумме ли разности частот входных импульсых последовательностей, т.е. ,tF.

При этбм не накладывается никаких ограничений на соотношение частот F и F, т.е. обеспечивается расширение частотного диапазона входных импульсных последовательностей.

Устройство содержит с первого по четвертый D-триггеры 1-4, причем третий D-триггер 3 с динамическим управлением, с первого по третий счетчики 5-7 и myльcoв, допускающие предварительную установку заданного числа, причем второй счетчик 6 ревер сивный, блок 8 коммутации, сумматор 9, первый и второй регистры 10 и 11, первый и второй делители 12 и 13 часто- . ты, первый и второй генераторы 14 и 15 импульсов, объединенные в блок 16 генераторов, блок 17 управления, тервую, вторую и третью входные шины 18-20,соединенные с D-входами D-5

jg

15

, .

20

25

триггеров 1-3 соответственно,и выходную шину 21, соединенную с выходом делителя 13. Прямой выход первого D-триггера 1 соединен со счетным входом первого счетчика 5, прямой выход второго D-триггера 2 и прямой и инверсный выходы третьего D-триггера 3 соединены с входами блока 8, выходы которого подключены к прямому и обратному счетным входам второго счетчика 6, выходы первого и второго счетчиков 5 и 6 соединены с входами сумматора 9, выходы первого и второго счетчиков 5 и 6 соединены с входами сумматора 9, выходы которого соединены с входами первого регистра 10, выходы кЪторого подключены к входам предварительной записи первого делителя 12 частоты, выход которого подключен к информационному входу четвертого D-триггера 4, прямой выход которого соединен с счетным входом третьего счетчика 7, выходы которого подключены поразрядно к информационным входам второго регистра 11, выходы которого соединены с входами предварительной записи второго делителя 13 частоты, счетные входы.первого и второго делителей 12 и 13 частоты подключены к выходам первого и второго генераторов 14 и 15,выход второго генератора 15 соединен с входом блока 17. Первый выход блока 17 подключен к управляющим входам регистров 10 и 11, второй - к входу сброса третьего счетчика 7, входам предварительной установки первого и второго счетчиков 5 и 6 и синхронизирующему входу третьего D-триггера 3, третий выход блока 17 подключен к синхронизирующим входам первого 1, второго 2 и четвертого 4 D-триггеров.

Блок 8 содержит первый и второй элементы И 22 и 23, которые в зависимости от уровня сигнала на информационном входе третьего D-триггера 3, пропускают импульсы последовательности с частотой F либо на прямой, либо на обратный счетные входы второго 50 счетчика 6.

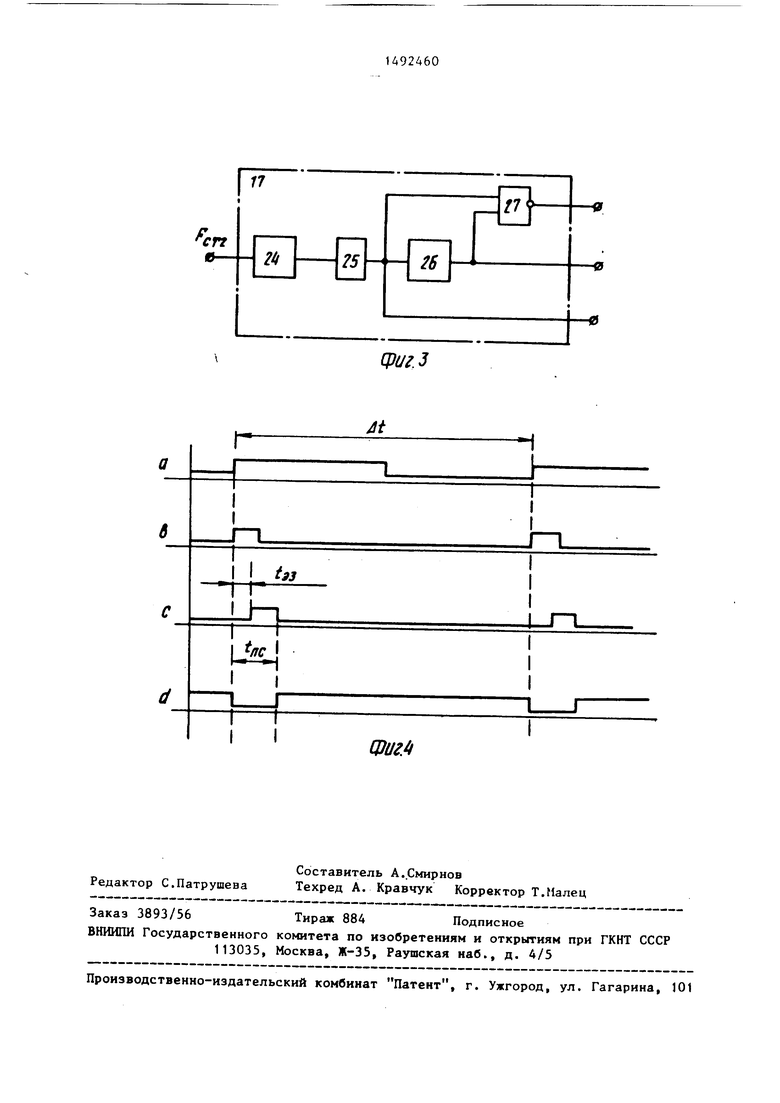

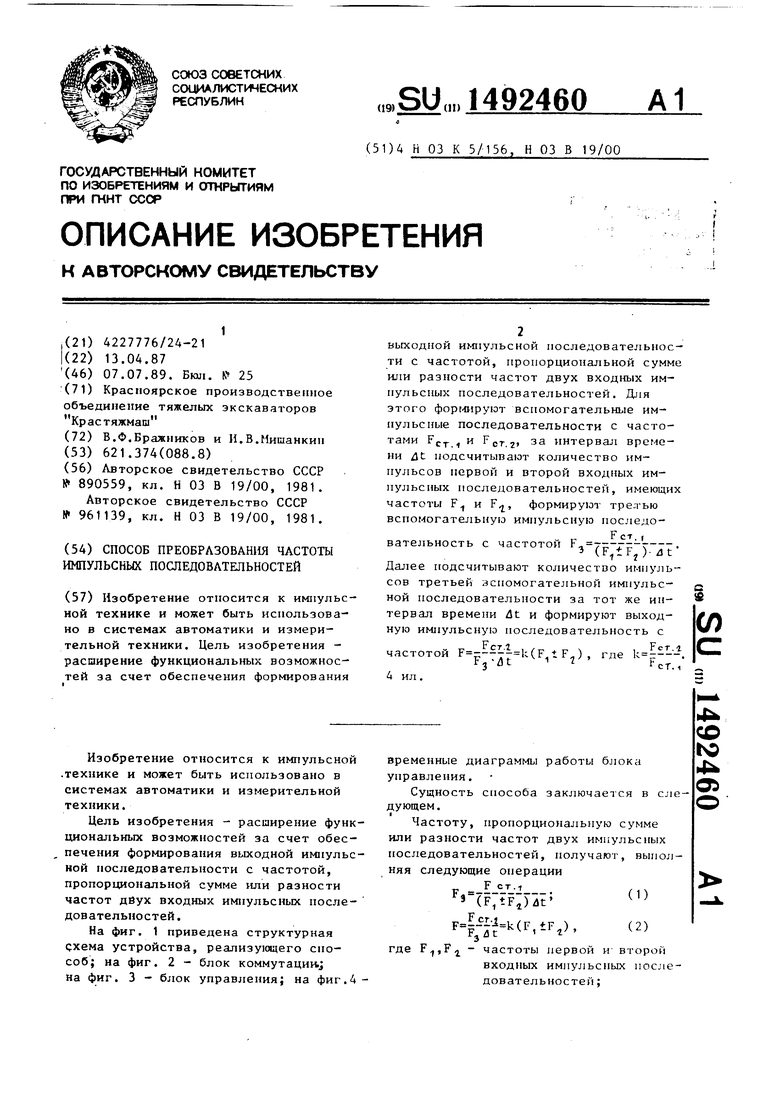

Блок 17 содержит делитель 24 частоты, на который подана вспомогательная импульсная последовательность с меньшей стабильной частотой. Импульсы с делителя 24 (фиг. 4,а) поступают на формирователь 25, импульсы с которого (фиг. 4,Ь) поступают на элемент 26 задержки и элемент 27 ИЛИ-НЕ, на второй

30

35

40

45

51

вхол элемента lUlH-HE 27 поступают импульсы после элемента 26 (фиг. ft,с). Назначение элемента 26 - задерживать импульс с формирователя 25 на время tj сСфиг, Д,с), элемента ИЛИ-НЕ 27 - формировать отрицательный импульс с длительностью, равной общему времени перекл 1очений в схеме t , (фиг . 4,d) . Время ме)зду двумя импульсами на лю- Оом из выходов блока 17 равно заданному интервалу времени /it, на котором подсчитывают импульсы преобразуемых последовательностей.

Устройство работает следующим об- разом.

На информационные входы первого и второго D-триггеров 1 и 2 подают входные последовательности импульсов На информационный вход третьего D- триггера 3 подают сигнал S, определяющий знак действия, выполняемого устройством, по следующему закону: если сигнал S имеет уровень логической единицы, го устройство выполняет сложение частот вход)1ых последовательностей, если сигнал S имеет уровень логического нуля, то устройство из последовательности иьшульсов с частотой F, вычитает последователь- ность импульсов с частотой F.

Отрицательный импульс (фиг.4,d) с блока 17, поданный на синхронизирующие входы перного и второго D- триггеров 1 и 2, задерживает проход возможных импульсов преобразуемых последовательностей на первый и второй счетчики 5 и 6.

Импульс, поданный на синхронизи- рующий вход третьего D-триггера 3, устанавливает его в с зответствии со знаком S , в связи с чем блок 8 выбирает направление счета второго счетчика 6. После окончания времени переключений схемы tJ,(фиг. 4,d) преобразуемые последовательности импульсо поступают на первый 5 и второй 6 счетчики. На выходе сумматора 9 накапливается информация о сумме или разности числа HMiiyjibcoB, преобразуемых последовательностей за заданный интервал времени лс, причем перенос в старший разряд с сумматора 9 не должен быть заде:1ствован в устройстве, так как в случае получения разности частот информация с второго счетчика 6 представлена в дополнительном коде, в этом случае значение

Q

5

0 5 о

,.

5

5

0

606

переноса и старший разряд и1-нориру- ется.

По окончании заданного интервала времени низкий уровень с блока 17 (фиг. 4,d) опять задерживает на время t f, f- прохождение в схему возможных импульсов преобразуемых последо- Baiельностей, а в это время передним фронтом импульса (фиг.4,Ь) осуществляется запись информации с сумматора 9 в первый регистр 10. Через время tj зСигналом с блока 17 (фиг-. 4, с), поданным на входы предварительной установки первого и второго счетчиков 5 и 6, производится их обнуление и одновременно с этим выбор направления счета второго счетчика 2 на следующий заданный интервал времени.

По окончании времени переключений t р с в течение следующего заданного интервала времени происходит новый счет импульсов преобразуемых последовательностей, а также деление импульсной последовательности со стабильной частотоуг Fj, на полученное ранее число, записанное в первом регистре 10. На выходе первого делителя 12 получается последовательность импульсов с частотой F, которая подсчитывается в счетчике 7, фиксируется во втором perncipe 11 и задает коэффициент деления второго делителя 13. Через промежуток времени, равный 24t, на выходе устройства получается последовательность импульсов с частотой (F,tF), импульсы которой распределены paBHOf-iepHo во времени.

Устройство работоспособно при выполнении следующих условий. Максимальная частота преобразуемых последовательностей импульсов должна быть не больше меньшей стабильной частоты вспомогательных импульсных последовательностей . макс с/мин

Время переключений в схеме не должно превышать половины периода максимальной частоты преобразуемых

последовательностей импульсов

1,1 Анакс

В случае получения разности частот уменьшаемая частота должна быть больше вычитаемой частоты, т.е. если F,-FI, то F,7/ F, .

При выполнении этих условий устройство обеспечивает следующие режимы работы: получение последовательности импульсов с частотой, пропорцио нальной сумме или разности частот, задаваемых двумя произвольными импульсными последовательностями, причем коэффициент пропорциональности может быть как равным, так и большим или меньшим единицы. Кроме того, устройство некритично к взаимному положению импульсов преобразуемых последовательностей.

Возможность задания как одной, так и обеих преобразуемых частот кодом. В этом случае численные значения частот подаются на входы предварительной записи счетчиков 5 и 6, уровень сигналов на информационных входах D-триггеров 1 и 2 должен быть постоянным, а в случае получения разности частот значение вычитаемой частоты должно быть представлено в коде Дополнение до двух.

При равенстве одной из преобразуемых частот нулю, например F, возможно получение импульсной последовательности регулируемой частоты

Формула изобретения Способ преобразования частоты импульсных последовательностей, включающий операции формирования первой

001.1

0

5

.

5

0

и второй вспомогательпых импульсных последовательностей и формирование третьей вспомогательной импульсной тюследовательности путем деления частоты первой вспомогательной импульсной последовательности на первый коэффициепт деления, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности формирования выходной т-тульсной последовательности с частотой, пропорциональной сумме или разности частот двух входных импульсных последовательностей, предварительно измеряют значение частот первой и второй входных импульсных последовательностей путем подсчета количеств импульсов этих последовательностей за заданный интервал времени, первый коэффициент деления формируют путем сложения или вычитания измеренных значений частот первой и второй входных импульсных последовательностей, а затем формируют второй коэффициент деления путем подсчета количества иш1ульсов третьей вспомогательной импульсной последовательности па том же заданном интервале времени и формируют выходную импульсную последовательность путем деления частоты второй вспомогательной импульсной последовательности на второй коэффициент деления.

(

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1444950A1 |

| Преобразователь частоты в код | 1978 |

|

SU744974A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| Устройство для коррекции числа импульсов по входному параметру | 1984 |

|

SU1187146A2 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Логарифмический преобразователь | 1978 |

|

SU765819A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1984 |

|

SU1233283A1 |

| Способ измерения функции изменения частоты импульсных сигналов с линейной частотной модуляцией | 1990 |

|

SU1748081A1 |

Изобретение относится к импульсной технике и может быть использовано в системах автоматики и измерительной техники. Цель изобретения - расширение функциональных возможностей за счет обеспечения формирования выходной импульсной последовательности с частотой, пропорциональной сумме или разности частот двух входных импульсных последовательностей. Для этого формируют вспомогательные импульсные последовательности с частотами F ст.1 и F ст.2, за интервал времени ΔТ подсчитывают количество импульсов первой и второй импульсных последовательностей, имеющих частоты F1 и F2, формируют третью вспомогательную импульсную последовательность с частотой F3 =F ст.1/(F1±F2)°ΔТ .Далее подсчитывают количество импульсов третьей вспомогательной импульсной последовательности за тот же интервал времени ΔТ и формируют выходную импульсную последовательность с частотой F=FCT2/F333ΔТ=K(F1±F2), где K=FCT.2/FCT.1 . 4 ил.

ФfJг.2

crt

2lt

6j

,f i n

1-r

n

-9

75

26

-0

Фиг.з

| Регулятор частоты | 1980 |

|

SU890559A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Частотно-импульсный преобразователь | 1981 |

|

SU961139A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-07—Публикация

1987-04-13—Подача