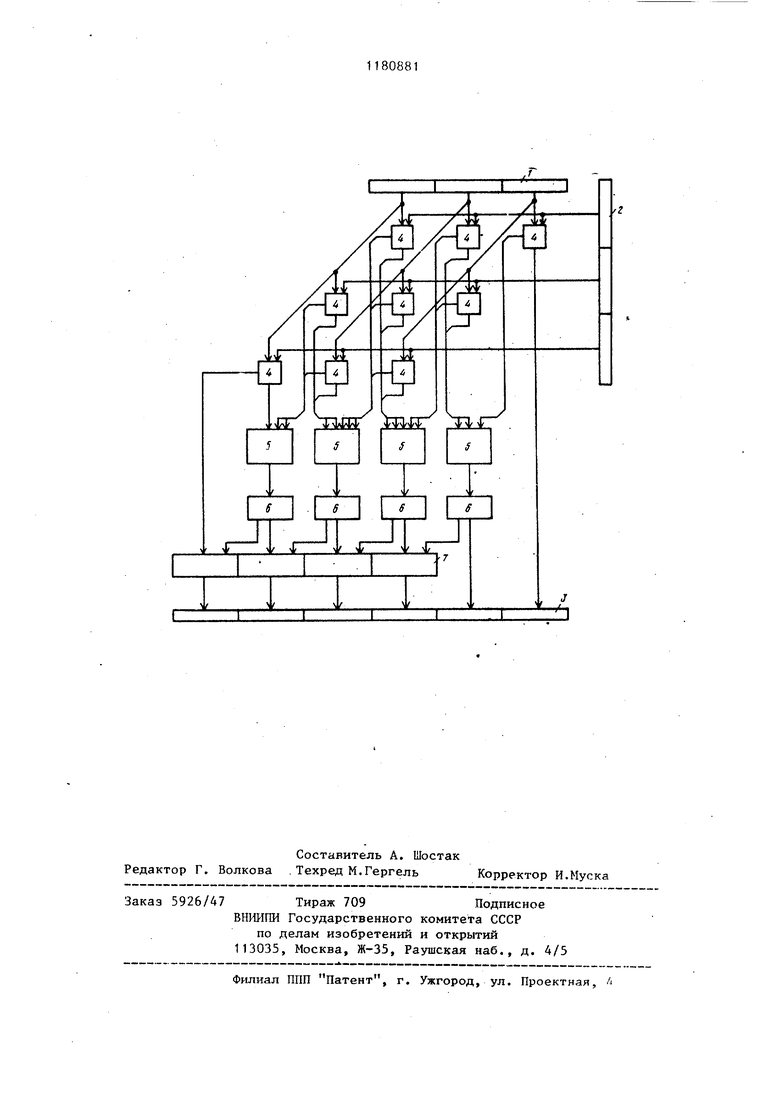

Изобретение относится к вычлслнтельной технике п может быть использовано для быстрого умножения десяти ных чисел, а также применено в чачес не основы при разработке универсальных быстродействующих устройств умно жения двоичных и десятичных чисел. Цель изобретения - сокращение количества оборудования устройства за счет упрощения используемых в нем преобразователей двоичного кода Б де сятичный из-за обеспечения меньшего диапазона преобразуемых в них чисел На чертеже приведена структурная схема предлагаемого устройства (для случая, когда число десятичных разря дов у множимого и у множителя равно трем). Устройство содержит регистры 1 множимого, множителя и произведения соответственно, матрицу блоков 4 умножения, двоичные сумматоры 5, преоб разователи 6 двоичного кода в десяти ный и десятичный сумматор 7. Первые входы блоков 4 умножения каждой стро ки матрицы соединены с выходами соот ветствующих тетрад регистра 1 множимого, вторые входы блоков 4 умножения каждого столбца матрицы соединен с выходами соответствующих тетрад регистра 2 множителя, входы k-го двоичного сумматора 5()с 1,2,3,4) соединены с выходами младших тетрад 1-X блоков 4 умножения j -х строк матрицы ( i 1,2,3; j 1,2,3; 1+ i k +2), выходы старших тетрад которых соединены с входами (k+1)-ro двоичного сумматора 5, выходы двоичных сумматоров 5 с первого по четвер тЬсй соединены с входами соответствующих преобразователей 6 Двоичного кода в десятичный, р-и выход g-го преобразователя 6 двоичного кода в десятичный соединен с входом () го разряда десятичного сумматора 7 (р 1,2; f 1,2,3,4), выходы младшей и старшей тетрад первого блока 4 умножения первой строки матрицы соединены соответственно с входом первой тетрады регистра 3 произведеНИН и входом первого двоичного сумматора 5, первый выход первого преобразователя 6 двоичного кода в десятичный соединен с входом второй тетрады регистра 3 произведения, . выходы младшей и старшей тетрад третьего блока 4 умножения третьей строки матрицы соединены соответстHSHHO с входом четвертого дьоичного сумматора 5 и входом четвертой тетрады десятичного сумматора 7, выходы разрядов с первогО по четвертый деСятичного сумматора 7 соединены с входами тетрад соответственно с третьей по шестую регистра 3 произведения. В устройстве блоки 4 умножения матрицы, двоичные сумматоры 5, преобразователи 6 двоичного кода в десятичньш и десятичньш сумматор 7 являются комбинационными схемами. Блок 4 умножения матрицы предназначен для перемножения двух десятичных цифр (цифры множимого и цифры множителя). На его выходах формируется двухразрядное произведение в десятичном коде. Пусть, например, цифра множимого равна 9, цифра множителя равна 7, и для представления десятичных цифр используется код прямого замещения 8 - 4 - 2 - 1. Тогда на выходах старшей тетрады блока 4 умножения сформируется код 0110, а на выходах его младшей тетра.тда код 0011, Блок 4 умножения может быть реализован по соответствующей таблице истинности на ПЗУ или в виде совокупности двоичного умножителя и преобразователя двоичного кода в десятичньй, причем выходы умножителя подключены cooтвeтcтвyюшJ м образом к входам преобразователя двоичного кода в десятичный или же другими известными методами и средствами. В каждом сумматоре 5 осуществляется двоичное суммирование младших цифр произведений, сформированных на выходах всех тех блоков 4 умножения, которые расположены в той же весовой десятичной позиции, что и данньш сумматор 5, и старших цифр произведений, сформированных на выходах всех тех блоков 4 умножения, которые расположены в соседней младшей весовой позиции по отношению к весовой десятичной позиции данного сумматора 5. С помощью преобразователей 6 осуществляется преобразование двоичных сумм, сформированных на выходах сумматоров 5, в десятичные суммы. Десятичный сумматор 7 выполняет суммирование с распространением переноса результатов, образованных на выходах преобразователей 6 двоичного кода в десятичный.

Устройство работает следующим образом.

Одновременно или прследовательно во времени в регистры 1 и 2 соответственно множимого и множителя загружаются десятичные сомножители. После загрузки операндов во входные регистры 1 и 2 устройства начинают работать блоки 4 умножения матрицы, с помощью которых формируются в дасятичном коде двухразрядные произведения десятичных цифр множимого и множителя. Сформированные на выходах |блоков 4 умножения матрицы значения младших и старших тетрад двухразрядных произведений поступают далее на .равновесовые входы сумматоров 5, где осуществляется их двоичное суммирование. Образованные на выходах сумматоров 5 двоичные суммы посредством преобразователей 6 преобразуются в десятичные суммы, которые поступают на равновесовые входы десятичного сумматора 7. Сформированная на выходах десятичного сумматор 7 сумма записывается в соответствующие разряды регистра 3 произведения, в первый разряд которого поступает значение младшей тетрады с выхода первого

блока 4 умножения nepBoii строки матрицы, а во второй разряд регистра 3 произведения подается результат, обрзованный на первом выходе первого преобразователя 6 двоичного кода в десятичный.

Таким образом, предложенное устроство для умножения можег быть принято за основу при разработке универсального быстродействующего устройства умножения двоичных и десятичных чис.т. Для этого необходимо в его блоках 4 умножения матрицы предусмотреть формирование значений тетрадных произведений как в десятичном коде, так и в двоичном, а вместо десятичного сумматора 7 использовать универсальный сумматор для сложения двоичных и десятичных чисел. Это устройство при умножении десятичных чисел работает так же, как и рассмотренное вьшге. Основное отличие при умножении на нем двоичных чисел состоит в том, что на входы сумматора 7 информация поступает не с выходов преобразователей 6 двоичного кода я десятичный, а непосредственно с выходов двоичных сумматоров 5.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1985 |

|

SU1259254A1 |

| Устройство для умножения | 1985 |

|

SU1262484A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| Устройство для умножения | 1985 |

|

SU1262481A1 |

| Устройство для умножения | 1989 |

|

SU1668979A1 |

| Устройство умножения двоично-десятичных цифр | 1982 |

|

SU1073771A1 |

| Устройство для умножения | 1981 |

|

SU1035600A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1003077A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее регистры множимого, множителя и произведения, матрицу блоков умножения, двоичные сумматоры, Преобразователи двоичного кода в десятичный и десятичный сумматор, причем первые входы блоков умножения казвдой строки матрицы соединены с выходами тетрад регистра множимого, вторые входы блоков умножения каждого столбца матрицы соединены с выходами соотвегствующих тетрад регистра множителя, причем входы k -го двоичного сумматора (k 1,...,N+M-3; N - число десятичных разрядов множимого; М - число десятичных разрядов множителя) соединены с выходами младших тетрад i -х блоков умножения ;j-x строк матрицы ( 1,...,N; j 1,.... ,М; i «- j 1 «- 2) , выходы двоичных сумматоров с первого по (К--М-2)-й соединены с входами соответствующих npeoCip,T.ionaTo.iieit дпоич110ГО кода в дecяти тf ыll, Р -и ныход -го преобразователя длоичиого кода л десятичный соединен с пходом (p+g-2)-ro разряда л,е1 ятич|1ого сумматора (р 1,...,Р; Р - число выХОД013 данного преобразовлтеля двоичного кода п десятичн1)1Й; 6 1,..., М+М-2), отличающееся тем, что, с целью сокращения количества оборудования, блоки умножения выполнены десятичными, выходы младшей и старшей тетрад первого блока умножения первой строки матрицы соединены соответственно с входом о первой тетрады регистра произведения (Л и входом первого двоичного сумматора, первьм выход первого преобразователя с двоичного кода в десятичный соединен с входом второй тетрады регистра произведения , выходы младшей и старшей тетрад N-го блока умножения М-и строки матрицы соединены соответственно с входом (+М-2)-го двоичного 00 О сумматора и входом (Н+М-2)-й тетрады десятичного сумматора, выходы старс ших тетрад i -х блоков ум1южения 00 j-X строк матрицы соединены с входами (/C4l)-ro двоичного сумматора,вы1ХОДЫ разрядов с первого по )-й десятичного сумматора соединены с входами тетрад соответственно с третьей по (()-m регистра произведения.

| Устройство для умножения | 1977 |

|

SU729587A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1981 |

|

SU1035600A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1983-04-29—Подача