Изобретение относится к вычислительной технике и, в частности, может быть использовано при проектировании комплексов на основе микро- ЭВМ с расширенными функциональными возможностями в тех случаях, когда число периферийных устройств, дополнительно подключенных к каналу мшсро- ЭВМ, превышает возможности основного канала (по нагрузке или по длине), при этом возможны параллел.ный, последовательный и п о следов а те ль но- параллельный принципы наращивания числа периферийных устройств.

Целью изобретения является расширение области применения.

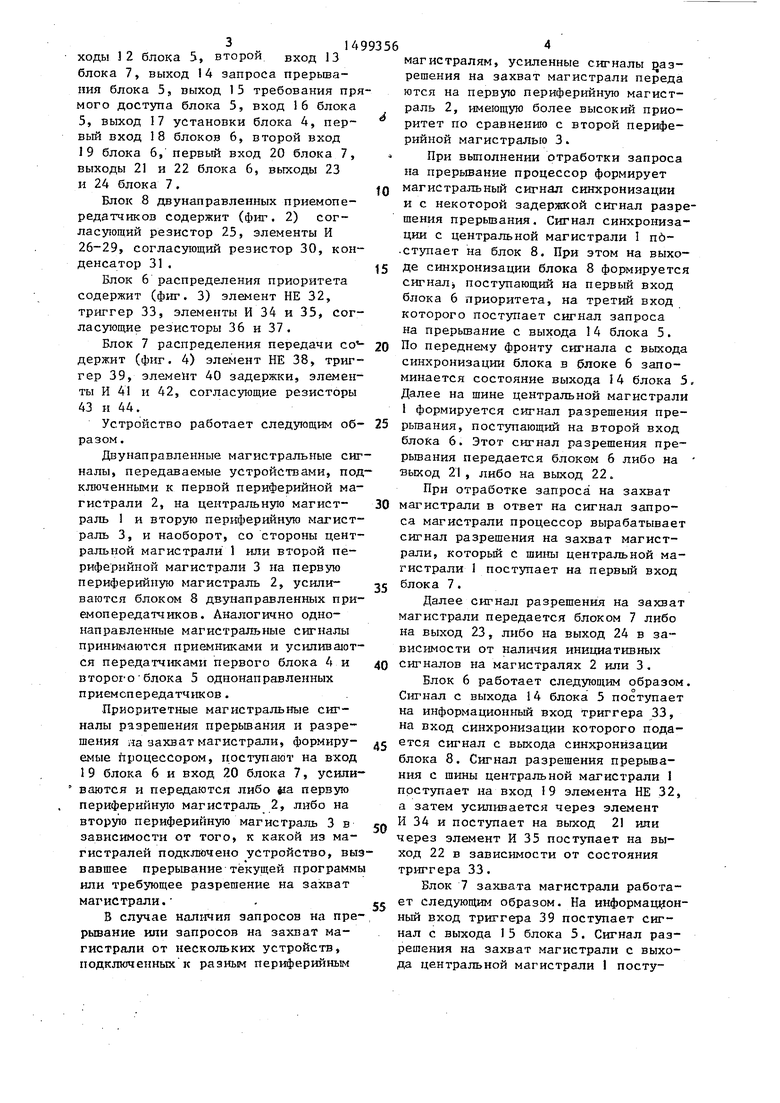

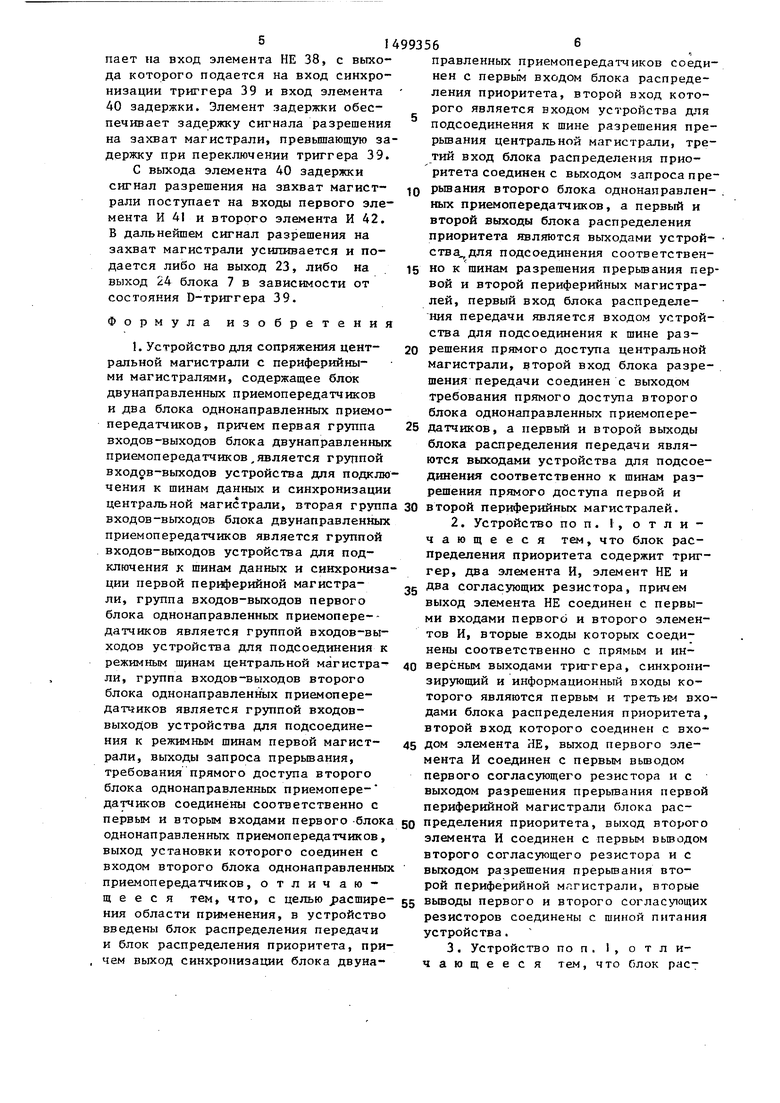

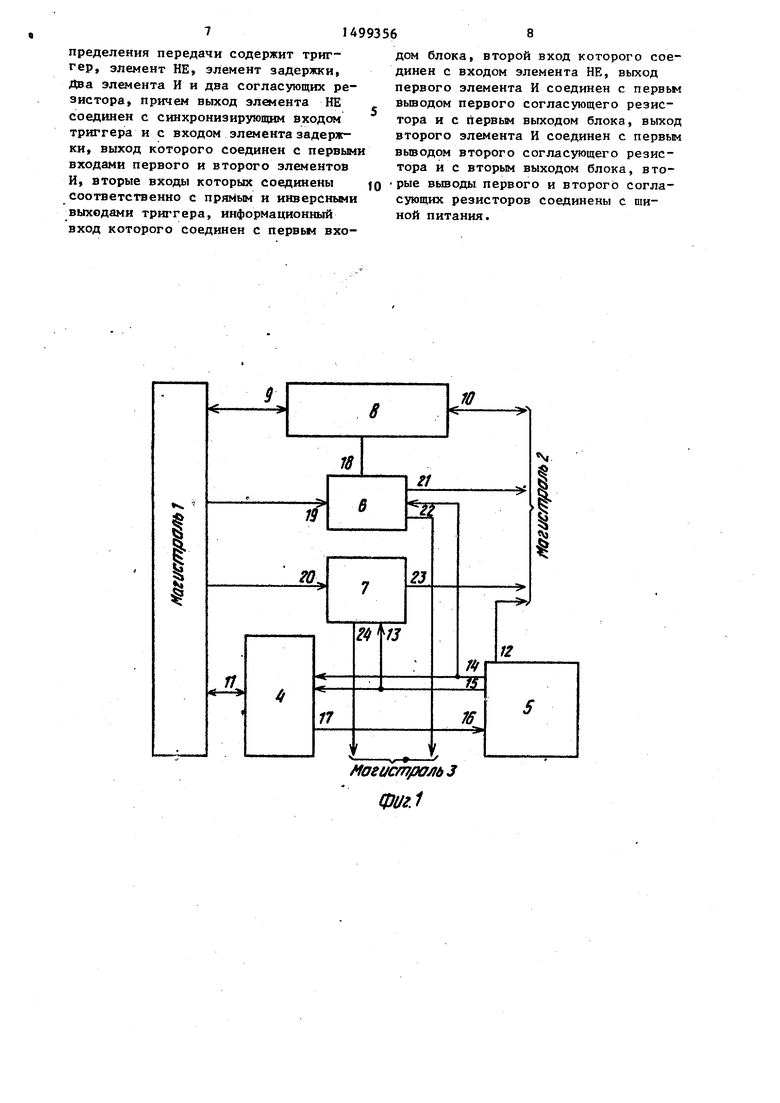

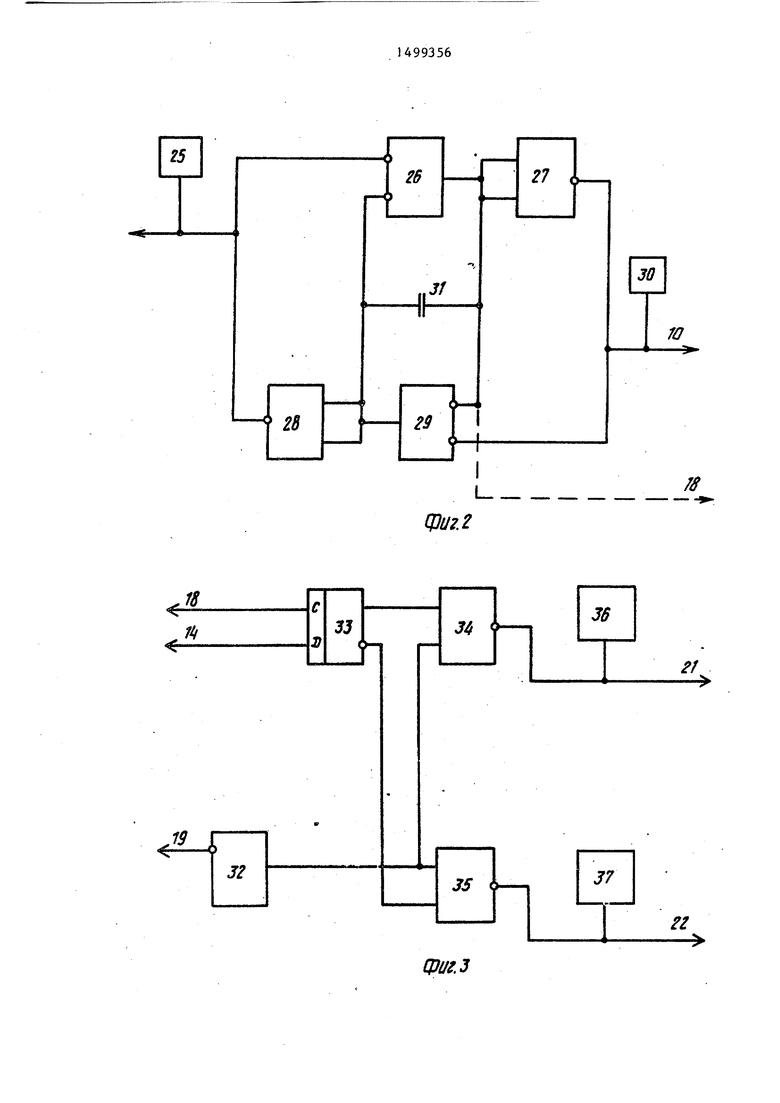

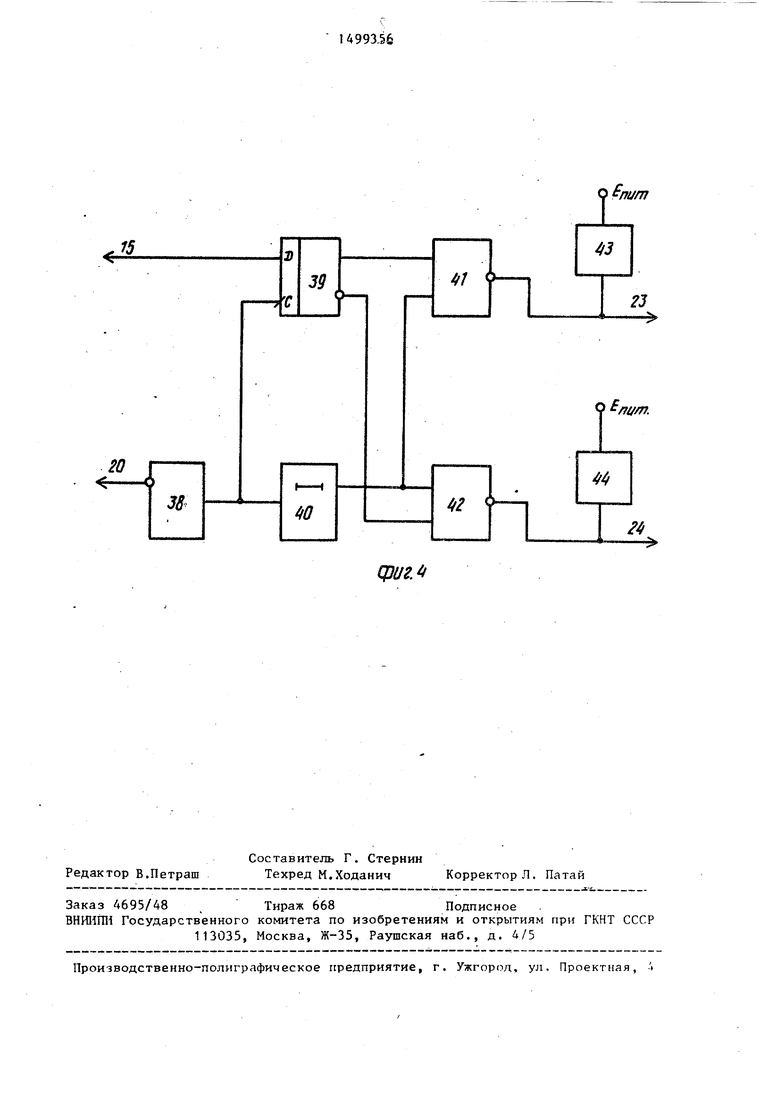

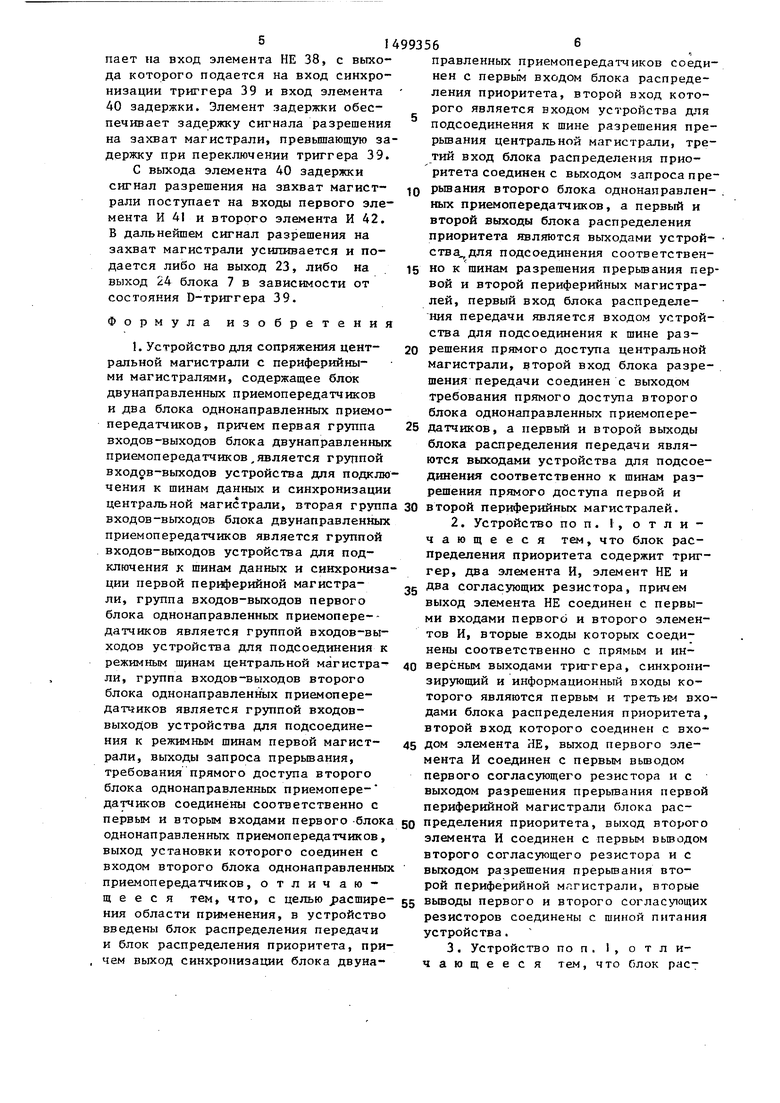

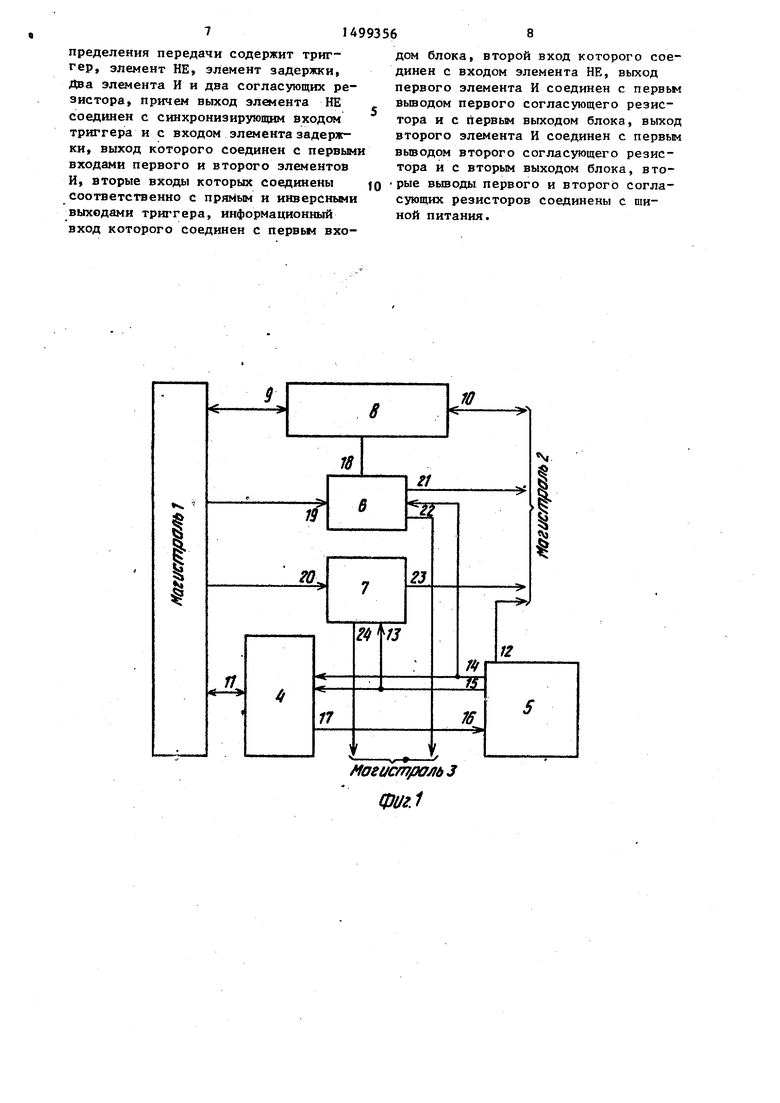

На фиг. I представлена блок-схема устройства; на фиг. 2 - схема блока двунаправленных приемопередатчиков на фиг. 3 - схема блока распределения приоритета; на фиг. 4 - схема блока распределения передачи.

На чертеже обозначены центральная магистраль I, первая периферийная магистраль 2 и вторая периферийная магистраль 3.

Устройство содержит блоки 4 и 5 однонаправленных приемопередатчиков, блок 6 распределения приоритета, блок 7 распределения передачи, блок 8 двунаправленных приемопередатчиков, входы-выходы 9 и 10 блокя 8, входы-выходы II блока 4, входы-ны4 СО СО

со сд

(У

31499356

ходы 12 блока 5, второй вход 13

блока 7, выход 14 запроса прерьша- ния блока 5, выход 15 требования прямого доступа блока 5, вход 16 блока 5, выход 17 установки блока 4, пер- вый вход 18 блоков 6, второй вход 19 блока 6, первый вход 20 блока 7, выходы 21 и 22 блока 6, выходы 23

и 24 блока 7.

to

Блок 8 двунаправленных приемопеедатчиков содержит (фиг. 2) согасующий резистор 25, элементы И 26-29, согласующий резистор 30, коненсатор 31 ,-с

Блок 6 распределения приоритета содержит (фиг. 3) элемент НЕ 32, триггер 33, элементы И 34 и 35, согасующие резисторы 36 и 37.

Блок 7 распределения передачи 20 ержит (фиг. 4) элемент НЕ 38, триггер 39, элемент 40 задержки, элементы И 41 и 42, согласующие резисторы 43 и 44.

Устройство работает следующим об- 25 разом.

Двунаправленные магистральные сигналы, передаваемые устройствами, подключенными к первой периферийной магистрали 2, на центральную магист- 30 раль 1 и вторую периферийную магистраль 3, и наоборот, со стороны центральной магистрали I или второй периферийной магистрали 3 на первзпо периферийную магистраль 2, усили- -sc ваются блоком 8 двунаправленных приемопередатчиков. Аналогично однонаправленные магистральные сигналы принимаются приемниками и усиливаются передат иками первого блока 4 и 40 второгоблока 5 однонаправленных приемопередатчиков.

Приоритетные магистральные сигналы разрешения прерьшания и разрешения яа захват магистрали, формиру- д емые процессором, поступают на вход 19 блока 6 и вход 20 блока 7, усюти- ваются и передаются либо а первую периферийную магистраль 2, либо на вторую периферийную магистраль 3 в ел зависимости от того, к какой из магистралей подключено устройство, вызвавшее прерьшание текущей программы или требующее разрешение на захват магистрали.-.J5

В случае наличия запросов на пре- рьшание или запросов на захват магистрали от нескольких устройств, подключенных к разным периферийным

с

0

5

0 c 0

л 5

магистралям, усиленные сигналы разрешения на захват магистрали переда ются на первую периферийную магистраль 2, имеющую более высокий приоритет по сравнению с второй периферийной магистралью 3.

При вьшолнении отработки запроса па прерьшание процессор формирует магистральный сигнал синхронизации и с некоторой задержкой сигнал разрешения прерьшания. Сигнал синхронизации с центральной магистрали 1 пй- .ступает на блок 8. При этом на выходе синхронизации блока 8 формируется cигнaЛj поступающий на первый вход блока 6 приоритета, на третий вход которого поступает сигнал запроса на прерьшание с выхода 14 блока 5. По переднему фронту сигнала с выхода синхронизации блока в блоке 6 запоминается состояние выхода i 4 блока 5 Далее на шине центральной магистрали 1 формируется сигнал разрешения прерьшания, поступающий на второй вход блока 6. Этот сигнал разрешения пре- рьшания передается блоком 6 либо на выход 21, либо на выход 22.

При отработке запроса на захват магистрали в ответ на сигнал запроса магистрали процессор вырабатывает сигнал разрешения на захват магистрали, которьй с шиШ)1 центральной магистрали 1 поступает на первый вход блока 7.

Далее сигнал разрешения на захват магистрали передается блоком 7 либо на выход 23, либо на выход 24 в зависимости от наличия инициативных сигналов на магистралях 2 или 3,

Блок 6 работает следующим образом. Сигнал с выхода 14 блока 5 поступает на информационный вход триггера 33, на вход синхронизации которого подается сигнал с выхода синхронизации блока 8. Сигнал разрешения прерывания с Ш1-ШЫ центральной магистрали 1 npCTjmaeT на вход 19 элемента НЕ 32, а затем усиливается через элемент И 34 и поступает на выход 21 или через элемент И 35 поступает на выход 22 в зависимости от состояния триггера 33.

Блок 7 захвата магистрали работает следующим образом. На информац он- ный вход триггера 39 поступает сигнал с выхода I5 блока 5. Сигнал разрешения на захват магистрали с выхода центральной магистрали I поступает на вход элемента НЕ 38, с выхода которого подается на вход синхронизации триггера 39 и вход элемента 40 задержки. Элемент задержки обеспечивает задержку сигнала разрешения на захват магистрали, превышающую задержку при переключении триггера 39.

С выхода элемента 40 задержки сигнал разрешения на захват магистрали поступает на входы первого элемента И 41 и второго элемента И 42. В дальнейшем сигнал разрешения на захват магистрали усиливается и подается либо на выход 23, либо на выход 24 блока 7 в зависимости от состояния D-триггера 39.

Формула изобретения

1. Устройство для сопряжения центральной магистрали с периферийными магистралями, содержащее блок двунаправленных приемопередатчиков и два блока однонаправленных приемопередатчиков, причем первая группа входов-выходов блока двунаправленных приемопередатчиков,является группой входов-выходов устройства для подключения к шинам данных и синхронизации

правленных приемопередатчиков соединен с первым входом блока распределения приоритета, второй вход которого является входом устройства для подсоединения к шине разрешения пре- рьшания центральной магистрали, третий вход блока распределения приоритета соединен с выходом запроса преQ рывания второго блока однонаправлен- . ных приемопередатчиков, а первый и второй выходы блока распределения приоритета являются выходами устрой- подсоединения соответствен5 но к шинам разрешения прерывания первой и второй периферийных магистралей, первый вход блока распределения передачи является входом устройства для подсоединения к шине раз0 решения прямого доступа центральной магистрали, второй вход блока разрешения передачи соединен с выходом требования прямого доступа второго блока однонаправленных приемопере5 датчиков, а первый и второй выходы блока распределения передачи являются выходами устройства для подсоединения соответственно к шинам разрешения прямого доступа первой и

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для сопряжения ЭВМ с магистралью ввода-вывода периферийных устройств | 1986 |

|

SU1397928A2 |

| Устройство для сопряжения процессоров в мультипроцессорной системе | 1984 |

|

SU1188747A1 |

| Контроллер с переменным приоритетом | 1980 |

|

SU907550A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств | 1988 |

|

SU1508220A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1982 |

|

SU1269142A1 |

| Устройство для обмена информацией между магистралью параллельного интерфейса и последовательным каналом | 1986 |

|

SU1444788A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

Изобретение относится к вычислительной технике ,в частности, оно может быть использовано при проектировании комплексов на основе микро ЭВМ с расширенными функциональными возможностями в тех случаях, когда число периферийных устройств, подключаемых к каналу микро ЭВМ, превышает его возможности. Целью изобретения является расширение области применения. Устройство содержит блок двунаправленных приемо-передатчиков, два блока однонаправленных приемо-передатчиков, блок распределения приоритета, блок распределения передачи. 2 з.п.ф-лы, 4 ил.

центральной магистрали, вторая группа ЗО второй периферийных магистралей, входов-выходон блока двунаправленных2. Устройство по п. 1, отличающееся

приемопередатчиков является группой входов-выходов устройства для подключения к шинам данных и синхронизации первой периферийной магистрали, группа входов-выходов первого блока однонаправленных приемопере-- датчиков является группой входов-выходов устройства для подсоединения к режимным шинам центральной магистра ли, группа входов-выходов второго блока однонаправленга 1х приемопередатчиков является группой входов- выходов устройства для подсоединения к режимным шинам первой магистрали, выходы запроса прерывания, требования прямого доступа второго блока однонаправленных приемопере- датчиков соединены соответственно с

тем, что блок распределения приоритета содержит триггер, два элемента И, элемент НЕ и

25 два согласующих резистора, причем выход элемента НЕ соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с прямым и ин40 версным выходами триггера, синхронизирующий и информационный входы которого являются первым и третьим входами блока распределения приоритета, второй вход которого соединен с вхо45 дом элемента НЕ, выход первого элемента И соединен с первым вьюодом первого согласующего резистора и с выходом разрешения прерьшания первой

периферийной магистрали блока рас- первым и вторым входами первого-блока go пределения приоритета, выход второго однонаправленных приемопередатчиков,элемента И соединен с первым выводом

выход установки которого соединен свторого согласующего резистора и с

входом второго блока однонаправленных выходом разрещения прерьюания вто- приемопередатчиков, отличаю-рой периферийной магистрали, вторые

щ е е с я тем, что, с целью асшире- 55 вьюоды первого и второго согласующих ния области применения, в устройстворезисторов соединены с шиной питания

введены блок распределения передачиустройства.

и блок распределения приоритета, при-3. Устройство по п. I, о т л ичем выход синхронизации блока двуна-чающееся тем, что блок расчающееся

тем, что блок распределения приоритета содержит триггер, два элемента И, элемент НЕ и

25 два согласующих резистора, причем выход элемента НЕ соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с прямым и ин40 версным выходами триггера, синхронизирующий и информационный входы которого являются первым и третьим входами блока распределения приоритета, второй вход которого соединен с вхо45 дом элемента НЕ, выход первого элемента И соединен с первым вьюодом первого согласующего резистора и с выходом разрешения прерьшания первой

пределения передачи содержит триггер, элемент НЕ, элемент задержки, Два элемента И и два согласующих резистора, причем выход элемента НЕ соединен с синхронизируюпщм входом триггера и с входом элемента задержки, выход которого соединен с первым входами первого и второго элементов И, вторые входы которых соединены соответственно с прямым и инверсными выходами триггера, информационный вход которого соединен с первьм входом блока, второй вход которого соединен с входом элемента НЕ, выход первого элемента И соединен с первьм вьшодом первого согласующего резистора и с первьм выходом блока, выход второго элемента И соединен с первым выводом второго соглас тощего резистора и с вторым выходом блока, вто- рые вьгооды первого и второго согласующих резисторов соединены с шиной питания.

V- маеистрользФиг.1

25

28

18

1

33

//

7

f

j/

L78

фиг,2

3ft

36

цзиг.з

15

пи/л

Ц)иг.

| Устройство для сопряжения источников и приемников с магистралью | 1984 |

|

SU1252788A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

Авторы

Даты

1989-08-07—Публикация

1987-05-04—Подача