И:) i t lpt TCHHe (I i HocirrcH к вычисли- TCjibHoii технике н может Оыть испольэовано в системах магистральной структуры для сопряжения приемников и источников информации, н частности серийно выг1ускае№,1х цифровых измерительных приборов с магистралью приборного интерфейса.

Цель изобретения - сокращение аппаратурных затрат.

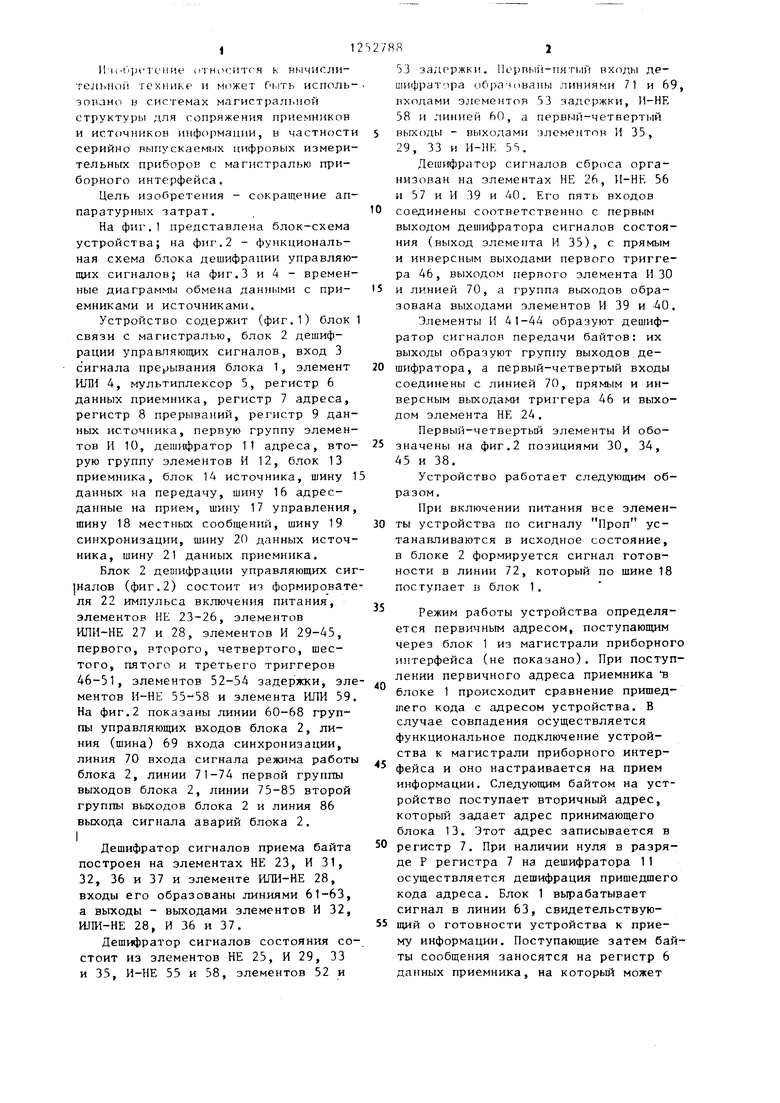

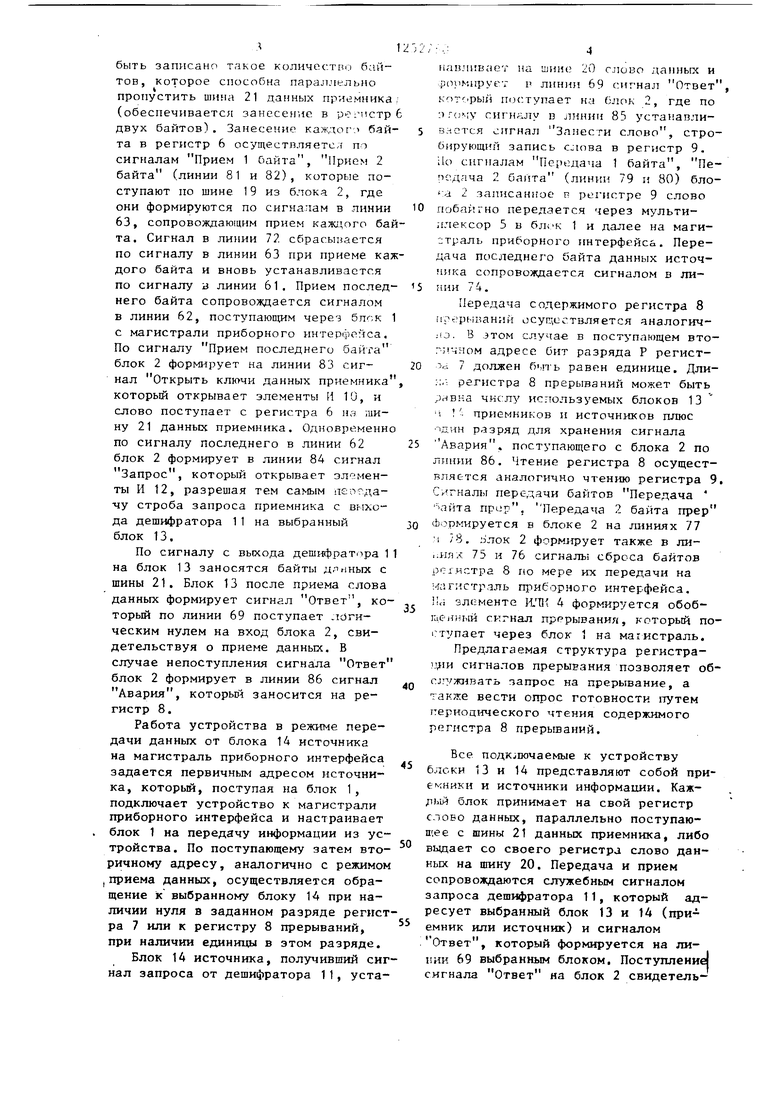

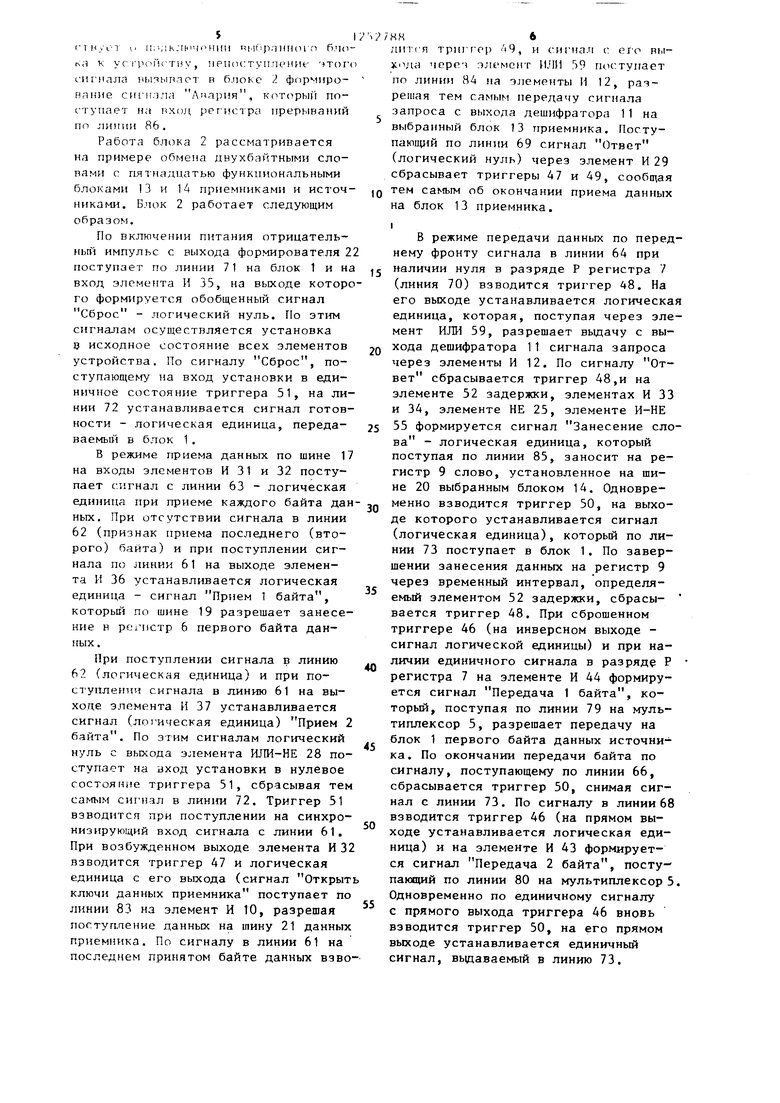

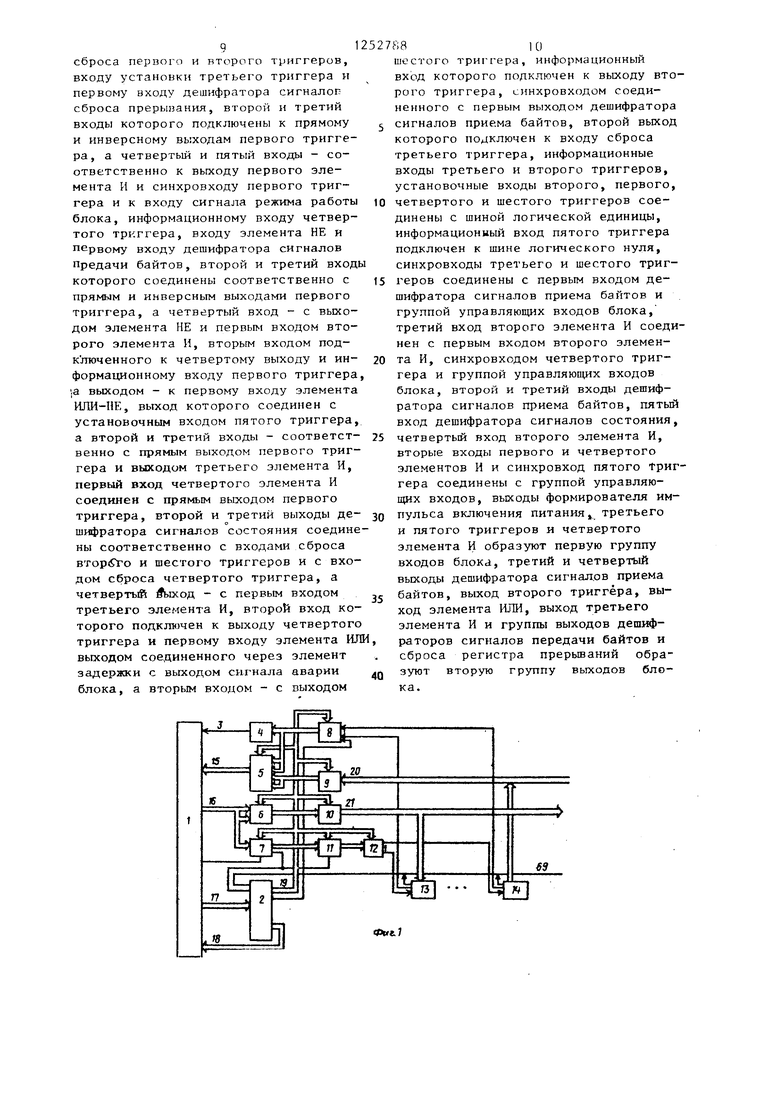

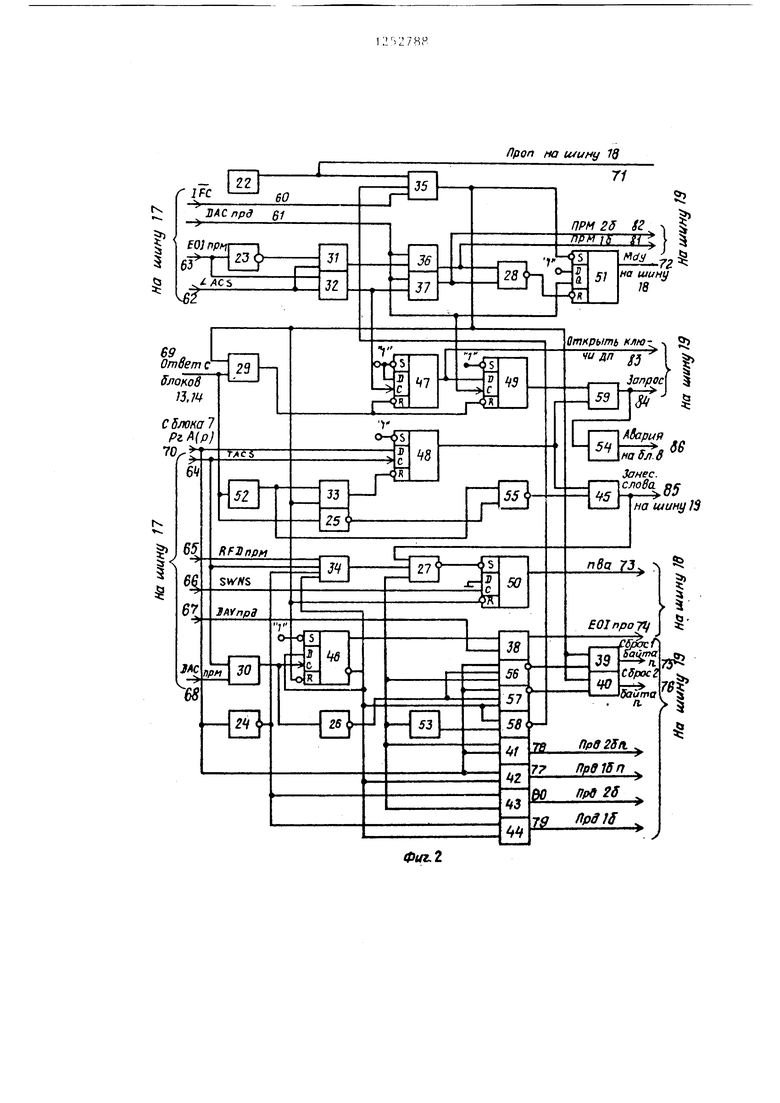

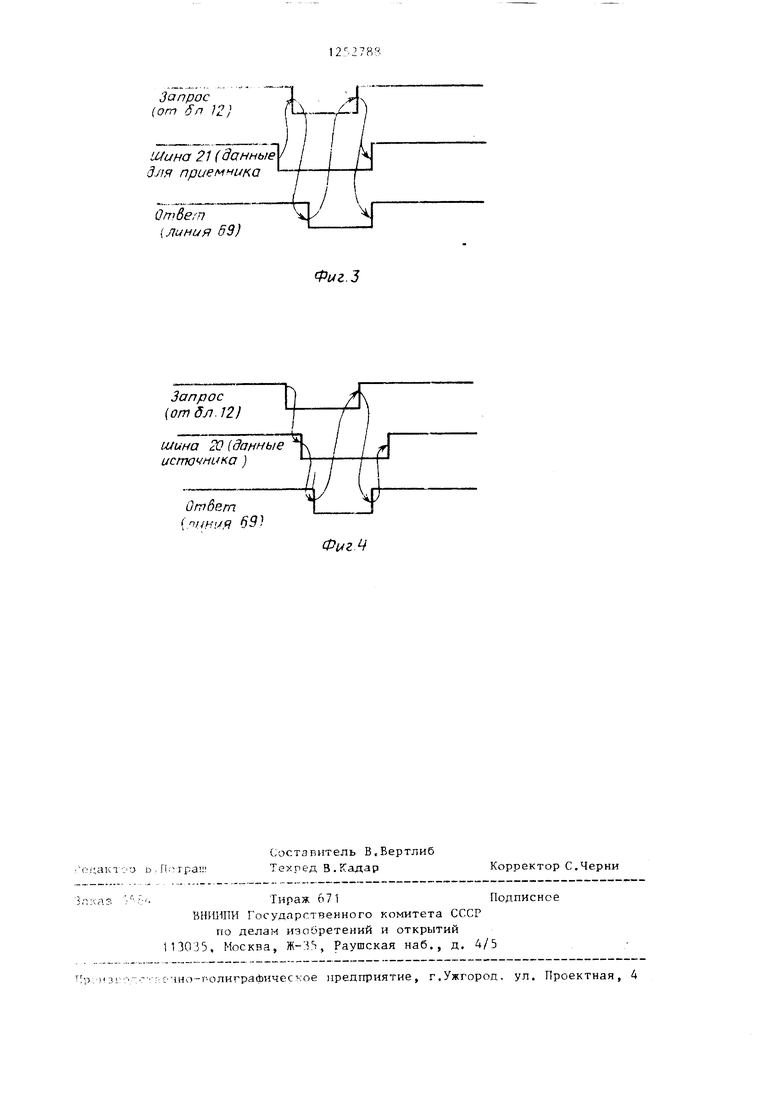

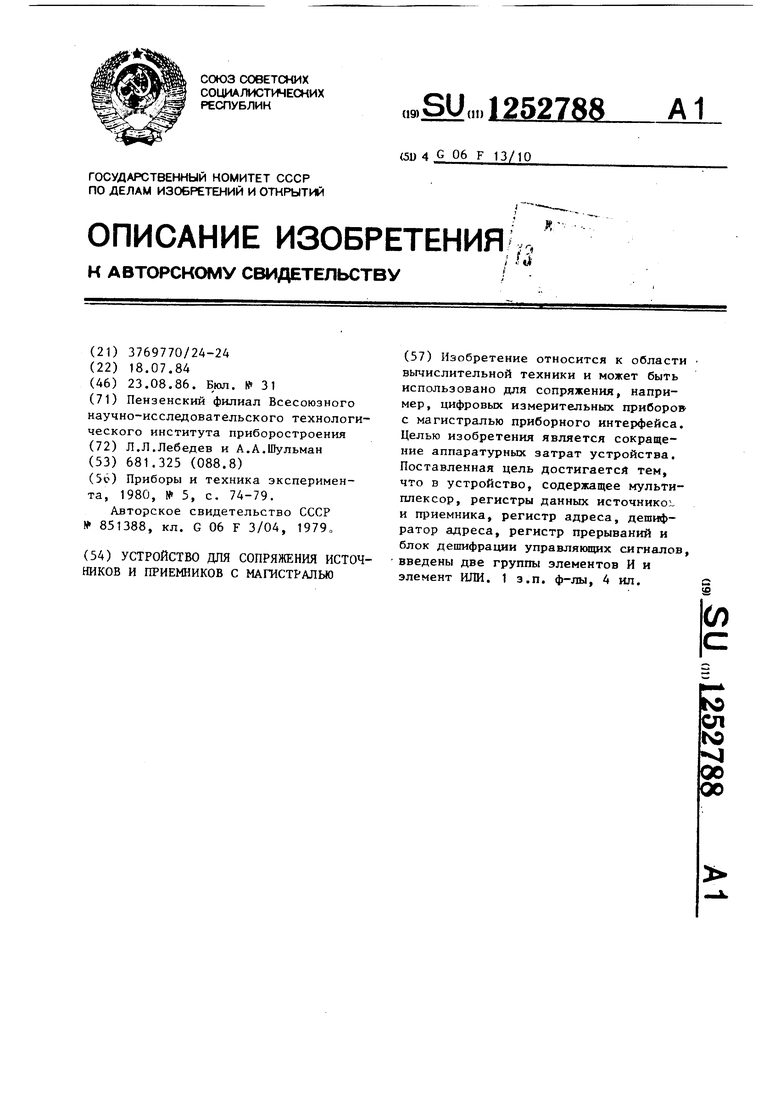

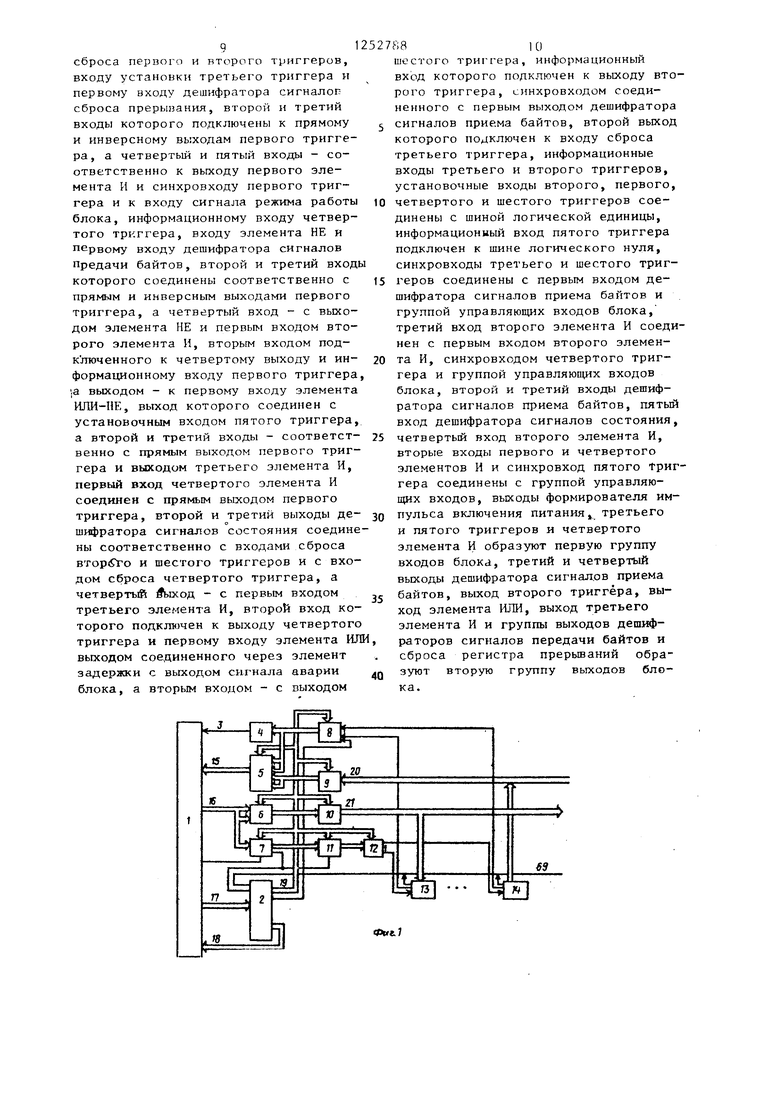

На фиг,1 представлена блок-схема устройства; на фиг.2 - функциональная схема блока дешифрации управляющих сигналов; на фиг.З и 4 - временные диаграммы обмена данными с приемниками и источниками.

Устройство содержит (фиг.1) блок связи с магистралью, блок 2 дешифрации управляющих сигналов, вход 3 сигнала прерывания блока 1, элемент ИЛИ 4, мультиплексор 5, регистр 6 данных приемника, регистр 7 адреса, регистр 8 прерываний, регистр 9 данных источника, первую группу элементов И 10, дешифратор 11 адреса, вторую группу элементов И 12, блок 13 приемника, блок 14 источника, шину 1 данных на передачу, шину 16 адрес- данные на прием, шину 17 управления, шину 18 местных сообщений, шину 19 синхронизации, шину 20 данных источника, шину 21 данных приемника.

Блок 2 дешифрации управляющих сиг {налов (фиг.2) состоит из формирователя 22 импульса включения питания, элементов НЕ 23-26, элементов Ш1И-НЕ 27 и 28, элементов И 29-45, первого, второго, четвертого, шестого, пятого и третьего триггеров 46-51, элементов 52-54 задержки, элементов И-НЕ 55-58 и элемента ИЛИ 59. На фиг.2 показаны линии 60-68 группы управляющих входов блока 2, линия (шина) 69 входа синхронизации, линия 70 входа сигнала режима работы блока 2, линии 71-74 первой группы выходов блока 2, линии 75-85 второй группы выходов блока 2 и линия 86 выхода сигнала аварий блока 2.

I

Дешифратор сигналов приема байта

построен на элементах НЕ 23, И 31, 32, 36 и 37 и элементе ИЛИ-НЕ 28, входы его образованы линиями 61-63, а выходы - выходами элементов И 32, ИЛИ-НЕ 28, И 36 и 37.

Дешифратор сигналов состояния состоит из элементов НЕ 25, И 29, 33 и 35, И-НЕ 55 и 58, элементов 52 и

53 задержки. Порпый-пятый входы дешифратора образованы линиями 71 и 69, входами элементов 53 задержки, И-НЕ 58 и линией 60, а первый-четвертый выходы - выходами :элементон И 35, 29, 33 и И-НЕ 5S.

Дешифратор сигналов сброса организован на элементах НЕ 26, И-НЕ 56 и 57 и И 39 и 40. Его пять входов соединены соответственно с первым выходом дешифратора сигналов состояния (выход элемента И 35), с прямым и инверсным выходами первого триггера 46, выходом первого элемента И 30 и линией 70, а группа выходов образована выходами элементов И 39 и -40.

Элементы И 41-44 образуют дешифратор сигналов передачи байтов: их выходы образуют группу выходов де- шифратора, а первый-четвертый входы соединены с линией 70, прямым и инверсным выходами триггера 46 и выходом элемента НЕ 24.

Первый-четвертый элементы И обо- значены на фиг.2 позициями 30, 34, 45 и 38,

Устройство работает следующим образом.

При включении питания все элемен- ты устройства по сигналу Проп устанавливаются в исходное состояние, в блоке 2 формируется сигнал готовности в линии 72, который по шине 18 поступает в блок 1.

Режим работы устройства определяется первичным адресом, поступающим через блок 1 из магистрали приборного интерфейса (не показано). При поступлении первичного адреса приемника в блоке 1 происходит сравнение пришедшего кода с адресом устройства. В случае совпадения осуществляется функциональное подключение устройства к магистрали приборного интерфейса и оно настраивается на прием информации. Следующим байтом на устройство поступает вторичный адрес, который задает адрес принимающего блока 13. Этот адрес записывается в

регистр 7. При наличии нуля в разряде Р регистра 7 на дешифратора 11 осуществляется дешифрация пришедшего кода адреса. Блок 1 вьфабатывает сигнал в линии 63, свидетельствующий о готовности устройства к приему информации. Поступающие затем байты сообщения заносятся на регистр 6 данных приемника, на который может

.

быть записано такое колнчсстпо тов, которое способна параллельно прог:устить шима 21 данных приемника (обеспечивается занесение в рн ;-истр двух байтов) . Занесение каждог, бай- та в регистр 6 осуществляетсл по сигналам Прием 1 байта, Прием 2 байта (линии 81 и 82), которые поступают по шине 19 из блока 2, где они формируются по сигналам в линии 63, сопровождающим прием каж1;ого байта. Сигнал в линии 72 сбрасывается по сигналу в линии 63 при приеме каждого байта и вновь устанавливается по сигналу в линии 61. Прием послед- него байта сопровождается сигналом в линии 62, поступаюпщм через блок с магистрали приборного интерфейса. По сигналу Прием последнего байта блок 2 формирует на линии 83 сиг- нал Открыть ключи данных приемника который открывает элементы И 10, и слово поступает с регистра 6 на шину 21 данных приемника. Одновременно по сигналу последнего в линии 62 блок 2 формирует в линии 84 сигнал Запрос, который открывает элементы И 12, разрешая тем самым пепгда- -чу строба запроса приемника с выхода дешифратора 11 на выбранный блок 13,

По сигналу с выхода дешифратора 1 на блок 13 заносятся байты длнных с шины 21. Блок 13 после приема слова данных формирует сигнал Ответ, ко- торый по линии 69 поступает логическим нулем на вход блока 2, свидетельствуя о приеме данных. В случае непоступления сигнала Ответ блок 2 формирует в линии 86 сигнал Авария, который заносится на регистр В.

Работа устройства в режиме передачи данных от блока 14 источника на магистраль приборного интерфейса задается первичным адресом источника, который, поступая на блок 1, подключает устройство к магистрали приборного интерфейса и настраивает блок 1 на передачу информации из устройства. По поступающему затем вто- pHMHONfy адресу, аналогично с режимом (Приема данных, осуществляется обращение к выбранному блоку 14 при наличии нуля в заданном разряде регистра 7 или к регистру 8 прерываний, при наличии единицы в этом разряде.

Блок 14 источника, получивший сигнал запроса от дешифратора 11, уста

5 Ю 5 20 25 зо

, ,

5

0

5

навливает на шине 20 слово данных и -pcijivaipyev i линии 69 сигнал Ответ, котг рый пог.тупает на блок 2, где по : .;у сигналу в линии 85 устанавли- гз.чстся сигнал Занести слово, стро- бирующий запись слова в регистр 9. ;1о сигналам Передача 1 байта, Пе- педача 2 байта (линии 79 и 80) бло- :а 2 записанное R регистре 9 слово побаягно передается через мультиплексор 5 в блек 1 и далее на маги- -траль приборного интерфейса. Передача последнего байта данных источника сопровождается сигналом в линии 74.

Передача содержимого регистра 8 прерываний осуществляется аналогич- ;(о. В этом случа-е в поступающем вторичном адресе бит разряда Р регист- -с. 7 должен быть равен единице. Дли- ::.. регистра 8 прерываний может быть рнвка числу используемых блоков 13 -. . приемников и источников плюс 1ДИН разряд для хранения сигнала Авария, поступающего с блока 2 по линии 86. Чтение регистра 8 осуществляется аналогично чтению регистра 9. Сигналы передачи байтов Передача айта прер. Передача 2 байта прер Формируется в блоке 2 на линиях 77 I /8. ;хаок 2 форм1трует также в ли- ,;иях 75 и 76 сигналы сброса байтов рс-гистра 8 по мере их передачи на магистраль приборного интерфейса. iici элементе ШИ 4 формируется обоб- гаеиный сигнал прерывания, который по- 1:тупает через блок 1 на магистраль.

Предлагаемая структура регистра- 11Д1и сигналов прерывания позволяет об- сл:ужнвать запрос на прерывание, а также вести опрос готовности путем 1териоаического чтения содержимого регистра 8 прерываний.

Все подключаемые к устройству блоки 13 и 14 представляют собой приемники и источники информации. Каж- лый блок принимает на свой регистр слово данных, параллельно поступающее с шины 21 данных приемника, либо выдает со своего регистра слово данных на шину 20. Передача и прием сопровождаются служебным сигналом запроса дешифратора 11, который адресует выбранный блок 13 и 14 (приемник или источник) и сигналом Ответ, который формируется на ли- 69 выбранным блоком. Поступление сигнала Ответ на блок 2 свидетельJI

rinv oi . iKMK. iH Monun Ri-if panHnrfi 5.4(1- ка к ус гропгтну, iiPiKiCTyiT.nennf чтог о сиг иала тилпыпаот в блоке 2 фг)рмиро- Екание сш илла Ляария, кс ТорыГ поступает на пход perncipa прерываний по jniiiHH 86 ,

Работа бл(5ка 2 рассматривается на примере обмена двухбайтными словами с гштнадпатью функпиональными блоками 13 и 14 приемниками и источниками. Блок 2 работает следующим образом.

По включении питания отрицатель- ньпЧ импульс с выхода формирователя 22 поступает по линии 71 на блок 1 и на вход элемента И 35, на выходе которого формируется обобщенный сигнал Сброс - логический нуль. По этим сигналам осуществляется установка IJ исходное состояние всех элементов устройства. По сигналу Сброс, по- cтyпaющe fy на вход установки в единичное состояние триггера 51, на линии 72 устанавливается сигнал готовности - логическая единица, переда- ваемьш в блок 1 .

В режиме приема данных по шине 17 на входы элементов И 31 и 32 поступает сигнал с линии 63 - логическая единица при приеме каждого байта данных. При отсутствии сигнала в линии 62 (признак приема последнего (второго) байта) и при поступлении сигнала по линии 61 на выходе элемента И 36 устанавливается логическая единица - сигнал Прием 1 байта, который по шине 19 разрешает занесение н pOi ncTp 6 первого байта данных .

При поступлении сигнала в линию 62 (логическая единица) и при поступлении сигнала в линию 61 на выходе элемента И 37 устанавливается сигнал (логическая единица) Прием 2 байта. По этим сигналам логический нуль с выхода элемента ИЛИ-НЕ 28 поступает на аход установки в нулевое состояние триггера 51, сбрасывая тем самым сигнал в линии 72. Триггер 51 взводится при поступлении на синхронизирующий вход сигнала с линии 61, При возбужденном выходе элемента И 32 взводится триггер 47 и логическая единица с его выхода (сигнал Открыт ключи данных приемника поступает по линии 83 на элемент И 10, разрешая постуааение данных на шину 21 данных приемника. По сигналу в линии 61 на последнем принятом байте данных взво/ /KK6

/пи сп триггер А9, и сигнал с. ег о выХ чда череч элемент ИЛИ 39 поступает по линии 84 на элементы И 12, разрешая тем самым передачу сигнала запроса с выхода дешифратора 11 на выбранный блок 13 приемника. Поступающий по линии 69 сигнал Ответ (логический нуль) через элемент И 29 сбрасывает триггеры 47 и 49, сообщая Q тем самым об окончании приема данных на блок 13 приемника.

I

В режиме передачи данных по переднему фронту сигнала в линии 64 при

5 наличии нуля в разряде Р регистра 7 (линия 70) взводится триггер 48. На его выходе устанавливается логическая единица, которая, поступая через элемент ИЛИ 59, разрешает выдачу с вы0 хода дешифратора 11 сигнала запроса через элементы И 12. По сигналу Ответ сбрасывается триггер 48,и на элементе 52 задержки, элементах И 33 и 34, элементе НЕ 25, элементе И-НЕ

5 55 формируется сигнал Занесение слова - логическая единица, который поступая по линии 85, заносит на регистр 9 слово, установленное на шине 20 выбранным блоком 14. Одновре менно взводится триггер 50, на выходе которого устанавливается сигнал (логическая единица), который по линии 73 поступает в блок 1. По завершении занесения данных на регистр 9 через временный интервал, определяемый элементом 52 задержки, сбрасы- вается триггер 48. При сброшенном триггере 46 (на инверсном выходе - сигнал логической единицы) и при на личии единичного сигнала в разряду Р регистра 7 на элементе И 44 формируется сигнал Передача 1 байта, который, поступая по линии 79 на ль- типлексор 5, разрешает передачу на блок 1 первого байта данных источника. По окончании передачи байта по сигналу, поступающему по линии 66, сбрасывается триггер 50, снимая сигнал е линии 73. По сигналу в линии 68 взводится триггер 46 (на прямом выходе устанавливается логическая единица) и на элементе И 43 формируется сигнал Передача 2 байта, посту- пакхций по линии 80 на мультиплексор 5. Одновременно по единичному сигналу с прямого выхода триггера 46 вновь взводится триггер 50, на его прямом выходе устанавливается единичный сигнал, вьдаваемый в линию 73.

5

5

0

5

7

При пгро.чпче ч(и:ледие 11 б. регистра 9 на члемеито И 58 IK; мремеи- мой чйдёржке на элементе 51 яадерж ки формируется сигнал Передача закончена, который, поступая на эле- мент И 35, формирует обобщенный сигнал Сброс (логический нуль), по кoтopo ry сбросятся все элементы уст- |ройства. Передача последнего байта сопровождается сигналом в линии 74, который формируется по сигналу в линии 67 на элементе И 38, с выхода которого поступает в блок 1 по линии 74. Чтение регистра 8 прерываний осуществляется аналогично, В этом случае разряд Р регистра 7 равен единице и триггер 50 взводится при совпадении на элементе И 34 сигналов линий 65 и 64, Сигнал Передача 1 байта прерывания формируется на элементе И 42 при сброшенном триггере 46, На элементе И 41 формируется сигнал Передача 2 байта прерывания сигналы, поступая на мультиплексор 5 по линиям 77 и 78, разрешают переда- чу содержимого регистра 8, После передачи каждого байта на элементах И-НЕ 56, И 39, И-НЕ 58, И 40 формируются сигнал1 1 Сброс 1 байта прерывания и Сброс 2 байта прерывания (линии 75 и 76),

Формула изобретения

1, Устройство для сопряжения ис- точников и приемников с магистралью содержащее регистры данных источников, соединенные, информационным входом с информационными выходами источников, регистр прерываний, соединенный группой информационных входов с выходами запросов прерывания источников и приемников, регистр данных приемника и регистр адреса, информационные входы которых соединены с информационным выходом блока связи с магистралью, дешифратор адреса, группой информационных входов подключенный к группе выходов регистра адреса, мультиплексор, выход которого соединен с информационным входом блока связи с магистралью, а первый информационный вход - с выходом регистра данных источника, и блок дешифрации управляю1цих сигналов, групп управляющих входов и первая группа вькодов которого соединены соответственно с группами управляющих входов

.-

to 15 20 , 25 зо

5 , а55

и Г1мход(м блока сняэи с магистралью, ;(х.)д (инхр(. - с выходами сигнала ответа источников и приемников, а вторая группа выходов - с управляющими входами регистра адреса, дешифратора адреса, регистров данных источника и приемника, регистра прерываний и мультиплексора, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены две группы элементов И и элемент ИЛИ, причем информационный вход регистра прерываний подключен к выходу сигнала аварии блока дешифра- |Ции управляющих сигналов, вторая группа выходов которого подключена к управляющим входам элементов И первой и второй групп и входу сброса регистра прерываний, группа выходов которого соединена с вторым информационным входом мультиплексора и группой входов элемента ИЛИ, выходом подключенного к входу сигнала прерываний блока связи с магистралью, информационные входы элементов И первой группы соединены с выходом регистра данных приемника, а вькоды - с информационными входами приемников, информационные входы элементов И агорой группы подключены к выходам дешифратора адреса, а выходы - к входам запроса соответствукяцих приемников и источников, вход сигнала режима работы блока дешифрации управляющих сигналов соединен с соответствующим разрядом группы выходов регистра адреса, стробирующий вход которог о соединен с выходом сигнала сопровождения адреса блока связи с магистралью,

2, Устройство по п,1, о т л и - чающееся тем, что блок дешифрации управляющих сигналов содержит шесть триггеров, дешифратор сигналов приема байта, дешифратор сигналов состояния, дешифратор сигналов сброса регистра прерывания, дешифратор сигналов передачи байтов, формирователь импульса включения питания, элемент ИЛИ, элемент задержки, четыре элемента И, элемент ИЛИ-НЕ и элемент НЕ, причем первый-четвертый входы дешифратора сигналов состояния подключены соответственно к выходу, формирователя импульсов включения питания, входу синхронизации блока и прямому и инверсному выходам первого триггера, первый выход - к входам

q

сброса первого и второго триггеров, входу установки третьего триггера и первому входу дешифратора сигналоп- сброса прерынания, второй и третий входы которого подключены к прямому и инверсному выходам первого триггера, а четвертый и пятый входы - соответственно к выходу первого элемента И и синхровходу первого триггера и к входу сигнала режима работы блока, информационному входу четвертого триггера, входу элемента НЕ и первому входу дешифратора сигналов предачи байтов, второй и третий вход которого соединены соответственно с прямым и инверсным выходами первого триггера, а четвертый вход - с выходом элемента НЕ и первым входом второго элемента И, вторым входом подключенного к четвертому выходу и информационному входу первого триггера .а выходом - к первому входу элемента ИЛИ-ПЕ, выход которого соединен с установочным входом пятого триггера, а второй и третий входы - соответственно с прямым выходом первого триггера и выходом третьего элемента И, первый вход четвертого элемента И соединен с прямым выходом первого триггера, второй и третий выходы дешифратора сигналов состояния соединены соответственно с входами сброса и шестого триггеров и с входом сброса четвертого триггера, а четвертый - с первым входом третьего элемента И, второй вход которого подключен к выходу четвертого триггера и первому входу элемента ИЛ выходом сое,циненного через элемент задержки с выходом сигнала аварии блока, а вторым входом - с выходом

1252788

С)

10

5

0

5

0

5

шестого триггера, информационный вход которого подключен к выходу второго триггера, синхровходом соединенного с первым выходом дешифратора сигналов приема байтов, второй выход которого подключен к входу сброса третьего триггера, информационные входы третьего и второго триггеров, установочные входы второго, первого, четвертого и шестого триггеров соединены с шиной логической единицы, информационный вход пятого триггера подключен к шине логического нуля, синхровходы третьего и шестого триггеров соединены с первым входом дешифратора сигналов приема байтов и группой управляющих входов блока, третий вход второго элемента И соединен с первым входом второго элемента И, синхровходом четвертого триггера и группой управляющих входов блока, второй и третий входы дешифратора сигналов приема байтов, пятьй вход дешифратора сигналов состояния, четвертый вход второго элемента И, вторые входы первого и четвертого элементов И и синхровход пятого tpHr- гера соединены с группой управляющих входов, выходы формирователя импульса включения питания, третьего и пятого триггеров и четвертого элемента И образуют первую группу входов блока, третий и четвертый выходы дешифратора сигналов приема байтов, выход второго триггера, выход элемента ИЛИ, выход третьего элемента И и группы выходов дешифраторов сигналов передачи байтов и сброса регистра прерьшаний образуют вторую группу выходов блока.

Фке.7

Проп на tuuHy 1в

, ,. ,, .

на шину /5

у

Запрос

(от 5п 12)

Мина 21 (данные для приемника

Ответ (Линия 69)

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистрали приборного интерфейса с магистралью микро-ЭВМ | 1986 |

|

SU1368885A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения источников и приемников с магистралью | 1986 |

|

SU1363227A2 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1251093A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

Изобретение относится к области вычислительной техники и может быть использовано для сопряжения, например, цифровых измерительных приборов с магистралью приборного интерфейса. Целью изобретения является сокращение аппаратурных затрат устройства. Поставленная цель достигается тем, что в устройство, содержащее мультиплексор, регистры данных источников и приемника, регистр адреса, дешифратор адреса, регистр прерываний и блок дешифрации управляющих сигналов, введены две группы элементов И и элемент ИЛИ. 1 з.п. ф-лы, 4 ип. с (О

Запрос (от дл. 12}

Шина Л7 (данные )

Ответ (/ /w. /.f 91

-lUiKTC O ь , И; тра;::

{Доставитель В.Вертлиб Техред В.Кадар

Тираж 671Подписное

ВНИППИ Государственного комитета СССР

по делам изобретений и открытий ПЗОЗЗ, Москва, Ж-:1, Раушская наб., д. 4/5

;:ечно-ролиграфнческое предприятие, г.Ужгород, ул. Проектная, 4

Корректор С,Черни

Авторы

Даты

1986-08-23—Публикация

1984-07-18—Подача