Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных комплексах.

Цель изобретения - расширение функциональных возможностей устройства путем обеспечения работы периферийных устройств в режиме прямого доступа к памяти (ПДП). .

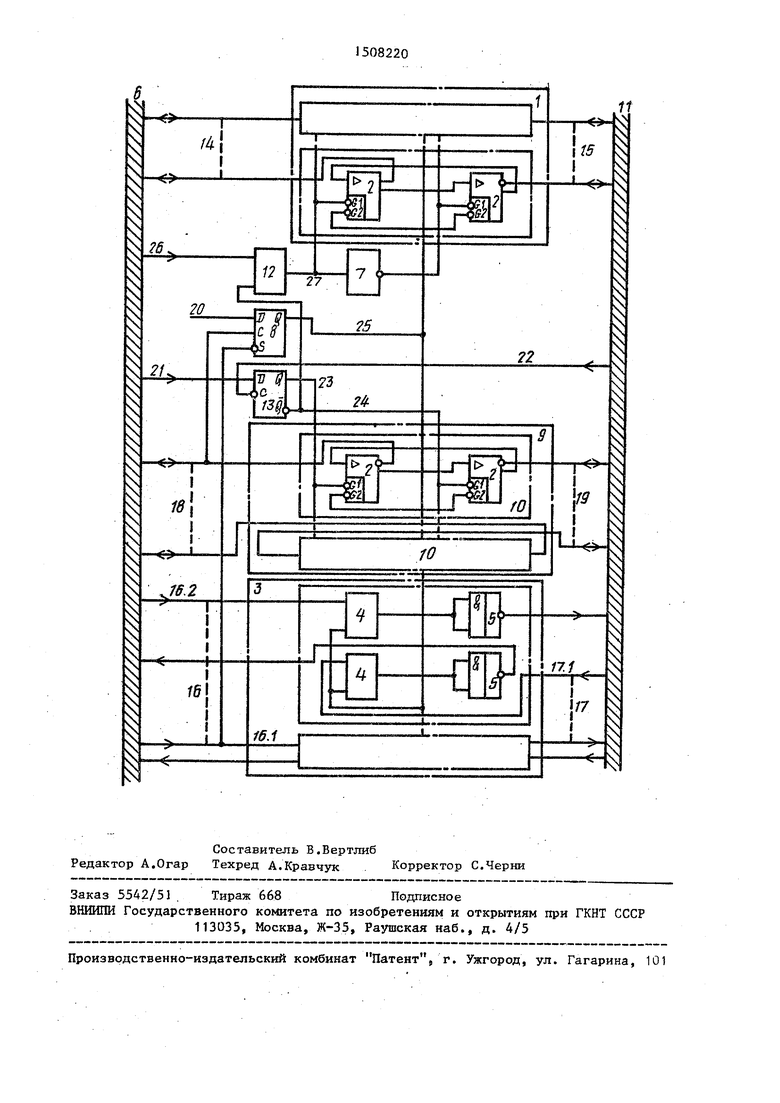

На чертеже представлена функциональная схема устройства.

Устройство содержит коммутатор 1 информационных сигналов, каждый элемент коммутации которого состоит из шинных формирователей 2,,узсш 3-усилителей з равляющих сигналов, состоящий из приемников 4 и передатчиков 5, магистраль 6 микроЭВМ, элемент

НЕ 7, триггер 8 управления, коммута - тор 9 управляющих сигналов, каждый элемент 10 коммутации которого сос- тоит из шинных формирователей 2, магистраль 11 периферийных устройств, элемент ИСКЛЮЧАК1 ЕЕ ИЛИ 12 и триггер 13 захвата магистрали.

На чертеже обозначены также двунаправленные линии (шины) 14 и 15 информационных сигналов, однонаправленные линии (шины) J6 и 17, проходящие -через узел 3 между магистралями 6 и 13, двунаправленные линии (шины) 18. и 19, коммутируемые коммутатором 9, вход 20 пуска устройства, линии 21 и 22 входов и линии 23 и 24 выходов триггера 13, линия 25 выхода триггера 8, линия (шины) 26 чтения данных маю

31508

гистрали б и линия 27 выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12.

Информационные входы приемников 4 подключены к выходным линиям Выбор устройства, Разрешение захвата магистрали, Разрешение прерывания, Установка магистрали 6 микроЭВМ и .выходным линиям Запрос магистрали, .Подтверждение запроса, 3anpqc пре- рыванйя, Прерывание по внешнему событию,.Авария источника питания, Останов, магистрали 11 периферийных устройств; выходы передатчиков 5 подключены к входным линиям Выбор уст- ройства, Разрешение захвата магистрали, Разрешение прерывания, Установка магистрали 11 периферийных устройств и входным линиям Запрос магистрали, Подтверждение за- проса, Запрос прерьгоания, Прерывание по внешнему событию, Авария источника питания, Останов магистрали 6 микроэвм.

Установочный вход и синхровход триггера 8 подключены к линиям Установка и Синхронизация обмена магистрали 6 микроэвм, а информационный вход триггера 8 - к линии 20 пуска устройства, причем шины 18 Синхрони- зация обмена, Чтение данных, Запись данных, Ответ устройства, Признак записи байта Регенерация магистрали 6 микроЭВМ подключены к одноименным шинам магистрали 11 пери- ферийных устройств через коммутатор 9

Информационный вход 21 и синхровхо 22 триггера 13 подключены к шине Разрешение запроса магистрали магистрали б микроэвм и шине Подтверж- дение запроса магистрали 11 периферийных устройств соответственно, прямой выход триггера 13 подключен к шине 26 Чтение данных магистрали 6 микроэвм,

Устройство работает следующим образом.

При работе периферийного устройства в программном р ежиме, т.е, когда на входе 20 пуска устройства установ- лен сигнал низкого уровня и на шине 21 Разрешение запроса магистрали магистрали 6 и шине 17 Подтверждение запроса магистрали П установлены сигналы высокого уровня, на прямом , и инверсном выходах триггера 13 присутствуют сигналы высокого и низкого уровней соответственно. Эти сигналы, поступая на входы направления передачи шинных формирователейi 2 коммутатора 9, разрешают прохождени сигналов по линиям 18 Синхронизация обмена, Чтение данных, Запись данных, Признак записи байта, Регенерация из магистрали 6 в магистраль 11, а сигнала Ответ устройства - в обратном направлении, мент ИСКЛЮ 1/ ЮЩЕЕ ИПИ 12 при этом работает как повторитель сигнала шины Чтение данных магистрали б, так как шинные формирователи 2 коммутатора 1 управляются только сигналом линии 26 Чтение данных, При работе периферийного устройства в режиме прямого доступа в памяти микроЭВМ периферийное устройство выра- батьшает в линии 17,1 Запрос магистрали сигнал, который, поступая затем обычным образом через соответствующий усилитель узла 3 в магистраль 6 микроэвм, приводит к выработке в линию 2 центральным процессором микроэвм сигнала Разрешение запроса магистрали. Этот сигнал сбрасывает триггер 13, устанавливая на прямом выходе триггера 13 сигнал низкого уровня. Устройство подготавливается для трансляции сигналов Синхронизация обмена, Чтение данных, Запись данных, Признак записи байта Регенерация из магистрали 11 периферийного устройства в магистраль 6 микроэвм, ,а сигнала Ответ устройства - в обратном направлении. Процесс подготовки длится до поступления по линии 22 сигнала Подтверждение запроса из магистрали 11 периферийных устройств, появление этого сигнала устанавливает триггер 13 на весь цикл прямого доступа к памяти микроэвм. Сигнал высокого уровня, поступающий с инверсного выхода триггера 13 на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12, переключает последний в режим инвертора, что позволяет управлять направлением передачи шинньрс формирователей 2 коммутатора 1 периферийному устройству, например, в цикле Чтение, организуемом периферийным устройством (режим ПДП), сигнал Чтениелданных, поступая в магистраль 6 ,микроэвм через шинные формирователи 2 коммутатора 9, приводит к появлению высокого уровня на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 и низкого уровня на выходе элемента НЕ- 7, В результате обеспечи51508220 .6

вается направление передачи сигналов маг истрали периферийных -устройств, Адрес - данные из магистрали 6 триггер управления, выход которого микроэвм в магистраль 1I периферий- соединен с разрешающими входами ком- ных устройств. По окончании магистраль, Утатора информационных сигналов и

. . чт/ тчо r rrT TirniST-Tri fr ттпп этзгт атлттт TiX / Т1 а гт

него цикла прямого доступа к памяти микроэвм, организованного периферийным устройством, последнее снимает с линии 22 сигнал Подтверждение запроса. Так как в линии 21 сигнал Раз- 10 решение запроса магистрали к этому моменту уже снят процессором микро- ЭВМ, на прямом и инверсном выходах триггера 13 устанавливаются сигналы высокого и низкого уровней соответ- 15 ственно, что приводит к переключению шинных формирователей 2 коммутатора 9 в начальное сос.тояние (т.е. соответствующее программному режиму раузла усилителей управляющих сигналов, а вход установки, синхровход и информационный вход являются соответствующими входами устройства для подключения к шинам установки и синхронизации обмена магистрали микроЭВМ и входу пуска устройства, отличаю щееся тем, что, с целью расшире ния функциональных возможностей устройства путем обеспечения режима пря мого доступа к памяти микроЭВМ, в нег введены коммутатор управляющих сигналов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и триггер захвата магистрали, причем перботы микроэвм, когда устройство управ-20 вая и вторая группы входов-выходов

ляется сигналом шины Чтение данных

магистрали микроЭВМ).

Форм у.л а изобретения

Устройство для сопряжения магистрали микроэвм с магистралью перифе- 25 рий.ных устройств, содержащее коммутатор информационных сигналов, первая и вторая группы информационных входов-, выходов которого являются соответствующими группами входов-выходов ЗО устройства для подключения к информа- цонным шинам магистралей микроЭВМ и перифе1 1Йных устройств, элемент НЕ, выход и вход которого соединены с

коммутатора управляющих сигналов явля ются соответствующими группами входов выходов устройства для подключения к управляющим шинам магистрали микро- ЭВМ и магистрали периферийных устройств, а первый и второй входы выбора направления,подключены соответственно к инверсному и прямому выходам триггера захвата магистрали, информапионный вход н синхровход которого,являются соответственно входами устройства для подключения к шине разрешения запроса магистрали микроэвм и шине подтверждения запромаг истрали периферийных -устройств, триггер управления, выход которого соединен с разрешающими входами ком- Утатора информационных сигналов и

чт/ тчо r rrT TirniST-Tri fr ттпп этзгт атлттт TiX / Т1 а гт

узла усилителей управляющих сигналов, а вход установки, синхровход и информационный вход являются соответствующими входами устройства для подключения к шинам установки и синхронизации обмена магистрали микроЭВМ и входу пуска устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения режима прямого доступа к памяти микроЭВМ, в него введены коммутатор управляющих сигналов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и триггер захвата магистрали, причем первая и вторая группы входов-выходов

коммутатора управляющих сигналов являются соответствующими группами входов выходов устройства для подключения к управляющим шинам магистрали микро- ЭВМ и магистрали периферийных устройств, а первый и второй входы выбора направления,подключены соответственно к инверсному и прямому выходам триггера захвата магистрали, информапионный вход н синхровход которого,являются соответственно входами устройства для подключения к шине разрешения запроса магистрали микроэвм и шине подтверждения запро

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств | 1990 |

|

SU1784985A1 |

| Устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств | 1986 |

|

SU1367018A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения электронной вычислительной машины с общей магистралью | 1987 |

|

SU1411765A1 |

| Устройство для сопряжения вычислительного модуля с магистралью | 1985 |

|

SU1325495A1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство для согласования системных магистралей | 1989 |

|

SU1674143A1 |

Изобретение относится к цифровой вычислительной технике, непосредственно к устройствам для передачи информации в магистрали микроЭВМ. Преимущественная область использования - создание мультипроцессорных систем и сетей ЭВМ на базе микроЭВМ с магистральным параллельным интерфейсом. Целью изобретения является расширение функциональных возможностей устройства путем обеспечения режима прямого доступа к памяти микроЭВМ. Для этого в устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств, содержащее коммутатор информационных сигналов, узел усилителей управляющих сигналов, элемент НЕ и триггер управления, введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, коммутатор управляющих сигналов и триггер захвата магистрали. 1 ил.

пёрвым и вторым входами выбора направ-,- са магистрали периферийных устройств.

ления коммута тора информационных сигналов, узел усилителей управляющих сигналов, первые и вторые группы входов и выходов являются соответствующи- -,ъм группами входов и выходов устрой- ства для подключения к грзпппам входных и выхрдных шин магистрали микро- ЭВМ и группам выходных и входных шин

40

первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является входом устройства для подключения к шине чтения данных магистрали микроэвм, инверсный выход триггера захвата магистрали соединен с вторым входом элемента ИСКЛЮЧАКЖЩЕ ИЛИ, выходом соединенного с входом элемента НЕ,

первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является входом устройства для подключения к шине чтения данных магистрали микроэвм, инверсный выход триггера захвата магистрали соединен с вторым входом элемента ИСКЛЮЧАКЖЩЕ ИЛИ, выходом соединенного с входом элемента НЕ,

| Приборы и техника эксперимента, 1983, № 2, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Авторское свидетельство СССР по заявке № 4029794, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-15—Публикация

1988-01-13—Подача