N со со

4

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам ЭВМ.и предназначено преимущественно для использования в составе вычислительной машины коллективного пользования.

Цель изобретения - расширение области применения устройства путем обеспечения возможности обращения к памяти несколькими пгльзователями.

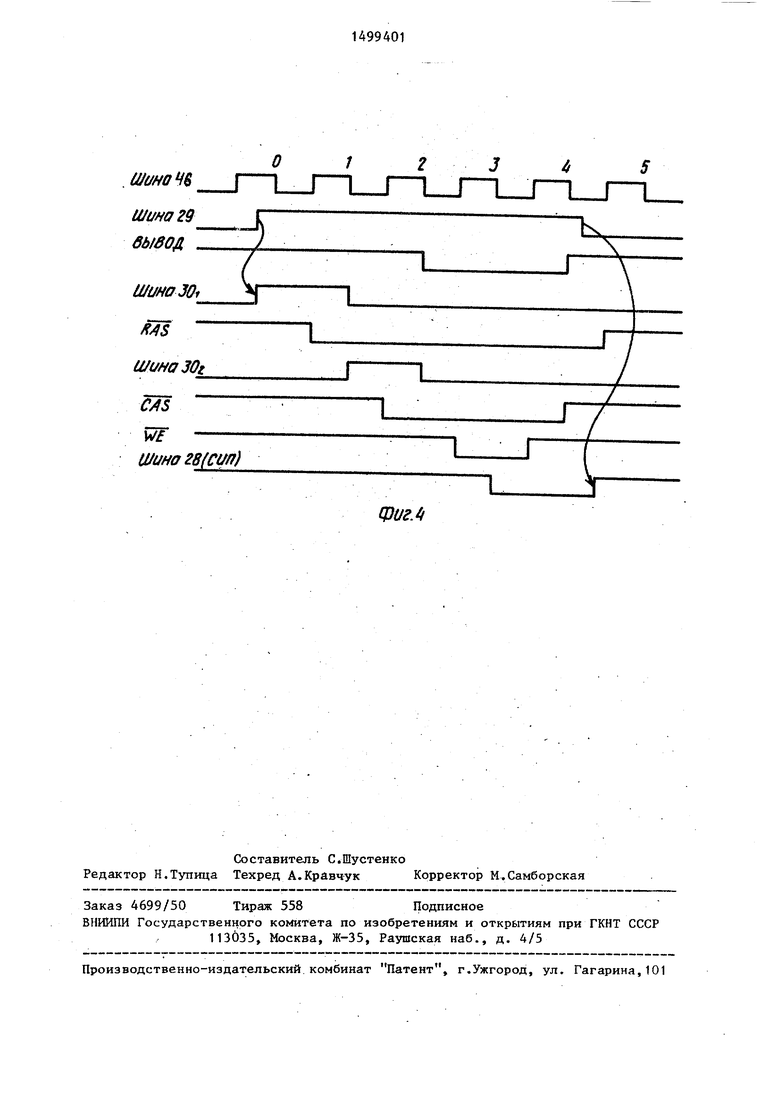

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема дешифратора адреса; на фиг. 3 - функциональная , схема блока управления; на фиг. 4 - временная диаграмма работы устройства.

Пример конкретной реализации устройства приводится применительно к требованиям ОСТа для междумодульного параллельного интерфейса (МПЙ), который используестя в ЭВМ типа Электроника-60. Кроме того, регист разделения имеет 4 разряда (примени- ргельно к вычислительной системе для 16 пользователей).

Устройство содержит (фиг. 1) матрицу блоков 1 оперативной памяти, в состав которой входит 41 блоков па мяти динамического типа, где i для конкретного примера, в зависимости о использования конкретной микросхемы, приведены в таблице.

|К565 РУЗр

К565 РУЗ,РУ6 К565 РУ5 К565 РУ7

32

Кроме того, устройство содержит регистр 2 адреса, состоящ51Й из регистра 2, младших разрядов адреса и регистра 2 ,, старших разрядов адреса, блок З управления, дешифратор 4 адреса, регистр 5 адреса регенерации, регистр 6 кода разделения памяти, блок 7 коммутации, который в простейшем случае представляет собой медные штыри, закрепленные на печатной плате, а комщ тация осуществляется путем накрутки проводника на соответствующие штыри, счетчик 8 адресов регенерации магистральные приемопередатчики 9, соответственно старшегб и младшего байтов, магистральные приемник 10 и передатчик 11, информационные выходы 12 и 13 соответственно старшего и

0 5

0

5

0

0

младшего байтов блс1ков 1 оперативной памяти, адресные входы 14, информационные входы 15 и 16 соответственно младшего и старшего байтов блоков 1 оперативной памяти, входы 17 и 18 стробирования адресов строк блоков

1(RAS1 и RAS2), вход 19 разрешения записи блоков 1 (WE), входы 20 (CAS) стробирования адресов столбцов блоков 1, выходы 21 регистра Б, счетный вход 22 счетчика 8 адресов регенерации, вход 23 активной синхронизации устройства (сил), вход 24 регенерации (РГН), выход 25 дешифратора 4 адреса, вход 26 управления магистральных приемопередатчиков 9, входы 27 управления регистров адреса 2 и регенерации 5, выход 28 пассивной синхронизации устройства (сип), межмодульный параллельный интерфейс (МПИ) 29 группу шин 30 адреса данных МПИ, группу управляющих шин 31 и 32 МПИ, входы 33 блока 3 управления, групповую линию связи управляющих шин МПИ 29 с

блоком управления, вход 34 младшего разряда адреса блока 3 управления.

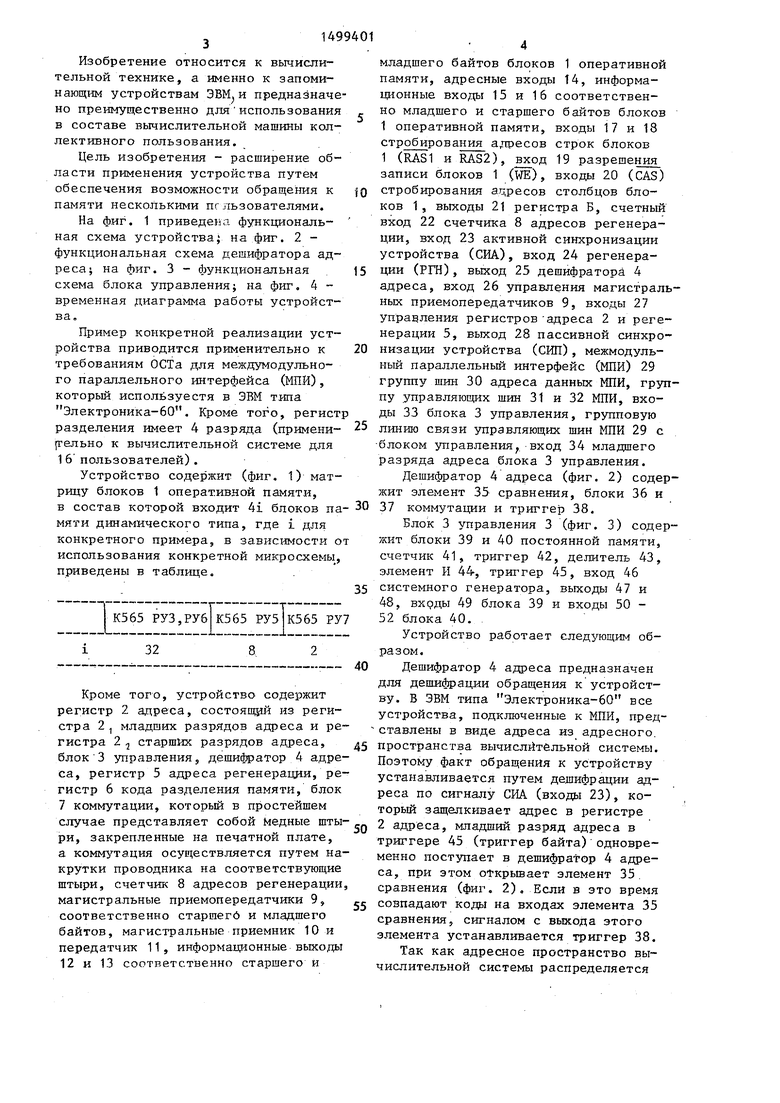

Дешифратор 4 адреса (фиг. 2) содержит элемент 35 сравнения, блоки 36 и 37 коммутации и триггер 38.

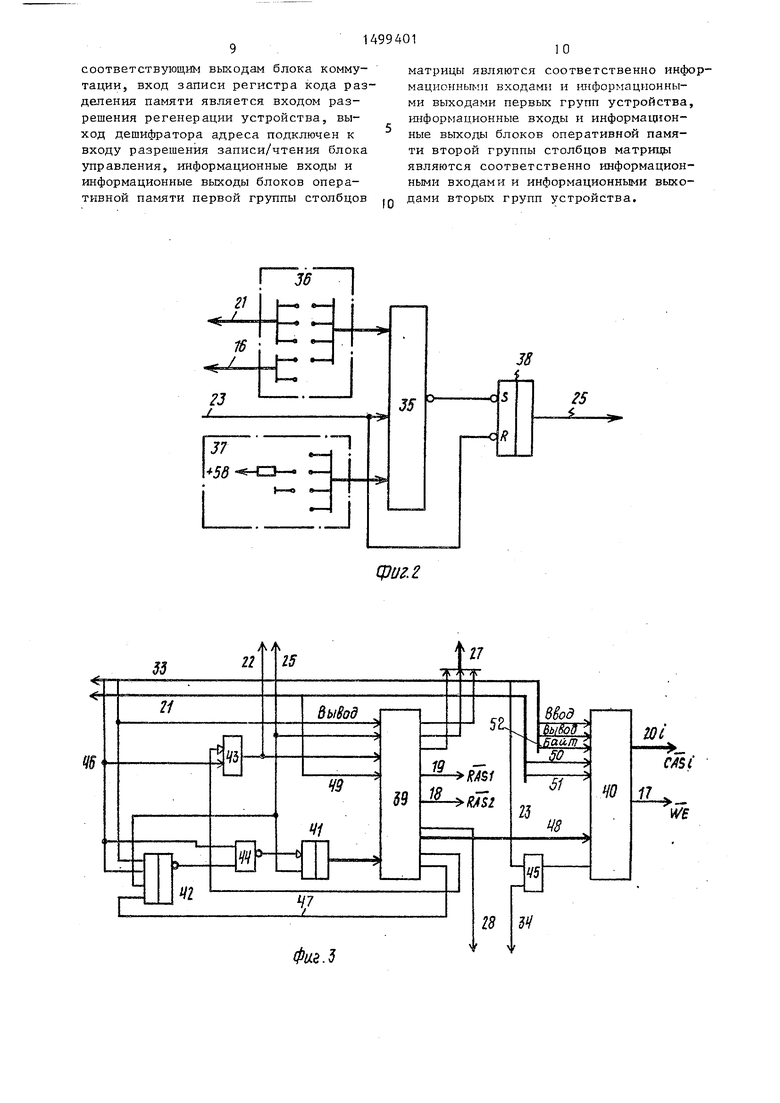

Блок 3 управления 3 (фиг. 3) содержит блоки 39 и 40 постоянной памяти, счетчик 41, триггер 42, делитель 43, элемент И 44, триггер 45, вход 46 системного генератора, выходы 47 и 48, входы 49 блока 39 и входы 50 - 52 блока 40.

Устройство работает следующим образом.

Дешифратор 4 адреса предназначен для дешифрации обращения к устройству. В ЭВМ типа Электроника-60 все устройства, подключенные к МПИ, пред- ставлены в виде адреса из адресного, пространства вычислительной системы. Поэтому факт обращения к устройству устанавливается путем дешифрации адреса по сигналу СНА (входы 23), который защелкивает адрес в регистре

2адреса, младший разряд адреса в триггере 45 (триггер байта) одновременно поступает в дешифратор 4 адреса, при этом открьшает элемент 35. сравнения (фиг, 2), Если в это время совпадают коды на входах элемента 35 сравнения, сигналом с выхода этого элемента устанавливается триггер 38.

Так как адресное пространство вычислительной системы распределяется

между ОЗУ, ПЗУ и внешними устройствами, то ОЗУ могут быть отведены различные области в пределах адресного пространства. Лпя настройки к отведенной области памяти дешифратор 4 адреса содержит два блока 36 и 37 комутации. Первый блок 36 предназначен для коммутации дешифрируемых разрядо адресного слова, которые подведены по линиям 16 и 21, так как адресное слово в устройстве образуется добавлением к адресным разрядам с МПИ 29 разрядов регистра 6 кода разделения памяти (в данном примере максимальная разрядность адресного слова составляет ) . Второй блок 37 предназначен для задания номера банка памяти, т.е. установленной области памяти.

Таким образом, если устройство выбрано, т.е. поступил в устройство запрос с МПИ 29, то по шине 25 сигнал выбора устройства поступает в блок 3 управления. При этом открывается (фиг. 3) счетчик 41 и триггер 42. По очередному отрицательному срезу сигнала системного генератора на входе 46 установится триггер 42, который открьгаает элемент И 44,и при последующих сигналах системного генератора счетчик 41 начинает перебирать адреса блока 39, на выходах которого формируются управляющие сиг

инициируется системой синхронизации вычислительной системы. По содержанию код, загружаемый в регистр 6, на каждом цикле увеличивается на единицу так, что изменение состояний младшего разряда регистра 6 разделения имеет вид меандра, причем период меандра должен быть не более 4 мс. Следовательно, каждая строка накопителей в матрице активизируется в течение 2 мс и после этого переходит в пассивный режим, т.е. в режим регенерации, а другая строка накопителей

5 матрицы будет в обратной фазе повторять режим первой строки.

Рассмотрим работу устройства на примере канального цикла ВЫВОД (запись в ОЗУ). Допустим, что вход 49 (младший разряд регистра 6) имеет низкий уровень, следовательно, верх- ние блоки 1 в активном режиме, а нижние блоки 1 в режиме регенерации. С приходом сигнала по входу 25 (с де5 шифратора 4 адреса) блок 39 формирует код на выходах 27, по которому выход регистра 5 адресов регенерации переходит в третье состояние, а выход регистра 2 переходит в активный режим (фиг. 4). При переходе счетчика 41 развертки в состояние 1g формируется сигнал RAS1, который стробирует адрес строки в блоках 1 , (верхняя строка). На следующем такте счетчика

0

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Формирователь символов для устройств отображения информации на матричных экранах | 1989 |

|

SU1688280A1 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для ранжирования чисел | 2022 |

|

RU2792182C1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1381584A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам ЭВМ, предназначено преимущественно для использования в составе вычислительной машины коллективного пользования. Цель изобретения - расширение области применения устройства за счет возможности обращения к памяти несколькими пользователями. Устройство содержит матрицу 1 блоков оперативной памяти, в состав которой входят 4 I блоков памяти, регистр 2 адреса, состоящий из регистра 21 младших разрядов адреса и регистра 22 старших разрядов адреса, блок 3 управления, дешифратор 4 адреса, регистр 5 адреса регенерации, регистр 6 кода разделения памяти, блок 7 коммутации с соответствующими функциональными связями. 4 ил., 1 табл.

налы. Содержание управляющих сигналов 35 блок 39 на выходах 27 формирует определяется по состоянию входов 33 и новый код, который запирает регистр 21.

Выбор блока 1 осуществляется путем возбуждения одной из шин RAS 1,2 и.

2j и открывает регистр Z, т.е. на входах 14 устанавливает следующую группу адресных разрядов, которая с

по крайней мере, одной из шин CASi. Выбор одной из шин RAS 1 ,2 определяет состояние входа 49, по которому на вход блока 39 постоянной памяти поступает сигнал младшего разряда регистра 6.

Выбор одного из выходов 20 (сигнал CAS) осуществляется посредством дешифрации состояний входов 50-52 и выхода триггера 45. На входы 5(0 и 51 блока 40 постоянной памяти поступают состояния двух разрядов регистра 6, а совокупность состояний входов шин 52 и триггера 45 определяет выбор одного или двух байтов.

Таким образом, координата активного блока оперативной памяти в ос- новном определяется состоянием регистра 6. Последний загружается с МПИ 29 по сигналу регенерации, который

блок 39 на выходах 27 формирует новый код, который запирает регистр

2j и открывает регистр Z, т.е. на входах 14 устанавливает следующую группу адресных разрядов, которая с

увеличением счетчика 41.еще на единицу стробируется сигналом CASi в блоке 1 . На следующем такте регистр 2 .запирается и открывается регистр 5 адресов регенерации, при зтом изменение состояния входов 14 адресов для выбранного блока 1 не имеет значения.

На следующем такте счетчика 41, если нет сигнала направления передачи данных, в данном примере сигнал Вывод, который поступает на входы 33, то блок 39 формирует на выходе 47 сигнал, который переключает триггер 42. Следовательно, элемент И 44

запирается и дальнейшая развертка счетчика 41 приостанавливается. С приходом сигнала Вывод триггер 42 снова устанавливается и счетчик 41 переходит в следлтощее состояние, при

котором инициируется сигнал записи WE. Данные принимаются в блок 1 оперативной памяти и на последующих тактах формируется сигнал пассивной синхронизации устройства (СИП), послед ова.тельно снимаются -сигналы WE, CASi, RAS1. Канальный цикл завершается снятием сигнала СИЛ, которьй открывает регистр 2 адреса по входу и очищает триггер 38.

Рассмотрим процедуру регенерации по одному адресу, Стробирование адресов в блоках 1 оперативной памяти

осуществляется по срезу сигналов RAS и CAS, поэтому на входах 14 адресов требуемый адрес должен быть установлен к моменту прихода среза этих сигналов в накопитель ОЗУ, При регенерации стробирзпотся- только адреса по сиг налу RAC.

Признаком формирования сигнала RAS для регенерации является нулевое состояние выхода делителя 43, Сигнал (так как в данном случае нижняя строка- группы блоков 1 находится в пассивном режиме) формируется синхронно с переходом вькода делителя 43 из единичного состояния в нулевое ив дальнейше1у, копирует длительность сигнала делителя 43-. При переходе делителя 43 с низкого на высокий уровень сигнал RAS2 тоже восстанавливается j а на входе 22 фронт сигнала наращивает на единицу счетчик 8 адресов регенерации,-И так процедура периоди чески повторяется.

Когда одновременно поступают требования на канальный цикл и регенера цшо очередного адреса, в любом случа если при активизации триггера 38 делитель 43 в нулевом состоянии, блок 39 формирует сигнал очистки делителя 43 и одновременно сигнал RAS2 переводит на пассивный уровень, формируя этот сигнал одновременно с переключением регистра 5 адресов регенерации. Таким образом, регенерация пассивной части памяти не ухудшает, реакции устройства на канальные запрос

Формула изобретения

Динамическое оперативное запоминающее устройство, содержащее матрицу блоков оперативной памяти, регистр адреса, счетчик адресов регенерации, дешифратор адреса, блок управления, причем адресные входы блоков опера-

0

jд

5 о

. дс

35

0

тивной памяти матрицы подключены к выходам регистра адресов, входы режима блоков оперативной памяти матрицы подключены к соответствующему выходу блока управления, входы стро- бирования адресов строк блоков памяти каждой строки матрицы подключены к соответствующим выходам блока управления, входы стробирования адресов столбцов блоков памяти каждого столбца матрицы подключены к соот-- ветствующим выходам блока управления, информационные входы первой и второй групп регистра адреса являются адресными входами соответствующих групп устройства, вход записи регистра адреса подключен к входу активной синхронизации блока управления и является одноименным входом устройства, счетный вход счетчика регенерации подключен к соответствующему выходу блока управления, входы первой группы дешифратора адреса подключены к информационным входам второй группы регистра адреса первый и второй входы активации регистра адреса подключены к соответствующим выходам блока управления, выход пассивной синхро- . визации блока управления является одноименным выходом устройства, о т - лич ающее ся тем, что, с целью расширения области применения устройства путем обеспечения возможности обращения к памяти несколькими пользователями, оно содержит регистр кода разделения памяти, блок коммутации и регистр адресов, регенерации, выходы и информационные входы которого подключены соответственно к адресным входам блоков.оперативной памяти матрицы и к выходам счетчика адресов регенерации, вход активации регистра адресов регенерации подключен к соответств-ующему выходу блока управления, информационные входы второй грухты дешифратора адреса подклю-. чены к информационным входам первой группы блока коммутации, к входу з.а- дания режима блока управления и к выходам регистра кода разделения памяти, информационные входы которого подключены к информационным входам первой группы регистра адреса, информационные входы второй группы блока {коммутации подключены к информационным входам второй группы блока регистра адреса, первый и второй входы раз- решёйия записи которого подключены к

cooTBeTCTByioni,iiNi выходам блока коммутации, вход записи регистра кода разделения памяти является входом разрешения регенерации устройства, выход дешифратора адреса подключен к входу разрешения записи/чтения блока управления, ршформационные входы и информационные выходы блоков оперативной памяти первой группы столбцов

з б I

матрицы являются соответственно инфор- мационньп и входами и информационными выходами первых групп устройства, информационные входы и информационные выходы блоков оперативной памяти второй группы столбцов матрицы являются соответственно информационными входами и информационными выходами вторых групп устройства.

03иг.2

ШоноЧ

Шина 29 вывод .

ШиноЗ(}1 Ш

Шина 30t

Шиног8(сип)

Ъ.

Л

фиг. ft

| Авторское свидетельство СССР № 1177820, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Полупроводниковые запоминающие устройства и их применение | |||

| /Под ред | |||

| А.Ю.Гордонова, М.: Радио и связь, 1981, с | |||

| Халат для профессиональных целей | 1918 |

|

SU134A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-07—Публикация

1987-03-25—Подача