..LJ

Изобретение относится к вычислительной технике и может быть использовано в качестве ячейки базового кристалла для реализации произвольной функции одного трехзначного аргумента.

Целью изобретения является упрощение элемента и расширение его функциональных возможностей.

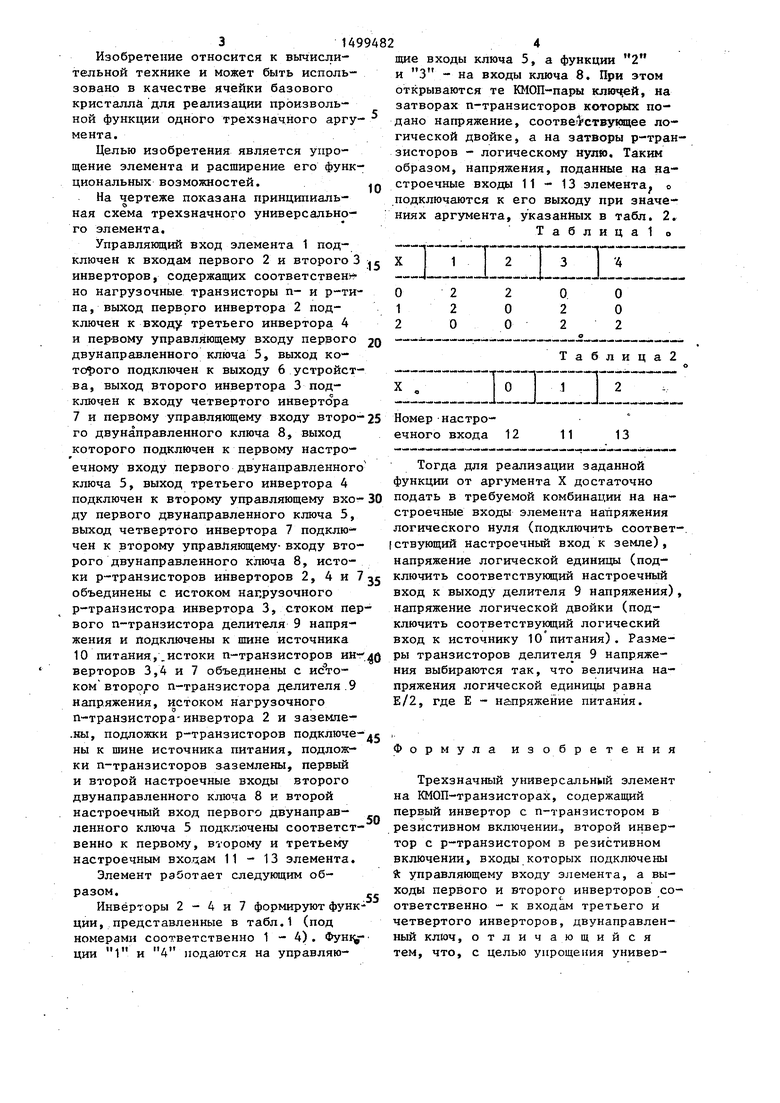

На чертеже показана принципиальная схема трехзначного универсального элемента.

Управляющий вход элемента 1 подключен к входам первого 2 и второго 3 инверторов, содержащих соответствен - но нагрузочные транзисторы п- и р-ти- па, выход первого инвертора 2 подключен к входу третьего инвертора 4 и первому управляющему входу первого двунаправленного ключа 5, выход которого подключен к выходу 6 устройства, выход второго инвертора 3 подключен к входу четвертого инвертора 7 и первому управляющему входу второго двунаправленного ключа 8, выход которого подключен к первому настрог

ечному входу первого двунаправленного ключа 5, выход третьего инвертора 4 подключен к второму управляющему входу первого двунаправленного ключа 5, выход четвертого инвертора 7 подключен к второму управляющему- входу второго двунаправленного ключа 8, истоки р-транзисторов инверторов 2, 4 и 7 объединены с истоком нагрузочного р-транзистора инвертора 3, стоком пер вого п-транзистора делителя 9 напряжения и подключены к шине источника 10 питания,.истоки п-транзисторов инверторов 3,4 и 7 объединены с ком второ го п-транзистора делителя.9 напряжения, истоком нагрузочного п-транзистора-инвертора 2 и заземпе- .ны, подложки р-транзисторов подключены к шине источника питания, подложки п-транзисторов заземлены, первый и второй настроечные входы второго двунаправленного ключа 8 и второй настроечный вход первого двунаправленного ключа 5 подключены соответственно к первому, второму и третьему настроечным входам 11 - 13 элемента.

Элемент работает следующим образом.

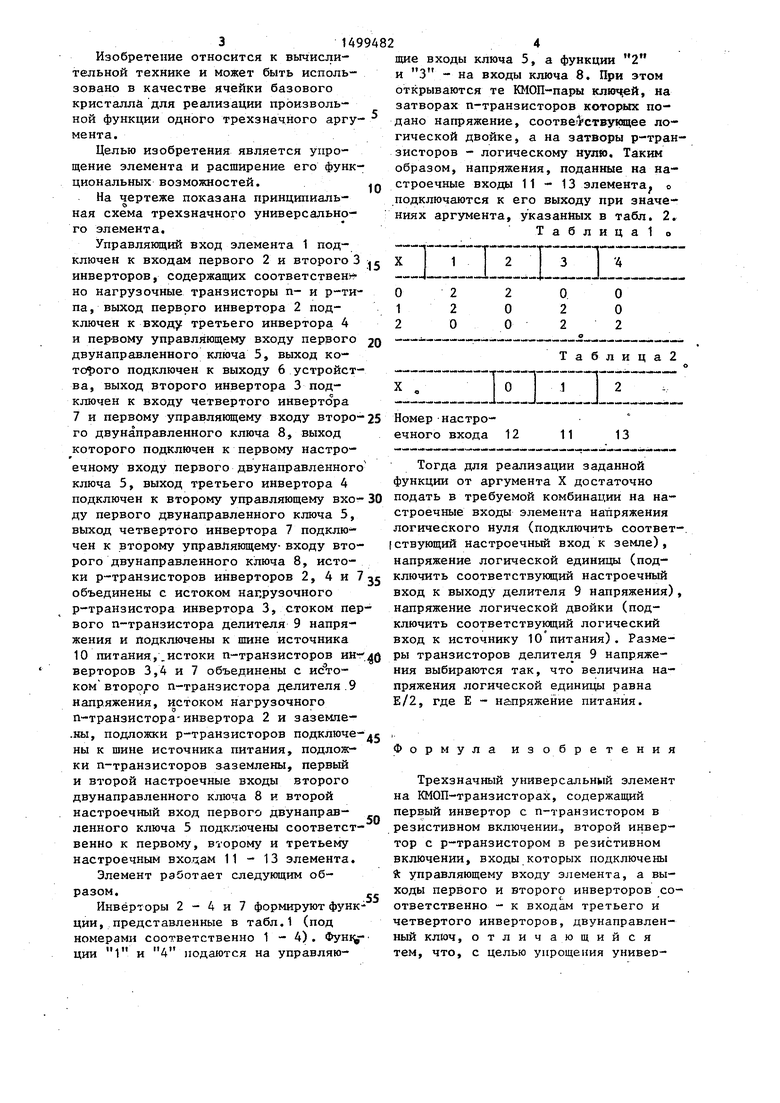

Инверторы 2 - 4 и 7 формируют функции, представленные в табл.1 (под номерами соответственно 1 - 4) . ции 1 и 4 подаются на управляю

0

s

tfoH

щие входы ключа 5, а функции 2 и 3 - на входы ключа 8. При этом открываются те КМОП-пары ключей, на затворах п-транзисторов которых подано напряжение, соотве ству1сядее логической двойке, а на затворы р-транзисторов - логическому нулю. Таким образом, напряжения, поданные на настроечные входы 11-13 злeмeнтa о подключаются к его выходу при значениях аргумента, указанных в табл. 2. Таблица1 о

iziizm

Номер настроечного входа 12

11

13

Тогда для реализации заданной функции от аргумента X достаточно подать в требуемой комбинации на настроечные входы элемента напряжения логического нуля (подключить соответ-. ствующий настроечный вход к земле), напряжение логической единицы (подключить соответствующий настроечный вход к выходу делителя 9 напряжения), напряжение логической двойки (подключить соответствукяций логический вход к источнику 10 питания). Размеры транзисторов делителя 9 напряжения выбираются так, что величина напряжения логической единицы равна Е/2, где Е - напряжение питания.

Формула изобретения

Трехзначный универсальный элемент на КМОП-транзисторах, содержащий первый инвертор с п-транзистором в резистивном включении., второй инвертор с р-транзистором в резистивном включении, входы которых подключены ft управляющему входу элемента, а выходы первого и второго инверторов соответственно - к входам третьего и четвертого инверторов, двунаправленный ключ, отличающийся тем, что, с целью упрощения унивео-

514994826

сального элемента и расширения функ- кого ключа, вызгод четвертого инвертоциональных возможностей, введены де-, ра подключен к второму управляющему литель напряжения, содержащий два п- входу второго двунаправленного ключа,

транзистора в резистивном включении,- выход которого подключен к первому и второй двунаправленный ключ, при настроёчнда|у входу первого двунаправ- этом выход первого инвертора подклю- ленного ключа, выход которого подключен к первому управляющему входу пер- чен к выходу элемента, второй на- вого двунаправленного ключа, выход строечшлй вход первого двунаправлентретьего инвертора подключен к вто-ю ного ключа, первый и второй настроеч- рому управляющему входу первого дву- ные входы второго двунаправленного

направленного ключа, выход второго ключа подключены соответственно к инвертора подключен к первому управ- первому, второму и третьему настроеч- лякяцему входу второго двунаправлен- ным входам элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| М-ЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1994 |

|

RU2079970C1 |

| Сумматор | 1983 |

|

SU1101863A1 |

| Многофункциональный логический элемент | 1980 |

|

SU898618A1 |

| Элементы однородной вычислительной структуры | 1980 |

|

SU930677A1 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ | 2014 |

|

RU2546302C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| КОМПЛЕМЕНТАРНЫЙ МИКРОЭЛЕКТРОМЕХАНИЧЕСКИЙ ИНВЕРТОР | 2005 |

|

RU2290753C1 |

| Регистр сдвига на МДП-транзисторах | 1985 |

|

SU1269210A1 |

| @ -Значный инвертор | 1982 |

|

SU1097162A1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ УРОВНЕЙ ЛОГИЧЕСКИХ СИГНАЛОВ НА КМОП-ТРАНЗИСТОРАХ | 1993 |

|

RU2085030C1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве ячейки базового кристалла для реализации произвольной функции одного трехзначного аргумента. Целью изобретения является упрощение элемента и расширение его функциональных возможностей. Устройство содержит управляющий вход 1, первый 2, второй 3, третий 4 и четвертый 7 инверторы, первый 5 и второй 8 двунаправленные ключи и делитель 9 напряжения. Поставленная цель достигается за счет последовательного соединения двунаправленных ключей 5 и 8 в блоке коммутации, на управляющие входы которых подаются фиксированные функции многозначного аргумента, и использования делителя 9 напряжения для формирования напряжения логической единицы. 1 ил.

| Int | |||

| J | |||

| of Electronics, 1982, V | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Переставная шейка для вала | 1921 |

|

SU309A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-08-07—Публикация

1987-12-21—Подача