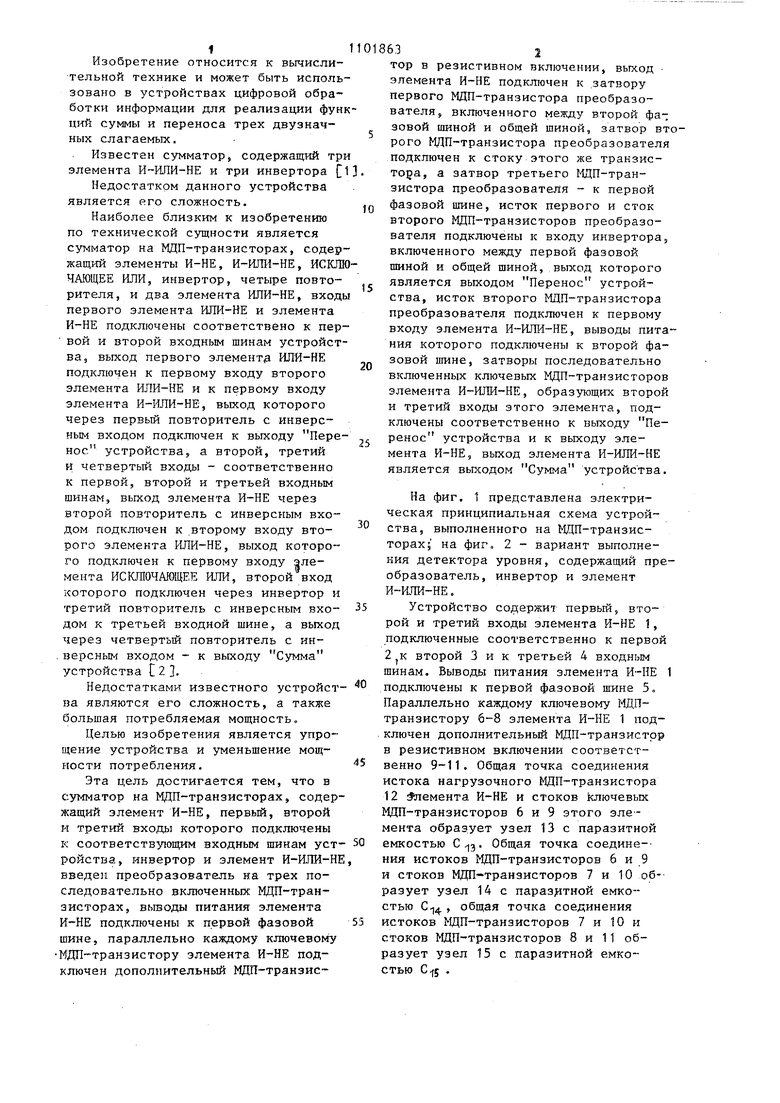

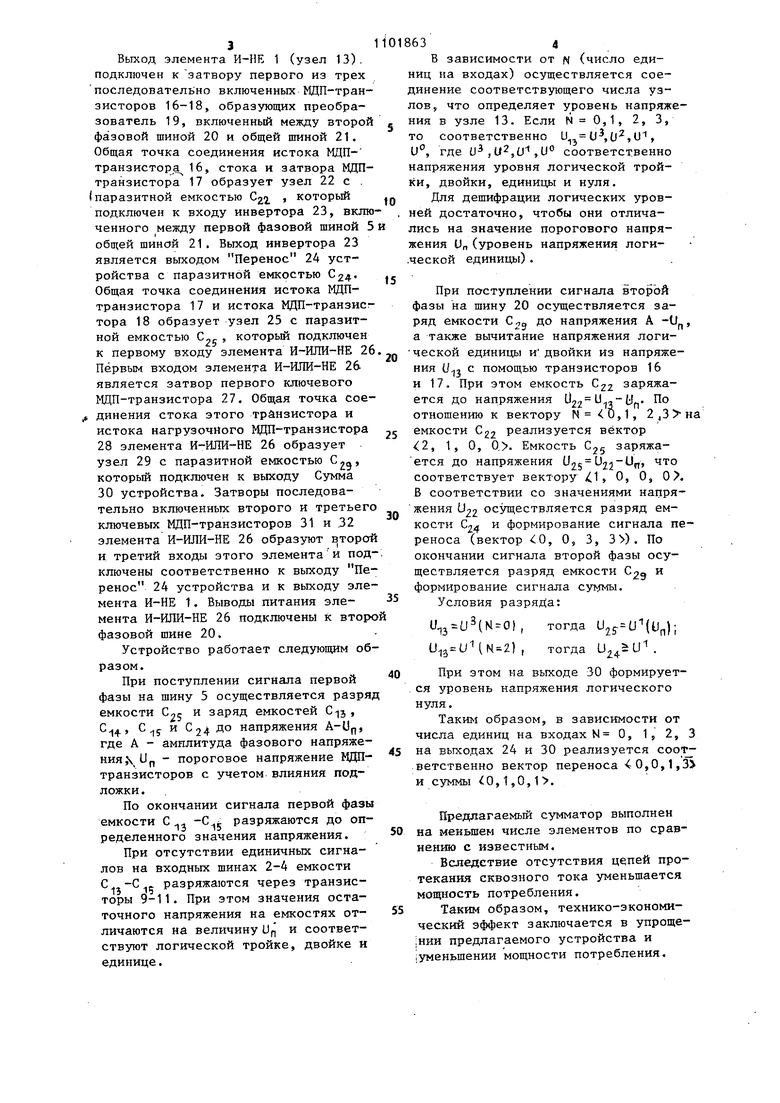

Изобретение относится к вычислительной технике и может быть исполь зовано в устройствах цифровой обработки информации для реализации фун ций суммы и переноса трех двузначных слагаемых. Известен сумматор, содержащий тр элемента И-ИЛИ-НЕ и три инвертора J Недостатком данного устройства является его сложность. Наиболее близким к изобретению по технической сущности является сумматор на МДП-транзисторах, содер жащий элементы И-НЕ, И-ИЛИ-НЕ, ИСКЛ ЧАЮЩЕЕ ИЛИ, инвертор, четыре повторителя, и два элемента ИЛИ-НЕ, вход первого элемента ИЛИ-НЕ и элемента И-НЕ подключены соответствено к пер вой и второй входным шинам устройст ва, выход первого элементд ИЛИ-НЕ подключен к первому входу второго элемента ИЛИ-НЕ и к первому входу элемента И-ИЛИ-НЕ, выход которого через первый повторитель с инверсным входом подключен к выходу Пере нос устройства, а второй, третий и четвертый входы - соответственно к первой, второй и третьей входным шинам, выход элемента И-НЕ через второй повторитель с инверсным входом подключен к второму входу второго элемента ИЛИ-НЕ, выход которого подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен через инвертор и третий повторитель с инверсным входом к третьей входной шине, а выход через четвертый повторитель с ин. версным входом - к выходу Сумма устройства С 2, Недостатками известного устройст ва являются его сложность, а также большая потребляемая мощность. Целью изобретения является упрощение устройства и уменьшение мощности потребления. Эта цель достигается тем, что в сумматор на МДП-транзисторах, содер жащий элемент И-НЕ, первый, второй и третий входы которого подключены к соответствующим входным шинам уст ройства, инвертор и элемент И-ИЛИ-Н введен преобразователь на трех последовательно включенных МДП-транзисторах, выводы питания элемента подключены к первой фазовой шине, параллельно каждому ключевому МДП-транзистору элемента И-НЕ подключен дополнительный МДП-транзис63тор в резистивном включении, выход элемента И-НЕ подключен к затвору первого МДП-транзистора преобразователя, включенного между второй фазовой шиной и общей шиной, затвор второго МДП-транзистора преобразователя подключен к стоку этого же транзистора, а затвор третьего МДП-транэистора преобразователя - к первой фазовой шине, исток первого и сток второго МДП транзисторов преобразователя подключены к входу инвертора включенного между первой фазовой шиной и общей шиной, выход которого является выходом Перенос устройства, исток второго МДП-транзистора преобразователя подключен к первому входу элемента И-ИЛИ-НЕ, выводы питания которого подключены к второй фазовой шине, затворы последовательно включенных ключевых МДП-транзисторов элемента И-ИЛИ-НЕ, образующих второй и третий входы этого элемента, подключены соответственно к выходу Перенос устройства и к выходу элемента И-НЕ, выход элемента И-ИЛИ-НЕ является вьпсодом Сумма устройства. На фиг. 1 представлена электрическая принципиальная схема устройства, выполненного на КЦП-транзисторах; на фиг, 2 - вариант выполнения детектора уровня, содержащий преобразователь, инвертор и элемент И-ИЖ-НЕ. Устройство содержит первый, второй и третий входы элемента И-НЕ 1, подключенные соответственно к первой 2 к второй 3 и к третьей 4 входным шинам. Выводы питания элемента И-НЕ 1 подключены к первой фазовой шине 5 Параллельно каждому ключевому ЩПтранзистору 6-8 элемента И-НЕ 1 подключен дополнительный МДП-транзистрр в резистивном включении соответственно 9-11. Общая точка соединения истока нагрузочного МДП-транзистора 12 5иемента И-НЕ и стоков ключевых МДП-транзисторов 6 и 9 этого элемента образует узел 13 с паразитной емкостью С ,|з. Общая точка соедине-ния истоков МДП-транзисторов 6 и 9 и стоков МДП-транзисторов 7 и 10 образует узел 14 с параз 1тной емкостью С 4 общая точка соединения истоков МДП-транзисторов 7 и 10 и стоков МДП-транзисторов 8 и 11 образует узел 15 с паразитной емкостью C-f5 . 3 Выход элемента И-НЕ 1 (узел 13). подключен к затвору первого из трех последовательно включенных МДП-транзисторов 16-18, образующих преобразователь 19, включенный между второй фазовой шиной 20 и общей шиной 21, Общая точка соединения истока МДПтранзистора 16, стока и затвора ЩЩтранзистора 17 образует узел 22 с . (паразитной емкостью , который подключен к входу инвертора 23, вклю ченного между первой фазовой шиной общей шиной 21 . Выход инвертора 23 является выходом Перенос 24 устройства с паразитной емкостью С24Общая точка соединения истока МДПтранзистора 17 и истока МДП-транзис тора 18 образует узел 25 с паразитной емкостью который подключен к первому вкоду элемента И-ИЛИ-НЕ 2 Первым входом элемента И-ИЛИ-НЕ 26 является затвор первого ключевого МДП-транзистора 27. Общая точка сое f. динения стока этого транзистора и истока нагрузочного ВДП-транзистора 28 элемента И-ИЛИ-НЕ 26 образует узел 29 с паразитной емкостью С.-, который подключен к выходу Сумма 30 устройства. Затворы последовательно включенных второго и третьег ключевых МДП-транзисторов 31 и .32 элемента И-ИЛИ-НЕ 26 образуют второ и третий входы этого элементами под ключены соответственно к выходу Пе ренос 24 устройства и к выходу эле мента И-НЕ 1. Выводы питания элемента И-ИЛИ-НЕ 26 подключены к втор фазовой шине 20, Устройство работает следующим об разом. При поступлении сигнала первой фазы на шину 5 осуществляется разря емкости С2 и заряд емкостей , 1 С 24 ДО напряжения A-Up, где А - амплитуда фазового напряжения ; Up - пороговое напряжение МДПтранзисторов с учетом влияния подложки . По окончании сигнала первой фазы емкости С разряжаются до определенного значения напряжения. При отсутствии единичных сигналов на входных шинах 2-4 емкости С -С разряжаются через транзисторы 9-11. При этом значения остаточного напряжения на емкостях отличаются на величину 1) и соответствуют логической тройке, двойке и единице. 634 В зависимости от N (число едииц на входах) осуществляется соеинение соответствующего числа узов, что определяет уровень напряжеия в узле 13. Если N 0,1, 2, 3, о соответственно U U, (J,U, и, где и,и,и,и° соответственно апряжения уровня логической тройи, двойки, единищ 1 и нуля. Для дешифрации логических уровей достаточно, чтобы они отличаись на значение порогового напряения Un(уровень напряжения логиеской единицы) , При поступлении сигнала второй фазы на шину 20 осуществляется заряд емкости С23 до напряжения А -U, а также вычитание напряжения логической единицы и двойки из напряжения и с помощью транзисторов 16 и 17, При этом емкость С22 заряжается до напряжения отношению к вектору N 0,1, емкости €22 реализуется вектор 2, 1, О, 0., Емкость С25 заряжается до напряжения U2 , что соответствует вектору (1 , О, О, О . В соответствии со значениями напряжения U22 осуществляется разряд емкости С и формирование сигнала переноса (вектор 0, О, 3, 3). По окончании сигнала второй фазы осуществляется разряд емкости С2з и формирование сигнала . Условия разряда: (М-01, тогда (U); Ц5 иМм-2) , тогда При этом на выходе 30 формируется уровень напряжения логического нуля. Таким образом, в зависимости от числа единиц на входах N О, 1, 2, 3 на выходах 24 и 30 реализуется cooTj ветственно вектор переноса 40,0,1,3 и суммы iO,1,0,1. Предлагаемый сумматор выполнен на меньшем числе элементов по сравнению с известным, Вследствие отсутствия цепей протекания сквозного тока уменьшается мощность потребления. Таким образом, технико-экономический эффект заключается в упроще;нии предлагаемого устройства и {уменьшении мощности потребления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

| Генератор импульсов,управляемый напряжением | 1980 |

|

SU902229A1 |

| Динамический элемент | 1974 |

|

SU663111A1 |

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| МДП-инвертор | 1990 |

|

SU1780184A1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Сумматор | 1983 |

|

SU1101816A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

СУММАТОР на МДП-транзисторах, содержащий элемент И-НЕ, первый, второй и третий входы которого подключены к соответствующим .входным шинам устройства, инвертор и элемент И-ИЛИ-НЕ, отличающийс я тем, что, с целью упрощения устройства и уменьшения мощности потребления, в него введен преобразователь на трех последовательно включенных МДП-транзисторах, выводы питания элемента И-НЕ подключены к первой фазовой шине, параллельно каждому ключевому МДП-транзистору элемента И-НЕ подключен дополнительньп МДПтранзистор в резистивном включении, выход элемента И-НЕ подключен к затвору первого МДП-транзистора преобразователя, включенного между второй фазовой шиной и общей шиной, зат-. вор второго МДП-транзистора преобразователя подключен к стоку этого же транзистора, а затвор третьего МДП-транзистора преобразователя - к первой фазовой шине, исток первого и сток второго МДП-транзисторов преобразователя подключены к входу инвертора, включенного между первой фа зовой шиной и общей шиной, выход которого является выходом Перенос устройства, исток второго МДП-транзистора преобразователя подключен к первому входу элемента И-ИЛИ-НЕ, выводы питания которого подключены к второй фазовой шине, затворы последовательно включенных ключевых МДП-транзисторов элемента И-ИЛИ-НЕ, образующих второй и третий входы 00 05 этого элемента подключены соответственно к выходу Перенос устрой00 ства и к выходу элемента И-НЕ, выход элемента И-ИЛИ-НЕ является выходом Сумма устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Букреев И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| М., Советское радио, 1975, с | |||

| Водяной двигатель | 1921 |

|

SU325A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Дальномер-построитель | 1925 |

|

SU4008A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-07-07—Публикация

1983-01-17—Подача