Изобретение относится к автомати-- ке и -вычислительной технике и может быть использовано для построения устройств анализа и обработки дискретной информации.

Цель изобретения - расширение функциональных возможностей и облас- ти применения устройства за счет-реализации всех пороговых и непороговых функций двух, трех, четырех, пяти и шести переменных.

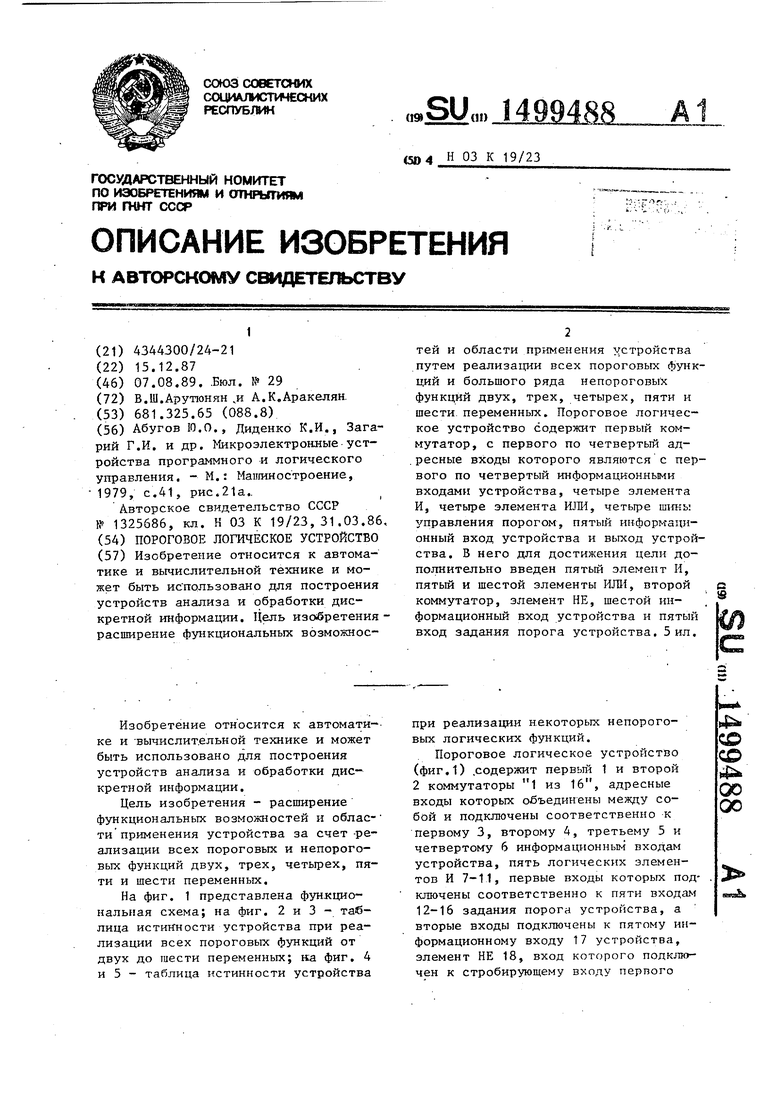

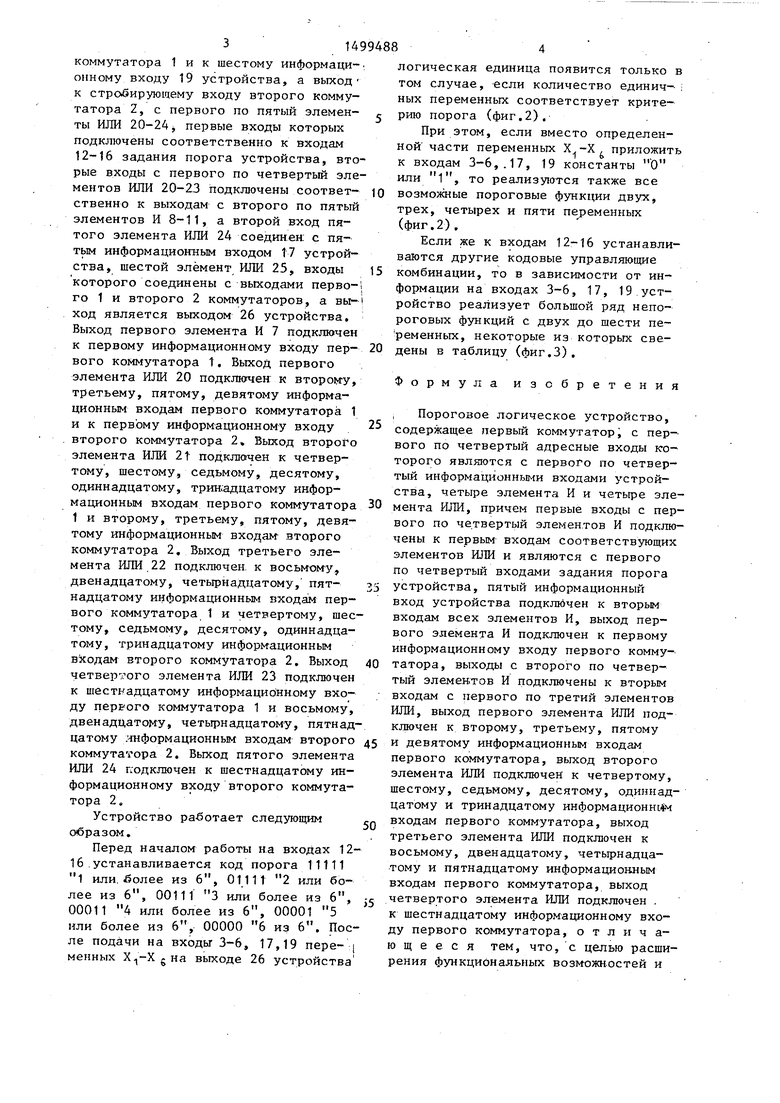

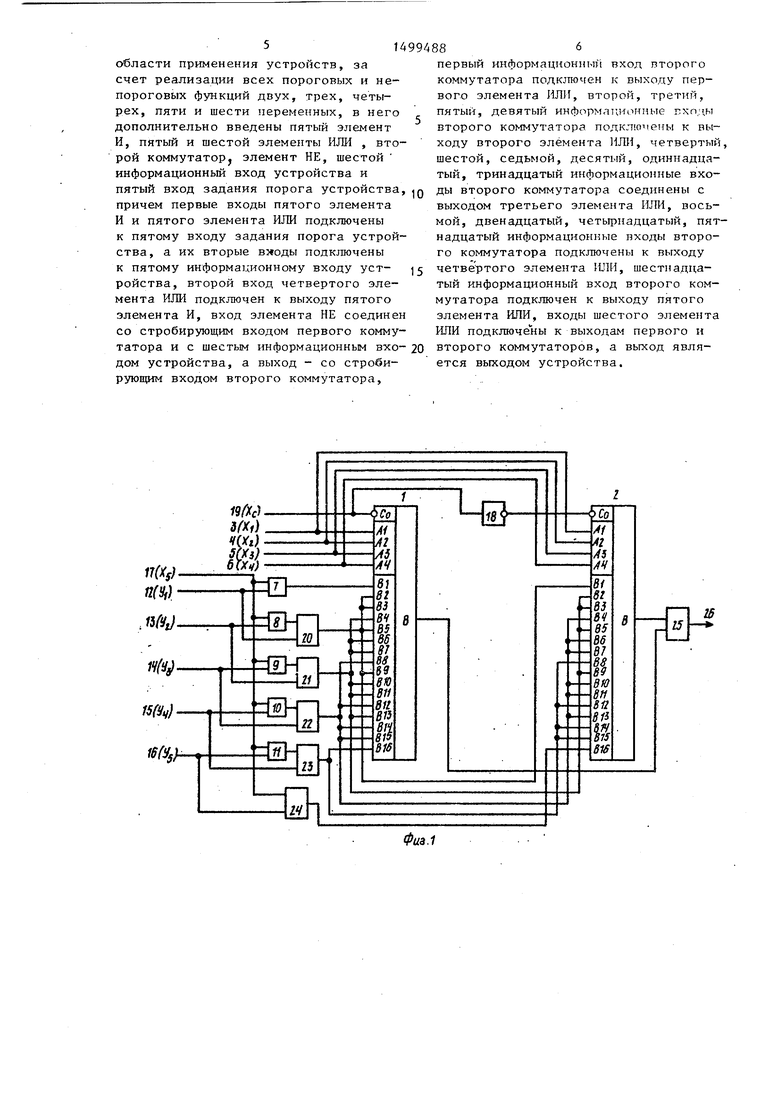

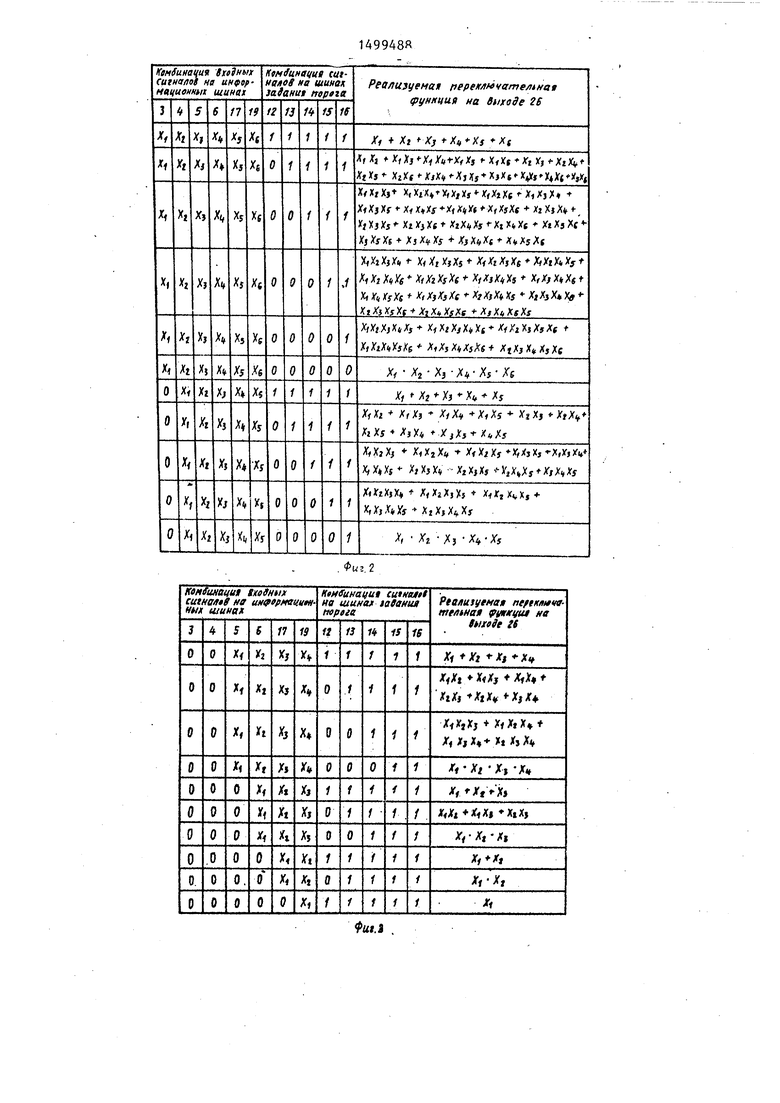

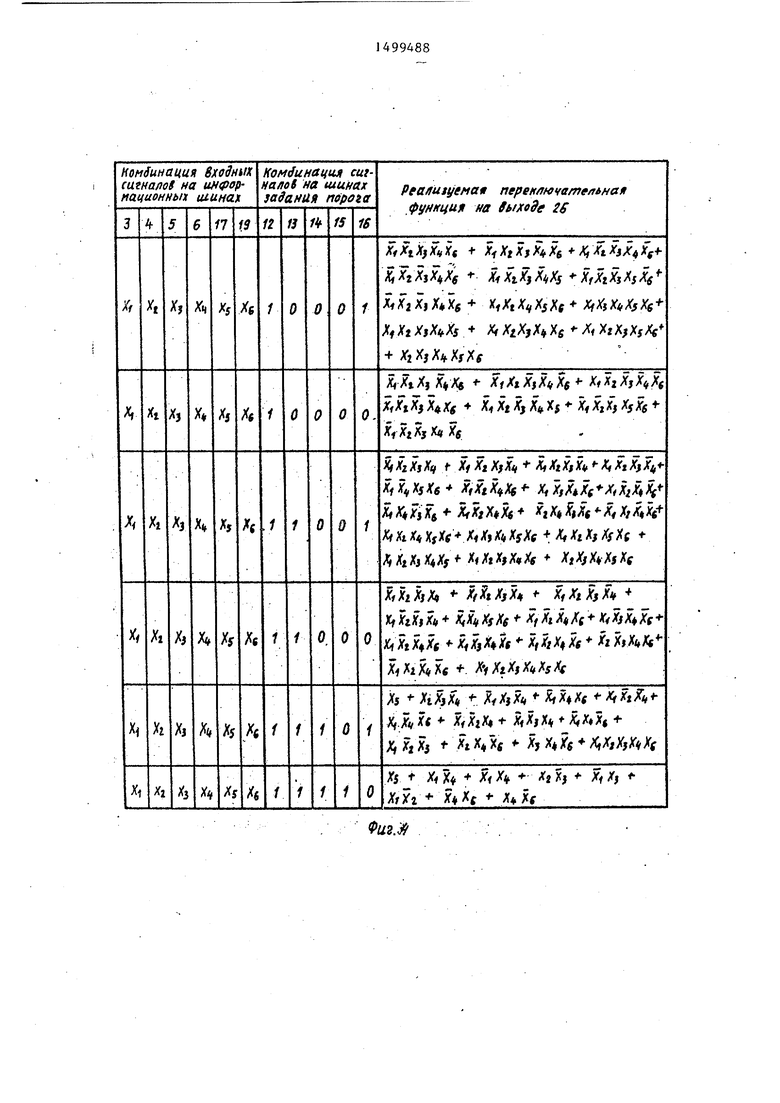

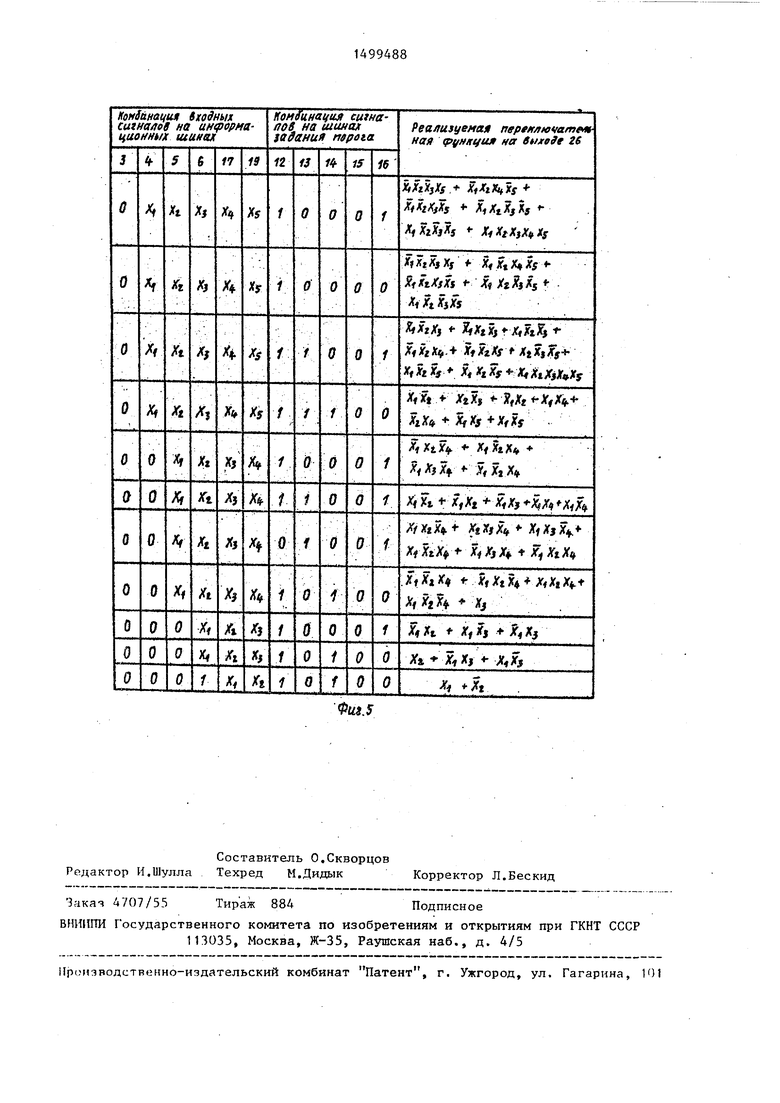

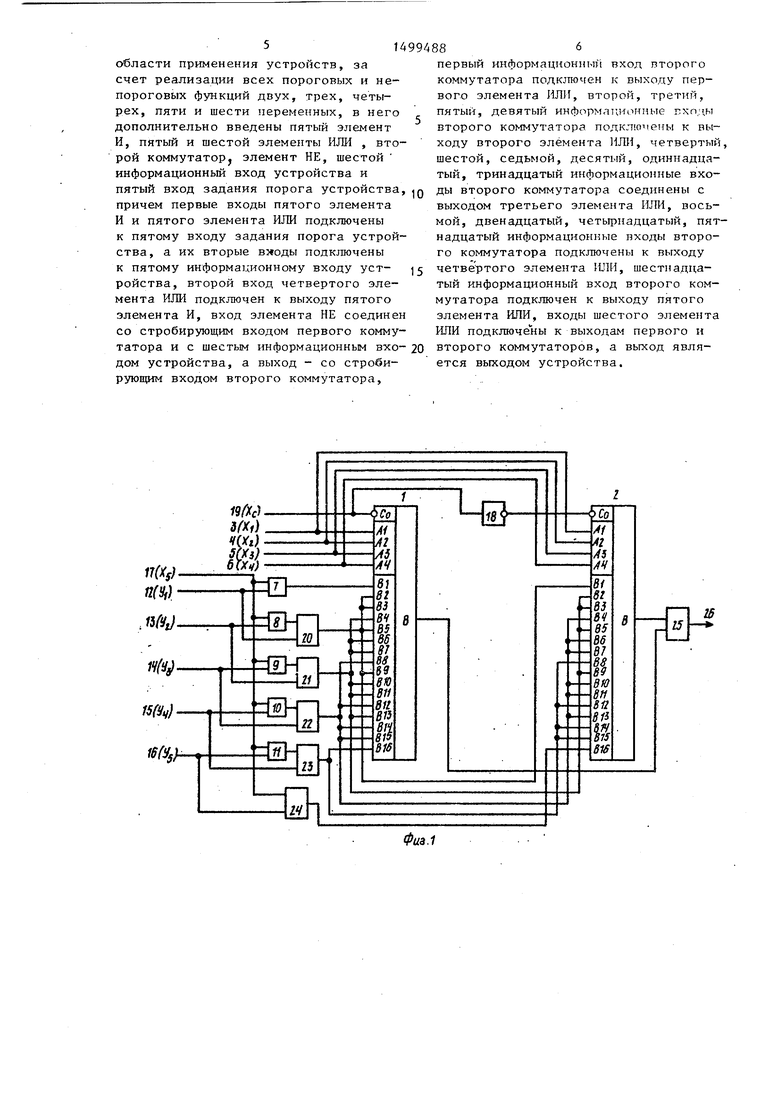

На фиг. 1 представлена фзш-кцио- нальная схема; на фиг. 2 и 3 -. таблица истинности устройства при реализации всех пороговых функций от двух до шести переменных; на фиг. 4 и 5 - таблица истинности устройства

при реализации некоторых непорого- вых логических функций.

Пороговое логическое устройство (фиг.1) .содержит первый 1 и второй 2 коммутаторы 1 из 16, адресные входы которых объединены между собой и подключены соответственно к первому 3, второму 4, третьему 5 и четвертому 6 информационным входам устройства, пять логических элементов И 7-11, первые входы которых подключены соответственно к пяти входам 12-16 задания порога устройства, а вторые входы подключены к пятому информационному входу 17 устройства, элемент НЕ 18, вход которого подключен к стробирующему входу первого

4;

СО

СО

4 00 СХ)

3149

коммутатора 1 и к шестому информаци- OIIHому входу 19 устройства, а выход- к стройирующему входу второго коммутатора Z, с первого по пятый элемен- ты ИЛИ 20-24j первые входы которых подключены соответственно к входам 12-16 задания порога устройства, вторые входы с первого по четвертый элементов ИЛИ 20-23 подключены соответ- ственно к выходам с второго по пятый элементов И 8-11, а второй вход пятого элемента ИЛИ 24 соединен с пя- ть1м информационным входом 17 устройства, шестой элемент ИЛИ 25, входы которого соединены с выходами перво- го 1 и второго 2 коммутаторов, а вы-i ход является выходом 26 устройства. Выход первого элемента И 7 подключен к первому информационному входу пер- вого коммутатора t. Выход первого элемента ИЛИ 20 подключен: к второьгу, третьему, пятому, девятому инфорна- ционным входам первого коммутатора 1 и к первому информационному входу второго коммутатора 2 Выход второго элемента ИЛИ 2t подключен к четвертому, шестому, седьмому, десятому, одиннадцатому, трин.адцатому информационным входам первого коммутатора 1 и второму, третьему, пятому, девятому информационным входам второго коммутатора 2. Выход третьего элемента ИЛИ,22 подключен, к восьмому, двенадцатому, четырнадцатому, пят- надцатому информационным входам первого коммутатора 1 и четвертому, шестому, седьмому, десятому, одиннадцатому, тринадцатому информационным входам второго коммутатора 2, Выход четвертого элемента ИЛИ 23 подключен к шестнадцатому информационному входу первого коммутатора 1 и восьмому, двенадцатому, четьфнадцатому, пятнадцатому .чнформационньм входам второго коммутатора 2. Выход пятого элемента ИЛИ 24 подключен к шестнадцатому информационному входу второго коммутатора 2.

Устройство работает следующим образом.

Перед началом работы на входах 12- 16.устанавливается код порога 11111 1 или. иолее из 6, 01111 2 или более из 6, 00111 3 или более из 6, 00011 4 или более из 6, 00001 5 или более из 6, 00000 6 из 6. После подачи на входы- 3-6, 17,19 пере- | менных Хд-XgHa выходе 26 устройства

5 0 5 0 з 0 5

0

логическая единица появится только в том случае, если количество единич-- i ных переменных соответствует критерию порога (фиг.2).

При этом, если вместо определенной части переменных X -X , приложить к входам 3-6,.17, 19 константы О или 1, то реализу1сгтся также все возможные пороговые функции двух, трех, четырех и пяти пе)еменных (фиг.2).

Если же к входам 12-16 устанавливаются другие кодовые управляющие комбинации, то в зависимости от информации на входах 3-6, 17, 19 устройство реализует большой ряд непороговых функций с двух до шести пе- ременных, некоторые из которых сведены в таблицу (фиг.З).

Формула изобретения

Пороговое логическое устройство, содержащее первый коммутатор, с первого по четвертый адресные входы которого являются с первого по четвертый информационными входами устройства, четыре элемента И и четыре элемента ИЛИ, причем первые входы с первого по четвертый элемен.тов И подключены к первым входам соответствующих элементов ИЛИ и являются с первого по четвертый входами задания порога устройства, пятый информационный вход устройства подкл1йчен к вторым входам всех элементов И, выход первого элемента И подключен к первому информационному входу первого коммутатора, выходы с второго по четвертый элементов И цодключены к вторым входам с первого по третий элементов ИЛИ, выход первого элемента ИЛИ подключен к второму, третьему, пятому и девятому информационным входам первого коммутатора, выход второго элемента ИЛИ подключен к четвертому, шестому, седьмому, десятому, одиннадцатому и тринадцатому информационн м входам первого коммутатора, выход третьего элемента ИЛИ подключен к восьмому, двенадцатому, четырнадцатому и пятнадцатому информационным входам первого коммутатора, выход четвертого элемента ИЛИ подключен . к шестнадцатому информационному входу первого коммутатора, отличающееся тем, что, с целью расширения функциональных возможностей и

области применения устройств, за счет реализации всех пороговых и непороговых функций двух, трех, четырех, пяти и шести переменных, в него дополнительно введены пятый элемент И, пятый и шестой элементы ИЛИ , второй коммутатор, элемент НЕ, шестой информационный вход устройства и пятый вход задания порога устройства причем первые входы пятого элемента И и пятого элемента ИЛИ подключены к пятому входу задания порога устройства, а их вторые в-яоды подключены к пятому информационному входу уст- ройства, второй вход четвертого элемента ИЛИ подключен к выходу пятого элемента И, вход элемента НЕ соединен со стробируюш;им входом первого коммутатора и с шестым информационным вхо- дом устройства, а выход - со строби- рующим входом второго коммутатора.

,Q 1520

994886

первый информационны) вход второго коммутатора подключен к выходу первого элемента ИЛИ, второй, третий, пятый, девятый информлци чимые гходы второго коммутатора подключены к выходу второго элемента ИЛИ, четвертый, шестой, седьмой, десятый, одиннадцатый, тринадцатый информационные входы второго коммутатора соединены с выходом третьего элемента ИЛИ, восьмой, двенадцатый, четырнадцатый, пятнадцатый информационные входы второго коммутатора подключены к выходу четвертого элемента ИЛИ, шестнадцатый информационный вход второго коммутатора подключен к выходу пятого элемента ИЛИ, входы шестого элемента ИЛИ подключе ны к выходам первого и второго коммутаторов, а выход является выходом устройства.

9U2.

Фиг.У

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговое логическое устройство | 1987 |

|

SU1422400A1 |

| Пороговое логическое устройство | 1986 |

|

SU1325686A1 |

| Мажоритарный элемент | 1987 |

|

SU1499487A1 |

| Мажоритарный элемент | 1990 |

|

SU1750052A1 |

| Многофункциональное устройство | 1982 |

|

SU1100618A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ МАНИПУЛЯТОРОМ | 2022 |

|

RU2821977C2 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Арифметическое устройство | 1981 |

|

SU1012240A1 |

| Многофункциональный логический модуль | 1981 |

|

SU1032449A1 |

| Устройство для моделирования процессов изменения параметров электронных схем | 1980 |

|

SU924712A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения устройств анализа и обработки дискретной информации. Цель изобретения - расширение функциональных возможностей и области применения устройства путем реализации всех пороговых функций и большого ряда непороговых функций двух, трех, четырех, пяти и шести переменных. Пороговое логическое устройство содержит первый коммутатор, с первого по четвертый адресные входы которого являются с первого по четвертый информационными входами устройства, четыре элемента И, четыре элемента ИЛИ, четыре шины управления порогом, пятый информационный вход устройства и выход устройства. В него для достижения цели дополнительно введен пятый элемент И, пятый и шестой элементы ИЛИ, второй коммутатор, элемент НЕ, шестой информационный вход устройства и пятый вход задания порога устройства. 3 ил.

Авторы

Даты

1989-08-07—Публикация

1987-12-15—Подача