Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств переработки дискретной информации.

Известен мажоритарный элемент, содержащий первый и второй коммутаторы 1 из 16, девять входов переменных, элемент И, элемент ИЛИ, шины нулевого и единичного логических потенциалов.

Недостатками этого мажоритарного элемента являются узкие функциональные возможности и область применения, обусловленные выполнением только мажоритарных функций 5 или более из 9, 4 или более из 7,3 или более из 5 или более из 3.

Наиболее близким по технической сущности к предлагаемому является мажоритарный элемент, содержащий первый - третий коммутаторы 1 из 16, первые-четвертые адресные входы которых соединены соотбетственно с одноименными входами

переменных мажоритарного элемента, пятый - седьмой входы переменных, элемент И, первый - четвертый входы которого соединены соответственно с восьмым - одиннадцатым входами переменных, а выход - с вторым, третьим, пятым, девятым информационными входами первого коммутатора 1 из 16 и с первым информационным входом второго коммутатора 1 из 16, шину нулевого логического потенциала, соединенную с первым информационным входом первого коммутатора 1 из 16 и с входами строби- рования первого-третьего коммутаторов 1 из 16, шину единичного логического потенциала, многопороговый элемент, первый, второй, третий и четвертый входы аргументов которого соединены соответственно с восьмым - одиннадцатым входами переменных, а пятый и шестой входы - соответственно с шинами нулевого и единичного логических потенциалов первый выход - с четвертым, шестым, седьмым, десятым, одиннадцатым, тринадцатым информаци(Л

С

ч ел о

8

ю

онными входами первого коммутатора 1 из 16, с вторым, третьим, пятым, девятым информационными входами второго коммутатора 1 из 16 и с первым информационным входом третьего коммутатора 1 из 16, а второй выход - с восьмым, двенадцатым, четырнадцатым, пятнадцатым информационными входами первого коммутатора 1 из 16, с четвертым, шестым, седьмым, десятым, одиннадцатым, тринадцатым информационными входами второго коммутатора 1 из 16 и с вторым, пятым, девятым информационными входами третьего коммутатора 1 из 16, третий выход -с шестнадцатым информационным входом первого коммутатора 1 из 16, с восьмым, двенадцатым, четырнадцатым, пятнадцатым информационными сходами второго коммутатора 1 из 16, и с четвертым, шестым, седьмым, десятым, одиннадцатым, тринадцатым информационными входами третьего коммутатора 1 из 16, элемент ИЛИ, первый - четвертый входы которого соединены соответственно с восьмым - одиннадцатым входами переменных, шестнадцатый информационный вход второго коммутатора 1 из 16 соединен с восьмым, двенадцатым, четырнадцатым и пятнадцатым инфор- мационными входами третьего коммутатора 1 из 16, многопороговый элемент содержит первый, второй и третий коммутаторы 1 из 8, выходы которых соединены соответственно с первым - третьим выходами многопорогового элемента, элемент И, выход которого соединен с четвертым, шестым, седьмым информационными входами первого коммутатора 1 из 8, с вторым, третьим и пятым информационными входами второго коммутатора 1 из 8 и с первым информационным входом третьего коммутатора 1 из 8, элемент ИЛИ, первый - третий, пятый информационные входы первого коммутатора 1 из 8 и первый вход второго коммутатора 1 из 8 соединены с шиной нулевого логического потенциала, а восьмой информационный вход третьего коммутатора 1 из 8 - с шиной единичногб логического потенциала.

Недостатками этого мажоритарного элемента являются узкие функциональные возможности и область применения, обусловленные выполнением только мажоритарных функций 6 или более из 11, 5 или более из 9, 4 или более из 7, 3 или более из 5 и 2 или более из 3.

Цель изобретения - расширение функциональных возможностей и области применения за счет обеспечения дополнительной мажоритарной функции 7 или более из 13.

Поставленная цель достигается тем, что в мажоритарный элемент, содержащий первый -третий коммутаторы 1 из 16, первые - четвертые адресные входы которых соединены соответственно одноименными входами переменных мажоритарного элемента, пятый - седьмой входы переменных, элемент И, первый - четвертый входы которого соединены соответственно с восьмым 0 одиннадцатым входами переменных, а выход - с вторым, третьим, пятым и девятым информационными входами первого коммутатора 1 из 16 и с первым информационным входом второго коммутатора 1 из 16,

5 шину нулевого логического потенциала, соединенную с первым информационным входом первого коммутатора 1 из 16 и с входами стробирования первого - третьего коммутаторов 1 из 16, шину единичного

0 логического потенциала, многопороговый элемент, первый - четвертый входы аргументов которого соединены соответственно с восьмым - одиннадцатым входами переменных а пятый и шестой входы - соответ5 ственно с шинами нулевого и единичного логических потенциалов, первый выход - с четвертым, шестым, седьмым, десятым, одиннадцатым и тринадцатым информационными входами первого коммутатора 1 из

0 16, с вторым, третьим, пятым и девятым информационными входами второго коммутатора 1 из 16 и с первым информационным входом третьего коммутатора 1 из 16, второй выход - с восьмым, двенадцатым,

5 четырнадцатым и пятнадцатым информационными входами первого коммутатора 1 из 16, с четвертым, шестым, седьмым, десятым, одиннадцатым и тринадцатым информационными входами второго коммутатора

0 1 из 16 и с вторым, третьим, пятым и девятым информационными входами третьего коммутатора 1 из 16, третий выход - с шестнадцатым информационным входом первого коммутатора 1 из 16, с восьмым,

5 двенадцатым, четырнадцатым и пятнадцатым информационными входами второго коммутатора 1 из 16 и с четвертым, шестым, седьмым, десятым, одиннадцатым, тринадцатым информационными входами

0 третьего коммутатора 1 из 16. элемент ИЛИ, первый - четвертый входы которого соединены соответственно с восьмым - одиннадцатым входами переменных, шестнадцатый информационный вход второго

5 коммутатора 1 из 16 соединен с восьмым, двенадцатым, четырнадцатым, пятнадцатым информационными входами третьего коммутатора 1 из 16, многопороговый элемент содержит первый - третий коммутаторы 1 из 8, выходы которых соединены

соответственно с первым -третьим выходами многопорогового элемента, элемент И, выход которого соединен с четвертым, шестым и седьмым информационными входами первого коммутатора 1 из 8, с вторым, третьим, пятым информационными входами второго коммутатора 1 из 8 и с первым информационным входом третьего коммутатора 1 из 8, элемент ИЛИ. первый - третий и пятый информационные входы первого коммутатора 1 из 8 и первый вход второго коммутатора 1 из 8 соединены с шиной нулевого логического потенциала, а восьмой информационный вход третьего коммутатора 1 из 8 - с шиной единичного логического потенциала, дополнительно введены двенадцатый и тринадцатый входы переменных, четвертый коммутатор 1 из 16, входстробирования которого соединен с шиной нулевого логического потенциала, порвый - четвертый адресный входы - с одноименными входами переменных, а шестнадцатый информационный вход - с шиной единичного логического потенциала, коммутатор 1 из 8, вход стробирования которого соединен с шиной нулевого логического потенциала, первый -третий адресные входы - соответственно с пятым - седьмым входами переменных, а выход - с выходом мажоритарного элемента, элементы И, ИЛИ и многопороговый элемент содержат по два дополнительных входа, соединенных соответственно с двенадцатым и тринадцатым входами переменных, многопороговый элемент содержит четвертым выход, причем первый информационный вход коммутатора 1 из 8 мажоритарного элемента соединен с выходом первого коммутатора 1 из 16, второй, третий и пятый информационные входы - с выходом второго коммутатора 1 из 16, четвертый, шестой и седьмой информационные входы - с выходом третьего коммутатора 1 из 16, восьмой информационный вход - с выходом четвертого коммутатора 1 из 16, первый информационный вход четвертого коммутатора 1 из 16 соединен с вторым выходом многопорогового элемента, второй, третий, пятый и девятый информационные входы - с третьим выходом многопорогового элемента, четвертый, шестой, седьмой, десятый, одиннадцатый, тринадцатый информационные входы - с четвертым выходом многопорогового элемента, восьмой, двенадцатый, четырнадцатый и пятнадцатый информационные входы - с шестнадцатым информационным входом третьего коммутатора 1 из 16 и с выходом элемента ИЛИ, многопороговый элемент дополнительно содержит четвертый коммутатор 1 из 8, мажоритарный элемент 2 или более из 3, а элементы И, ИЛИ содержат по одному дополнительному входу, причем первый - третий входы многопо- 5 рогового элемента соединены соответственно с первым - третьим адресными входами всех его коммутаторов 2 из 8, четвертый, пятый и шестой входы - соответственно с первыми, вторыми и третьими 0 входами его элементов И, ИЛИ и мажоритарного элемента 2 или более из 3, выход мажоритарного элемента 2 или более из 3 соединен с восьмым информационным входом ггервого коммутатора 1 из 8, с четвер5 тым, шестыми седьмым информационными входами второго коммутатора 1 из 8. с вторым, третьим и пятым информационными входами третьего коммутатора 1 из 8, с первым информационным входом четвер0 того коммутатора 1 из 8, выход элемента ИЛИ соединен с восьмым информационным входом второго коммутатора 1 из 8, с четвертым, шестым и седьмым информационными входами третьего коммутатора 1 из

5 8 с вторым, третьим и пятым информационными входами четвертого коммутатора 1 из 8, четвертый, шестой, седьмой и восьмой информационные входы четвертого коммутатора 1 из 8 соединены с шиной единич0 ного логического потенциала, а его выход- с четвертым выходом многопорогового элемента.

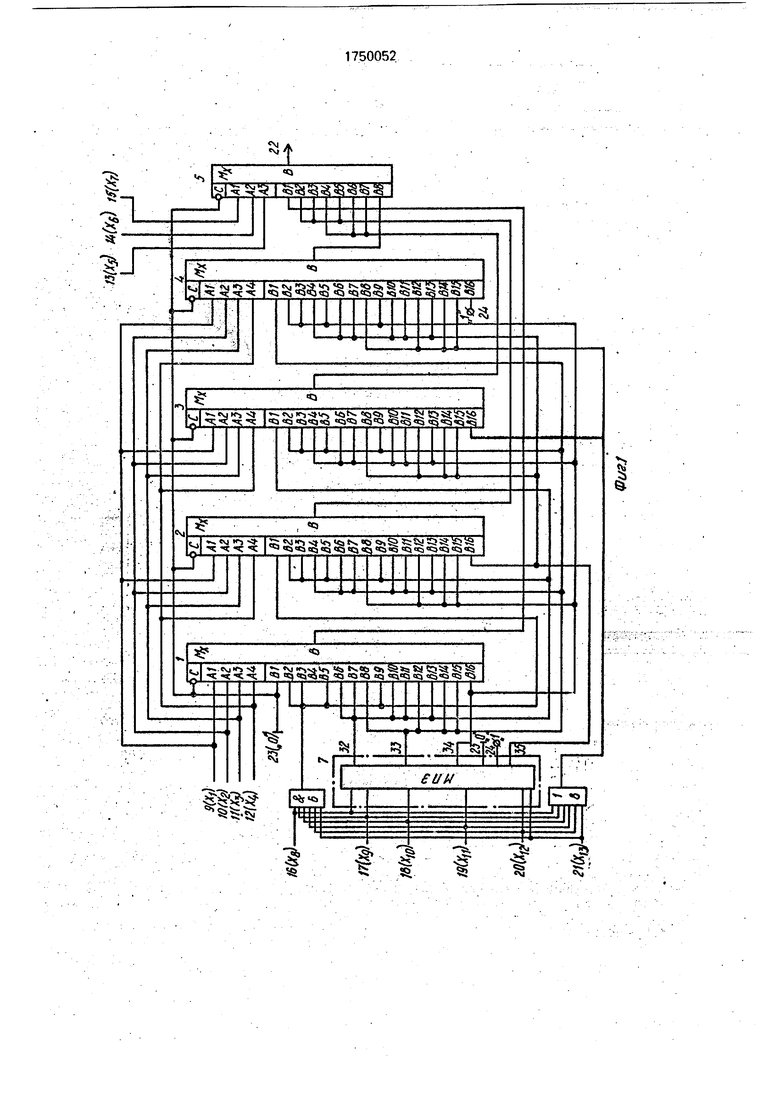

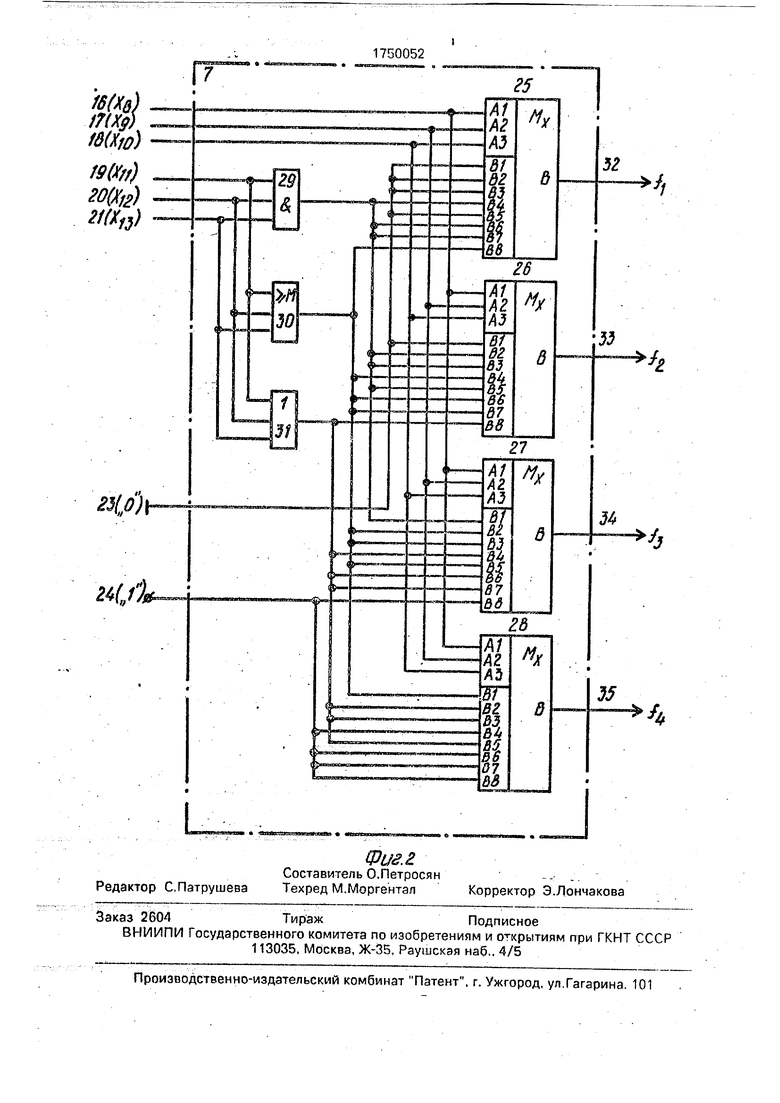

На фиг 1 представлена функциональная схема предлагаемого мажоритарного

5 элемента; на фиг. 2 - функциональная схема многопорогового элемента.

Мажоритарный элемент (фиг. 1) содержит с первого по четвертый 1-4 коммутаторы со структурой 1 из 16, коммутатор 5 со

0 структурой 1 из 8, элемент 6И 6, многопороговый элемент 7 шести аргументов, элемент 6ИЛИ 8, с первого по тринадцатый 9-21 входов переменных, выход 22 мажоритарного элемента, шины нулевого 23 и еди5 ничного 24 логических потенциалов. Многопороговый элемент 7 шести аргументов в свою очередь содержит четыре коммутатора 25-28, элементЗИ 29, мажоритарный элемент 30 со структурой 2 или более из 3,

0 элемент ЗИЛИ 31 и четыре выхода 32-35, Причем с первого по 4efBepTbiu входов переменных 9-12 устройства соединены соответственно с адресными входами коммутаторов 1-4, с пятого по седьмой вхо5 ды 13-15 переменных- с адресными входами коммутатора 5, с восьмого по тринадцатый входы 16-21 переменных - с входами элемента 6И 6, многопорогового элемента 7 и элемента 6ИЛИ 8. Первый информационный вход .коммутатора 5 соединем с выходом коммутатора 1, второй, третий и пятый информационные входы - с выходом второго коммутатора 2, четвертый, шестой и седьмой информационные входы - с выходом третьего коммутатора 3, восьмой информационный вход- с выходом четвертого коммутатора 4, а его выход соединен с выходом 22 устройства. Выход элемента 6И6 соединен с вторым, третьим, пятым, девятым информационными входами коммутатора 1 и с первым информационным входами коммутатора 2, первый выход многопорогового элемента 7 соединен с четвертым, шестым, седьмым, десятым, одиннадцатым, тринадцатым информационными входами коммутатора 1, с вторым, третьим, пятым, девятым информационными входами коммутатора 2 и с первым информационным входом коммутатора 3, второй выход многопорогового элемента 7 соединен с восьмым, двенадцатым, четырнадцатым, пятнадцатым информационными входами коммутатора 1, с четвертым, шестым, седьмым, десятым, одиннадцатым, тринадцатым информационными входами коммутатора, с вторым третьим, пятым, девятым информационными входами коммутатора 3 и с первым информационным входом коммутатора 4, третий выход многопорогового элемента 7 соединен с шестнадцатым информационным входом коммутатора 1, с восьмым, двенадцатым, четырнадцатым, пятнадцатым информационными входами коммутатора 2, с четвертым, шестым, седьмым, десятым, одинадцатым, тринадцатым информационными входами коммутатора 3 и с вторым, третьим, пятым, девятым информационными входами коммутатора 4, четвертый выход многопорогового элемента 7 соединен с шестнадцатым информационным входом коммутатора 2, с восьмым, двенадцатым, четырнадцатым, пятнадцатым информационными входами коммутатора 3 и с четвертым, шестым, седьмым, десятым, одинадцатым, тринадцатым информационными входами коммутатора 4, выход элемента 6ИЛИ 8 соединен с шестнадцатым информационным входбм коммутатора 3 и с восьмым, двенадцатым, четырнадцатым, пятнадцатым информационными входами коммутатора 4. Первый информационный вход коммутатора 1 и входы стробирования коммутаторов 1-5 соединены с шиной 23 нулевого логического потенциала, а шестнадцатый информационный вход коммутатора 4 соединен с шиной 24 единичного логического потенциала.

В многопороговом элементе 7 (фиг. 2) адресные входы коммутаторов 25-28 соединены соответственно с входами переменных 16-18, а входы элементов 29-31 - с входами переменных 19-21. Выходы коммутаторов 25-28 соединены соответственно с выходами 32-35 многопорогового элемента

7. Выход элемента 29 соединен с четвертым, шестым, седьмым информационными входами коммутатора 25, с вторым, третьим, пятым информационными входами коммутатора 26 и с первым информационным входом коммутатора 27. выход элемента 30 соединен с восьмым информационным входом коммутатора 25, с четвертым, шестым, седьмым информационными входами коммутатора 26, с вторым, третьим, пятым информационными входами коммутатора 27 и с первым информационным входом коммутатора 28. выход элемента 31 соединен с восьмым информационным входом коммутатора 26, с четвертым, шестым, седьмым

информационными входами коммутатора 27 и с вторым, третьим, пятым информационными входами коммутатора 28 Первый, второй, третий, пятый информационные входы коммутатора 25 и первый информационный вход коммутатора 26 соединены с шиной нулевого логического потенциала 23, восьмой информационный вход коммутатора 27 и четвертый, шестой, седьмой инфор- мационные входы коммутатора 28

соединены с шиной единичного логического потенциала 24.

Мажоритарный элемент (фиг 1) работает следующим образом

Для реализации мажоритарной функций 7 или более из 13 к входам подаются соответственно переменные Xi - Хп При этом если во входных кодовых комбинациях содержатся 7 или более логиче- сжих единиц (1), то на выходе 22

мажоритарного элемента возникает единичный логический потенциал (1). При других кодовых комбинаций переменных X-|-Xi3 на выходе 22 мажоритарного элемента имеется нулевой логический сигнал (О).

Мажоритарная функция 6 или более из 11 реализуется при приложении нулевых логических потенциалов к двум из входов 9-21 и произвольных переменных X - к остальным входам. Аналогично этому мажори- тарная функция 5 или более из 9 реализуется при подаче нулевых потенциалов к четырем из входов переменных 9-21, мажоритарная функция 4 или более из 7 при подаче нулевых потенциалов к шести входам переменных, мажоритарная функция 3 или более из 5 - при подаче нулевых потенциалов к восьми входам переменных, а мажоритарная функция 2 или более из 3

- при подаче нулевых потенциалов к десяти входам переменных.

Многопороговый элемент 7 (фиг. 2) работает следующим образом.

При наличии пяти или более логических единиц из шести переменных Хв-Х1з, приложенных к его соответствующим входам 16-21, на первом его выходе 32 возникает единичный потенциал, а при остальных кодах - нулевой сигнал. Аналогично этому при наличии четырех или более единиц из шести единичный потенциал возникает на его втором выходе 33, при наличии трех или более единиц из шести единичный потенциал возникает на его третьем выходе 34, а при наличии двух или более единиц из шести - на четвертом выходе 35.

Полная таблица истинности представлена для многопорогового элемента 7 шести переменных.

Таким образом, предлагаемый мажоритарный элемент реализует все возможные мажоритарные функции 7 или более из 13, 6 или более из 11, 5 или более из 9, 4 или более из 7, 3 или более из 5 и 2 или более из 3, что свидетельствует о его широких функциональных возможностях и области применения.

Формула изобретения

Мажоритарный элемент, содержащий первый - третий коммутаторы 1 из 16, .первые - четвертые адресные входы которых соединены соответственно с одноименными входами переменных мажоритарного элемента, пятый - седьмой входы переменных, элемент И, первый - четвертый входы которого соединены соответственно с восьмым - одиннадцатым входами переменных, а выход - с вторым, третьим, пятым и девятым информационными входами первого коммутатора 1 из 16 и с первым информационным входом второго коммутатора 1 из 16, шину нулевого логического потенциала, соединенную с первым информационным входом первого коммутатора 1 из 16 и с входами стробирования первого - третьего коммутаторов 1 из 16, шину единичного логического потенциала, многопороговый элемент, первый - четвертый входы аргументов которого соединены соответственно с восьмым - одиннадцатым входами переменных, а питый и шестой входы - соответственно с шинами нулевого и единичного логических потенциалов, первый выход - с четвертым, шестым, седьмым, десятым, одиннадцатым и тринадцатым информационными входами первого коммутатора 1 из 16, с вторым, третьим, пятым и девятым информационными входами второго коммутатора 1 из 16 и с первым информационным входом третьего коммутатора 1 из 16, второй выход - с восьмым, двенадцатым, четырнадцатым и пятнадцатым информационными входами первого коммутатора 1 из 5 16, с четвертым, шестым, седьмым, десятым, одиннадцатым и тринадцатым информационными входами второго коммутатора 1 из 16 и с вторым, третьим, пятым и девятым информационными входами третьего

0 коммутатора 1 из 16, третий выход - с шестнадцатым информационным входом первого коммутатора 1 из 16, с восьмым, двенадцатым, четырнадцатым и пятнадцатым информационными входами второго

5 коммутатора 1 из 16 и с четвертым, шестым, седьмым, десятым, одиннадцатым и тринадцатым информационными входами третьего коммутатора 1 из 16, элемент ИЛИ, первый - четвертый входы которого

0 соединены соответственно с восьмым - одиннадцатым входами переменных, шестнадцатый информационный вход второго коммутатора 1 из 16 соединен с восьмым, двенадцатым, четырнадцатым и пятнадца5 тым информационными входами третьего коммутатора 1 из 16, многопороговый элемент содержит первый - третий коммутаторы 1 из 8, выходы которых соединены соответственно с первым - третьим выхода0 ми многопорогового элемента, элемент И, выход которого соединен с четвертым, шестым и седьмым информационными входами первого коммутатора 1 из 8, с вторым, третьим и пятым информационными входа5 ми второго коммутатора 1 из 8 и с первым информационным входом третьего коммутатора 1 из 8, элемент ИЛИ, первый - третий и пятый информационные входы первого коммутатора 1 из 8 и первый вход

0 второго коммутатора 1 из 8 соединены с шиной нулевого логического потенциала, а восьмой информационный вход третьего коммутатора 1 из 8 - с шиной единичного логического потенциала, отличающий5 с я тем, что, с целью расширения функциональных возможностей и области применения за счет реализации мажоритарной функции 7 или более из 13, в него дополнительно введены двенадцатый и тринадца0 тый входы переменных, четвертый коммутатор 1 из 16. ехид стробирования которого соединен с шиной нулевого логического потенциала, первый-четвертый адресный входы - с одноименными входами

5 переменных, а шестнадцатый информационный вход - с шиной единичного логического потенциала, коммутатор 1 из 8, вход стробирования которого соединен с шиной нулевого логического потенциала, первый - третий адресные входы - соответственно с

пятым - седьмым входами переменных, а выход - с выходом мажоритарного элемента, элементы И, ИЛИ и многопороговый элемент содержит по два дополнительных пхода, соединенных соответственно с двенадцатым и тринадцатым входами переменных, многопороговый элемент содержит четвертый выход, причем первый информационный вход коммутатора 1 из 8 мажоритарного элемента соединен с выходом первого коммутатора 1 из 16, второй, третий и пятый информационные входы - с выходом второго коммутатора 1 из 16, четвертый, шестой и седьмой информационные входы - с выходом третьего коммутатора 1 из 16, восьмой информационный вход - с выходом четвертого коммутатора 1 из 16, первый информационный вход четвертого коммутатора 1 из 16 соединен с вторым выходом многопорогового элемента, второй, третий, пятый и девятый информационные входы - с третьим выходом многопорогового элемента, четвертый, шестой, седьмой, десятый, одиннадцатый и тринадцатый информационные входы - с четвертым выходом многопорогового элемента, восьмой, двенадцатый, четырнадцатый и пятнадцатый информационные входы с шестнадцатым информационным входом третьего коммутатора 1 из 16 и с выходом элемента ИЛИ, многопороговый элемент дополнительно содержит четвертый коммутатор 1 из 8, мажоритарный элемент 2 или более из 3, а его элементы И, ИЛИ содержат по одному дополнительному входу, причем первый - третий входы многопорогового элемента соединены соответ- стаенно с первым - третьим адресными входами всех его коммутаторов 1 из 8, четвертый, пятый и шестой входы - соответственно с первыми, вторыми и третьими

входами его элементов И, ИЛИ и мажоритарного элемента 2 или более из 3, выход мажоритарного элемента 2 или более из 3 соединен с восьмым информационным входом первого коммутатора 1 из 8, с четвертым, шестым и седьмым информационными входами второго коммутатора 1 из 8, с вторым, третьим и пятым информационными входами третьего коммутатора 1 из 8, с первым информационным входом четвертого коммутатора 1 из 8, выход элемента ИЛ И соединен с восьмым информационным входом второго коммутатора 1 из 8, с четвертым, шестым и седьмым информационными входами третьего коммутатора 1 из

8, с вторым, третьим и пятым информационными входами четвертого коммутатора 1 из 8, четвертый, шестой, седьмой и восьмой информационные входы четвертого коммутатора 1 из 8 соединены с шиной единичного логического потенциала, а его выход - с четвертым выходом многопорогового элемента,

CN

in о о in r

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарный элемент | 1987 |

|

SU1499487A1 |

| Пороговое логическое устройство | 1987 |

|

SU1422400A1 |

| Преобразователь кодов | 1988 |

|

SU1536509A1 |

| Многоканальное устройство для синхронизации | 1980 |

|

SU883888A2 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Мажоритарный элемент | 1988 |

|

SU1538249A1 |

| Многофункциональное устройство | 1985 |

|

SU1291963A1 |

| Пороговое логическое устройство | 1987 |

|

SU1499488A1 |

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации различных мажоритарных функций из тринадцати переменных при построении различных устройств переработки дискретной информации Цель изобретения - расширение функциональных возможностей и области применения Мажоритарный элемент содержит три коммутатора 1 из 16 элемент И, элемент ИЛИ, многопороговый элемент Для достижения поставленной цели в мажоритарный элемент дополнительно введены четвертый коммутатор 1 из 16 и коммутатор 1 из 8 2 ил , 1 табл

я т.

(Wv (tyv fr)u

| Мажоритарный элемент | 1987 |

|

SU1499487A1 |

Авторы

Даты

1992-07-23—Публикация

1990-06-27—Подача