Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств переработки дискретной информации.

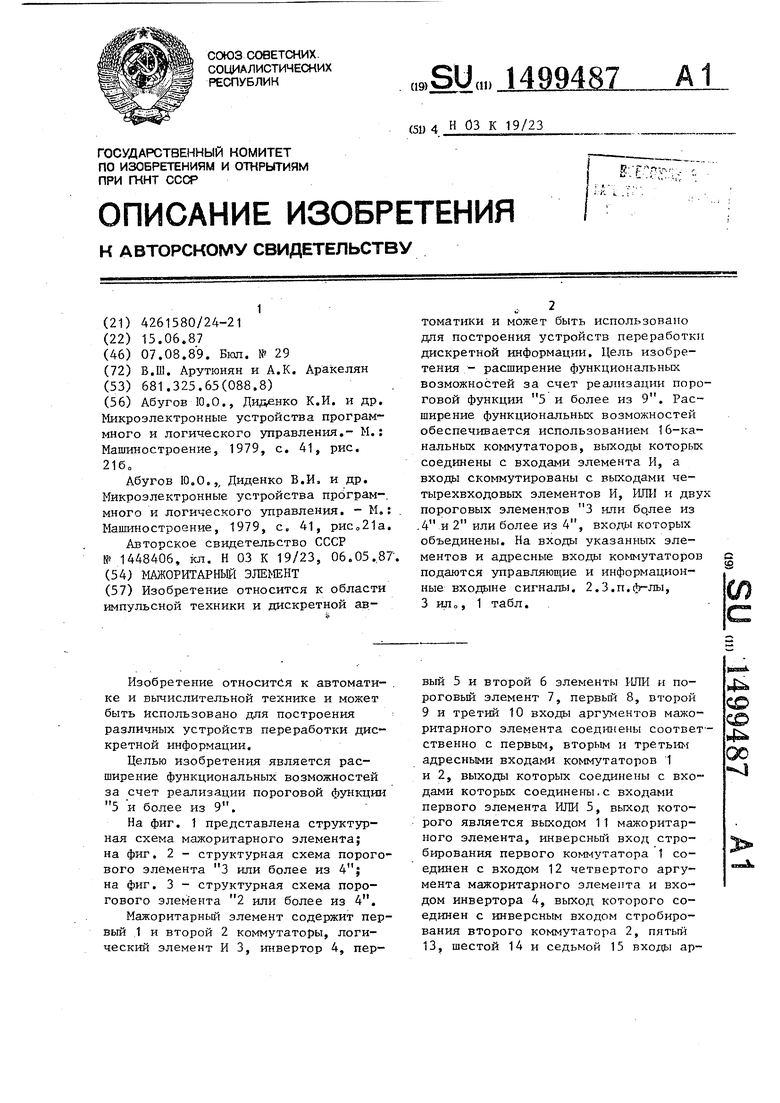

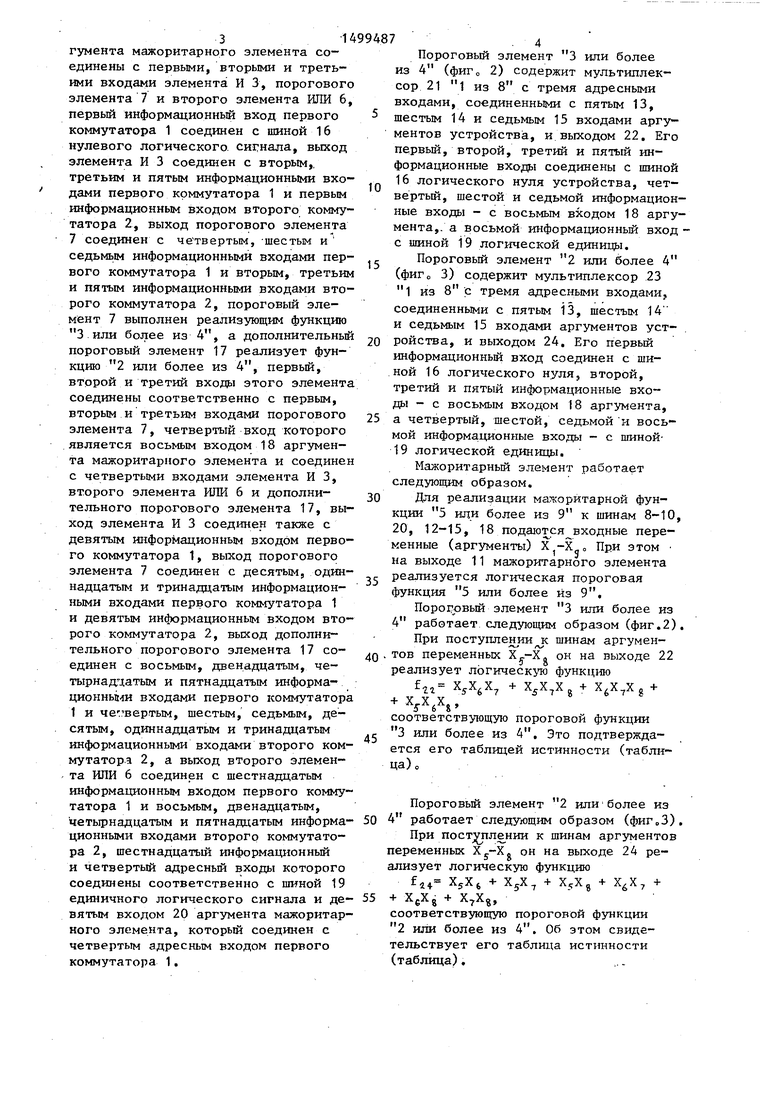

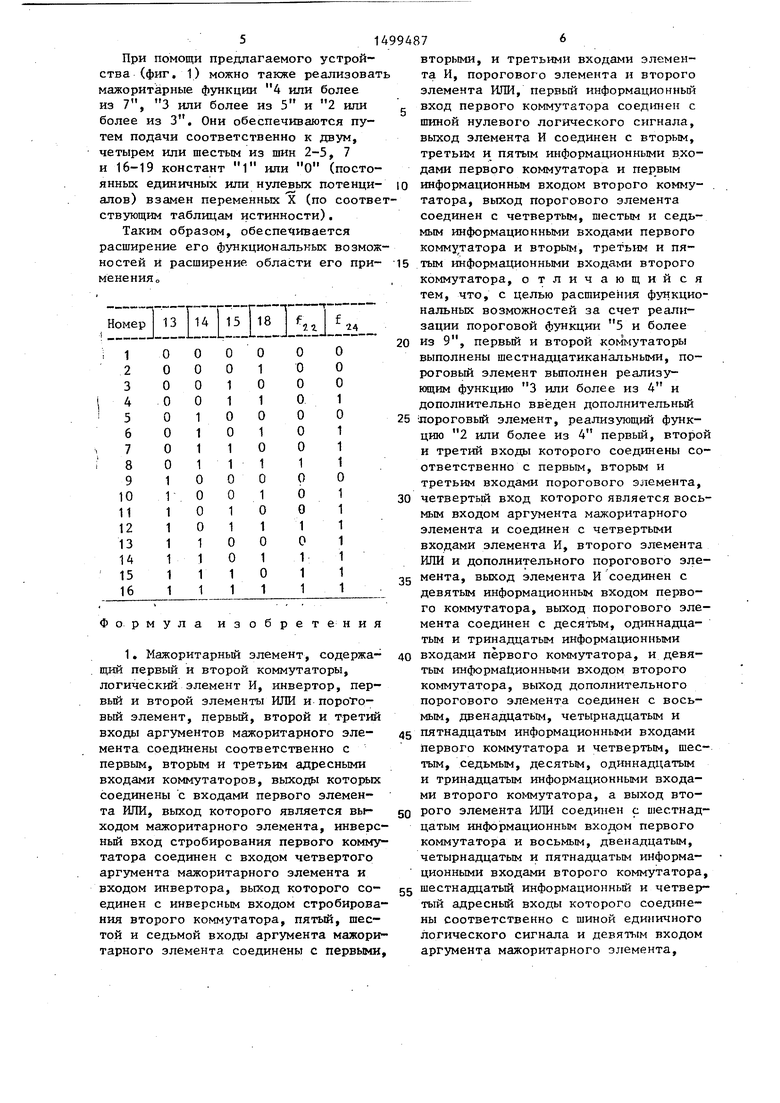

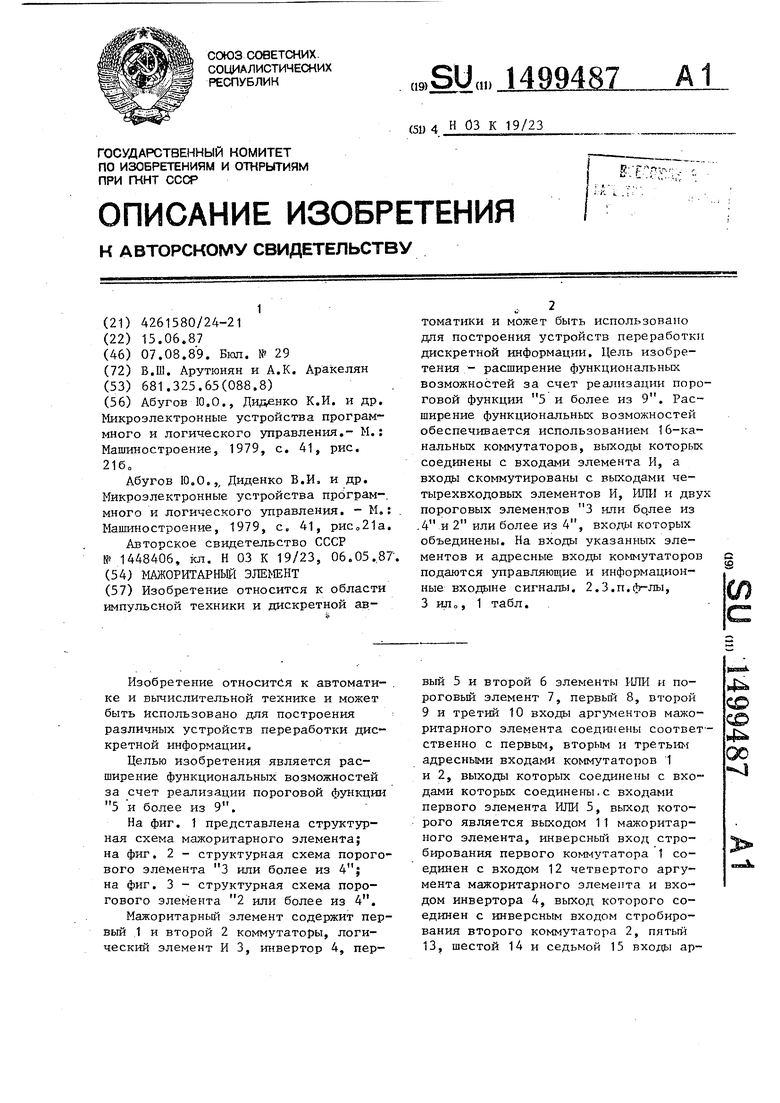

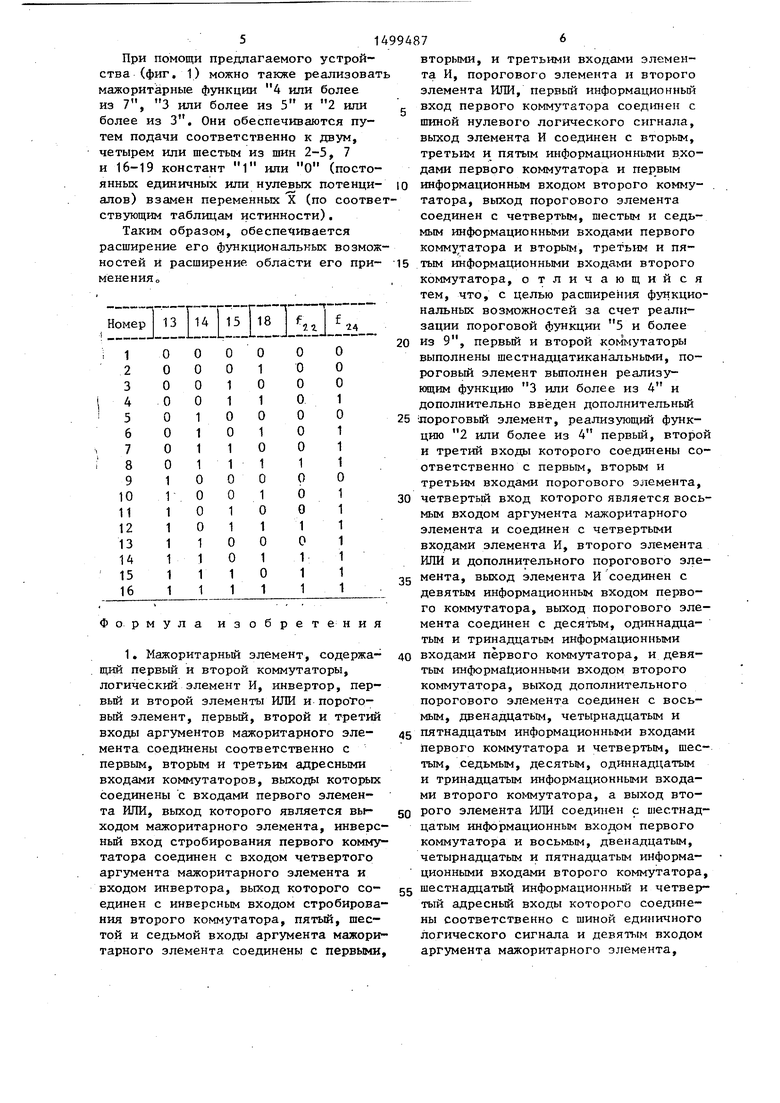

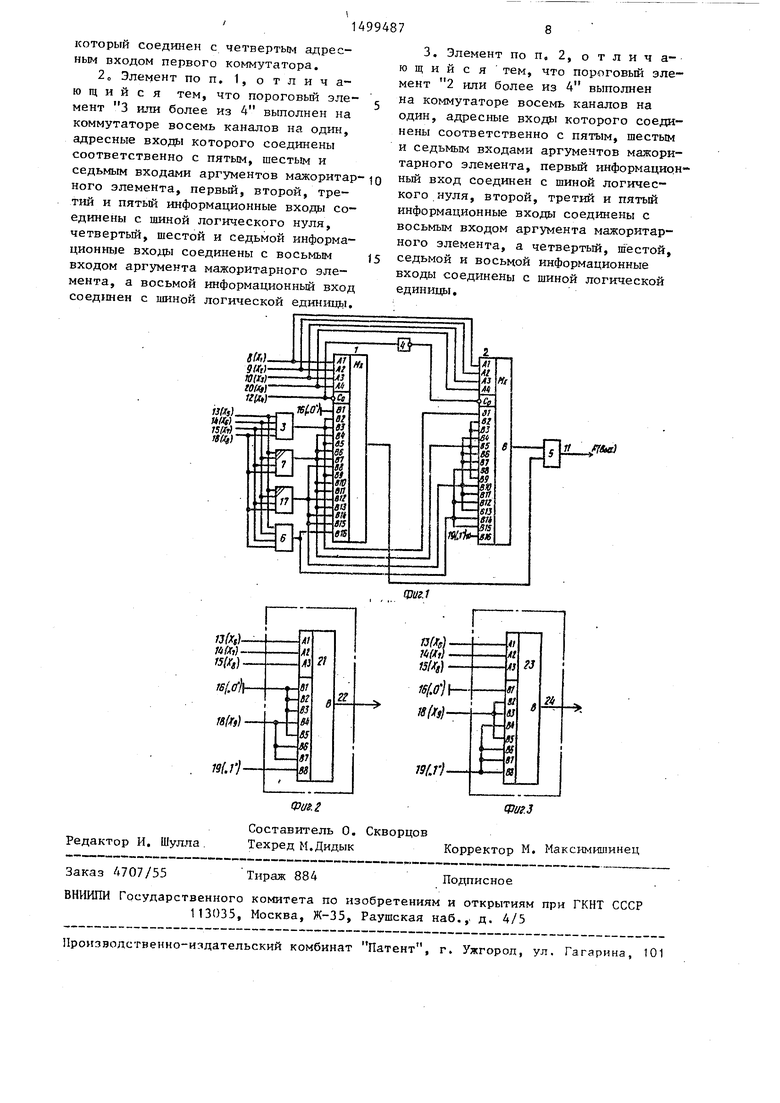

Целью изобретения является расширение функциональных возможностей за счет реализации пороговой функции 5 и более из 9. На фиг. 1 представлена структурная схема мажоритарного элемента; на фиг. 2 - структурная схема порогового элемента 3 или более из на фиг. 3 - структурная схема порогового элем ента 2 или более из 4.

Мажоритарный элемент содержит первый 1 и второй 2 коммутаторы, логический элемент И 3, инвертор 4, первый 5 и второй 6 элементы ИЛИ и пороговый элемент 7, первый 8, второй 9 и третий 10 входы apгy eнтoв мажоритарного элемента соединены соответственно с первым, вторым и третьим адресными входами коммутаторов 1 и 2, выходы которых соединены с входами которых соединены.с входами первого элемента ШШ 5, выход которого является выходом 11 мажоритарного элемента, инверсньй вход стро- бирования первого коммутатора 1 соединен с входом 12 четвертого аргумента мажоритарного элемента и входом инвертора 4, выход которого соединен с инверсным входом стробиро- вания второго коммутатора 2, пятый 13, шестой 14 и седьмой 15 входа ар

4 00

гумента мажоритарного элемента соединены с первыми, вторыми и третьими входами элемента И 3, порогового элемента 7 и второго элемента ИЛИ 6, первый информационный вход первого коммутатора 1 соединен с шиной 16 нулевого логического си1:нала, выход элемента И 3 соединен с вторым,, третьим и пятым информационными входами первого коммутатора 1 и первым информационным входом второго коммутатора 2, выход порогового элемента 7 соединен с че твертым, -шестым и седьмьм информационными входами первого коммутатора 1 и вторым, третьим и пятым информационными входами второго коммутатора 2, пороговый элемент 7 выполнен реализующим функцию З.или более из 4, а дополнительньй пороговый элемент 17 реализует функцию 2 или более из 4, первьй, второй и третий входы этого элемента соединены соответственно с первым, вторым и третьим входами порогового элемента 7, четвертый вход которого является восьмым входом 18 аргумента мажоритарного элемента и соединен с четвертыми входами элемента ИЗ, второго элемента ИЛИ 6 и дополнительного порогового элемента 17, выход элемента И 3 соединен также с девятым информационным входом первого коммутатора 1, выход порогового элемента 7 соединен с десятым, одиннадцатым и тринадцатым информационными входами первого коммутатора 1 и девятым информационным входом второго коммутатора 2, выход дополнительного порогового элемента 17 соединен с восьмым, двенадцатым, четырнадцатым и пятнадцатым информа- ционньии входами первого коммутатора 1 и чег вертым, шестым, седьмым, десятым, одиннадцатым и тринадцатым

45

или более из 4. Это подтверждается его таблицей истинности (таблица)

информационными входами второго коммутатора 2, а выход второго элемента ИЛИ 6 соединен с шестнадцатым информационным входом первого коммутатора 1 и восьмым, двенадцатым, Пороговый элемент 2 или-более из четырнадцатым и пятнадцатым информа- 50 4 работает следующим образом (фиг„3).

При поступлении к шинам аргументов переменных . он на выходе 24 реционными входами второго коммутатора 2, шестнадцатый информационный и четвертый адресный входы которого соединены соответственно с шиной 19 единичного логического сигнала и девятым входом 20 аргумента мажоритарного элемента, который соединен с четвертым адресным входом первого коммутатора 1.

ализует логическую функцию

-2+XjX,

XjX.

+ XjXg + , +

55

XeXg +

XyXg,

соответствующую пороговой функции 2 или более из 4. Об этом свидетельствует его таблица истинности (таблица).

0

5

0

5

0

5

0

Пороговый элемент 3 или более из 4 (фиго 2) содержит мультиплексор 21 1 из 8 с тремя адресными входами, соединенными с пятым 13, шестым 14 и седьмым 15 входами аргументов устройства., и выходом 22. Его первый, второй, третий и пятый информационные входы соединены с шиной 16 логического нуля устройства, четвёртый, шестой и седьмой информационные входы - с восьмым входом 18 аргумента,- а восьмой информационный вход - с шиной 19 логической единицы.

Пороговый элемент 2 или более 4 (фиг о 3) содержит мультиплексор 23 1 из В с тремя адресными входами, соединенными с пятым 13, шестым 14 и седьмым 15 входами аргументов устройства, и выходом 24. Его первый информационный вход соединен с шиной 16 логического нуля, второй, третий и пятый информационные вхо да - с восьмым входом 18 аргумента, а четвертый, шестой, седьмой и восьмой информационные входы - с шиной- 19 логической единицы.

Мажоритарньй элемент работает следующим образом.

Для реализации мажоритарной функции 5 или более из 9 к шинам 8-10, 20, 12-15, 18 подаются входные переПри этом элемента

реализуется логическая пороговая функция 5 или более из 9.

Пороговый элемент 3 или более из 4 работает следующим образом (фиг.2).

При поступлении шинам аргументов переменных . он на выходе 22 реализует логическую функцию

f, .Х, + , + +

менные (аргументы) на выходе 11 мажоритарного

.Xg +

5

,

соответствующую пороговой функции 3

или более из 4. Это подтверждается его таблицей истинности (таблица)

Пороговый элемент 2 или-более из 0 4 работает следующим образом (фиг„3).

При поступлении к шинам переменных . он на выхо

ализует логическую функцию

-2+XjX,

XjX.

+ XjXg + , +

XeXg +

XyXg,

соответствующую пороговой функции 2 или более из 4. Об этом свидетельствует его таблица истинности (таблица).

51

При помощи предлагаемого устройства (фиг. 1) можно также реализоват мажоритарные функции 4 или более из 7, 3 или более из 5 и 2 или более из 3. Они обеспечиваются путем подачи соответственно к двум, четырем или шестым из шин 2-5, 7 и 16-19 констант 1 или О (постоянных единичных или нулевых потенциалов) взамен переменных X (по соотвествующим таблицам истинности),

Таким образом, обеспечивается расширение его функциональных возможностей и расширение области его применения о

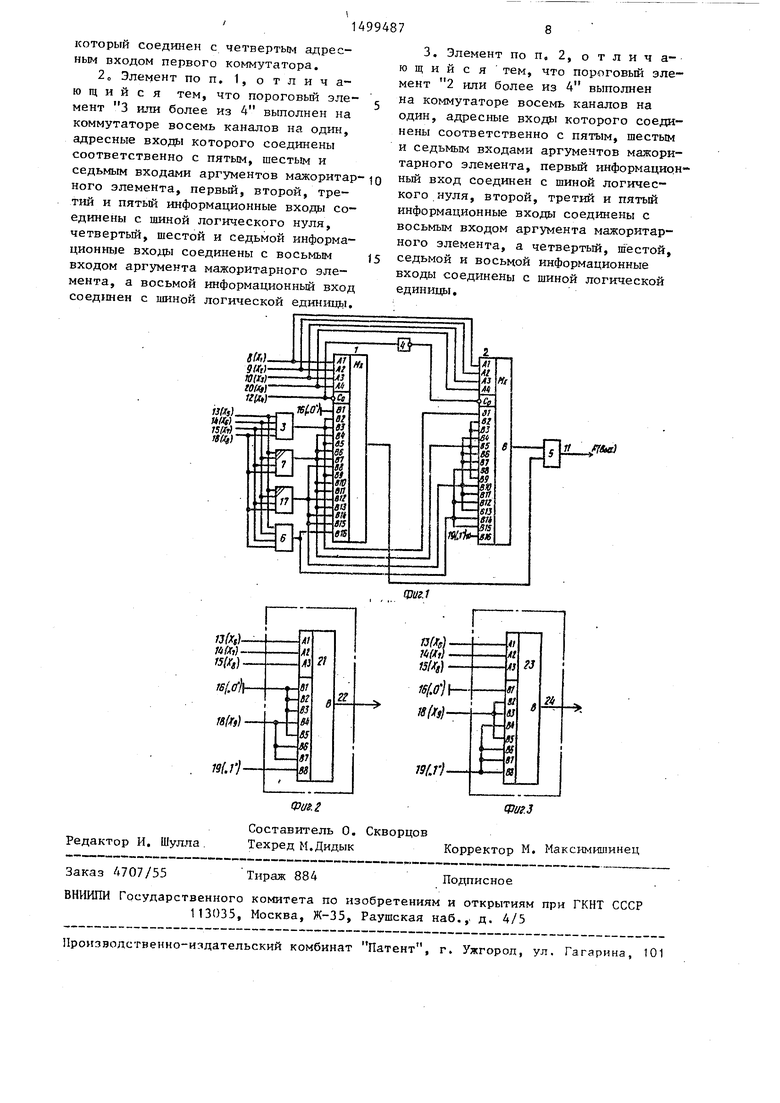

Номер

ЕГЖПЕЕ

24

Формула изобретения

1. Мажоритарный элемент, содержащий первый и второй коммутаторы, логический элемент И, инвертор, первый и второй элементы ИЛИ и пороТо- вый элемент, первый, второй и третий входы аргументов мажоритарного элемента соединены соответственно с первым, вторым и третьим адресными входами коммутаторов, выходы которых соединены с входами первого элемента ИЛИ, выход которого является вы ходом мажоритарного элемента, инверс- ньм вход стробирования первого коммутатора соединен с входом четвертого аргумента мажоритарного элемента и входом инвертора, выход которого соединен с инверсным входом стробирования второго коммутатора, пятый, шестой и седьмой входы аргумента мажоритарного элемента соединены с первыми.

вторыми, и третьими входами элемента И, порогового элемента и второго элемента ИЛИ, первьй информационный вход первого коммутатора соедш1ен с шиной нулевого логического сигнала, выход элемента И соединен с вторым, третьим и пятым информационными входами первого коммутатора и первым информационным входом второго комму- . татора, выход порогового элемента соединен с четвертым, шестым и седьмым информационными входами первого комму татора и вторым, третьим и пятым информационными входами второго коммутатора, отличающийся тем, что, с целью расширения функциональных возможностей за счет реализации пороговой функции 5 и более

из 9, первый и второй коммутаторы выполнены шестнадцатиканальными, пороговый элемент выполнен реализующим функцию 3 или более из 4 и дополнительно введен дополнительный

лороговый элемент, реализующий функцию 2 или более из 4 первый, второй и третий входы которого соединены соответственно с первым, вторым и третьим входами порогового элемента,

четвертой вход которого является восьмым входом аргумента мажоритарного элемента и соединен с четвертыми входами элемента И, второго элемента ИЛИ и дополнительного порогового элемента, выход элемента И соединен с девятым информационным входом первого коммутатора, выход порогового элемента соединен с десятым, одиннадцатым и тринадцатым информационными

входами первого коммутатора, и девятым информационными входом второго коммутатора, выход дополнительного порогового элемента соединен с восьмым, двенадцатью, четырнадцатым и

пятнадцатым информационными входами первого коммутатора и четвертым, шестым, седьмым, десятым, одиннадцатым и тринадцатым информационными входами второго коммутатора, а выход второго элемента ИЛИ соединен с шестнадцатым информационным входом первого коммутатора и восьмым, двенадцатым, четырнадцатым и пятнадцатым информационными входами второго коммутатора,

шестнадцатый информационный и четвертый адресный входы которого соединены соответственно с шиной единичного логического сигнала и девятым входом аргумента мажоритарного элемента.

который Соединен с четвертым адресным входом первого коммутатора.

2о Элемент по п. 1, о т л и ч а- ю щ и и с я тем, что пороговый эле- мент 3 или более из 4 выполнен на коммутаторе восемь каналов на один, адресные входы которого соединены соответственно с пятым, шестым и седьмым входами аргументов мажоритарного элемента, первьш, второй, третий и пятый информационные входы соединены с шиной логического нуля, четвертый, шестой и седьмой информационные входы соединены с восьмым входом аргумента мажоритарного элемента, а восьмой информационньй вход соед1шен с шиной логической единиць.

3. Элемент по п, 2, отличающийся тем, что пороговый элемент 2 или более из 4 выполнен на коммутаторе восемь каналов на один, адресные входы которого соединены соответственно с пятым, шестым и седьмым входами аргументов мажоритарного элемента, первый информацирн ньш вход соединен с шиной логического нуля, второй, третий и пятый информационные входы соединены с восьмым входом аргумента мажоритарного элемента, а четвертый, шестой, седьмой и восьмой информационные входы соединены с шиной логической единицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговое логическое устройство | 1987 |

|

SU1422400A1 |

| Мажоритарный элемент | 1988 |

|

SU1538249A1 |

| Мажоритарный элемент | 1990 |

|

SU1750052A1 |

| Мажоритарный элемент | 1987 |

|

SU1448406A1 |

| Пороговое логическое устройство | 1987 |

|

SU1499488A1 |

| Многофункциональный логический модуль | 1987 |

|

SU1495990A1 |

| Пороговое логическое устройство | 1986 |

|

SU1325686A1 |

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВУХ ПЕРЕМЕННЫХ | 1984 |

|

SU1371306A1 |

| Мажоритарный элемент "4 или более из 7 | 1988 |

|

SU1531210A1 |

Изобретение относится к области импульсной техники и дискретной автоматики и может быть использовано для построения устройств переработки дискретной информации. Цель изобретения - расширение функциональных возможностей за счет реализации пороговой функции "5 и более из 9". Расширение функциональных возможностей обеспечивается использованием 16-канальных коммутаторов, выходы которых соединены с входами элемента И, а входы скоммутированы с выходами четырехвходовых элементов И, ИЛИ и двух пороговых элементов "3 и более из 4" и "2 и более из 4", входы которых объединены. На входы указанных элементов и адресные входы коммутаторов подаются управляющие и информационные входные сигналы. 2 з.п. ф-лы, 3 ил., 1 табл.

Редактор И, Шулла

Ф(/.2

Составитель О. Скворцов

Техред М.Дидык

Заказ 4707/55

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб.,. д. 4/5

Фиг.з

Корректор М. Макснмишинец

Подписное

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| и др | |||

| Микроэлектронные устройства программного и логического зшравления.- М.: Машиностроение, 1979, с | |||

| Механический грохот | 1922 |

|

SU41A1 |

| Приспособление для подвешивания тележки при подъемках сошедших с рельс вагонов | 1920 |

|

SU216A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| - М.: | |||

| Машиностроение, 1979, с | |||

| Механический грохот | 1922 |

|

SU41A1 |

| Мажоритарный элемент | 1987 |

|

SU1448406A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-07—Публикация

1987-06-15—Подача