Изобретение относится к вычислительной технике и может быть использовано, например, в устройствах внешней памяти на магнитной ленте.

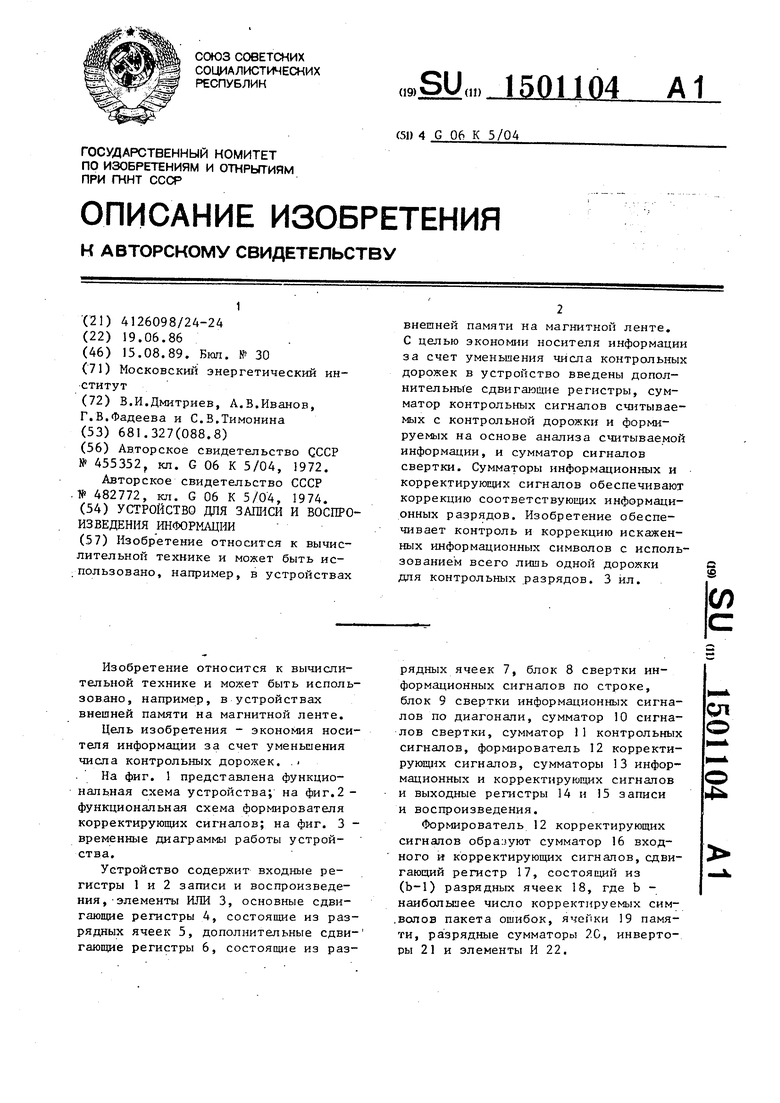

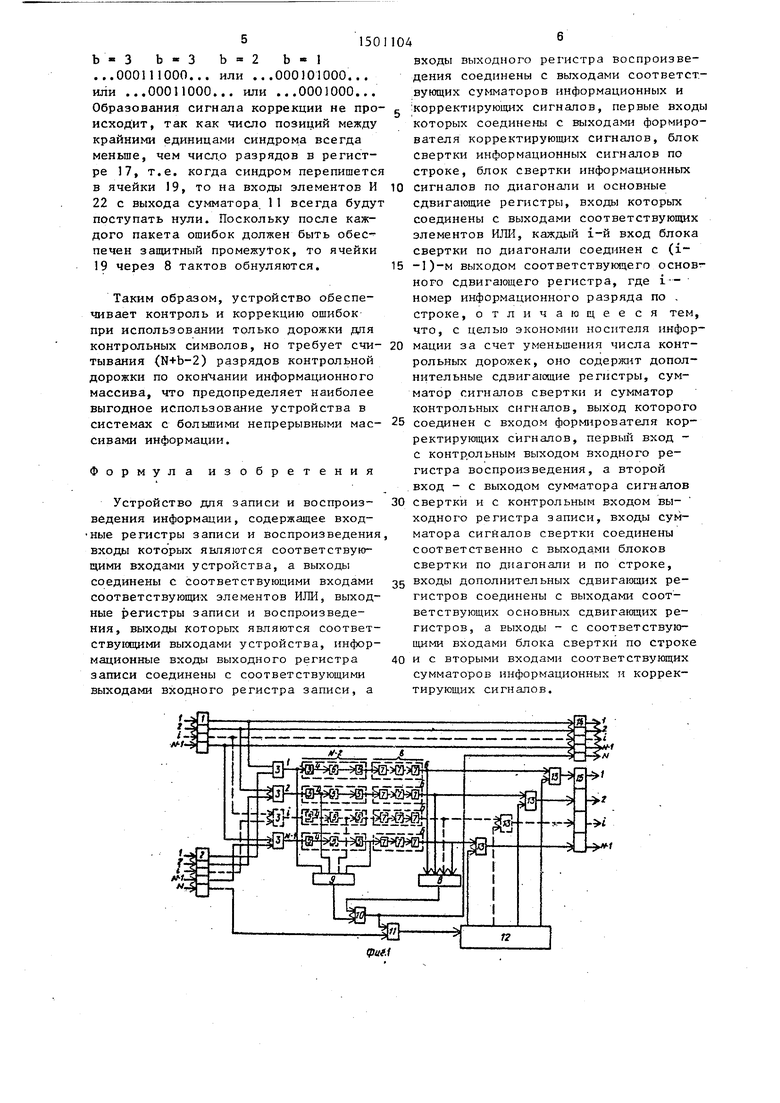

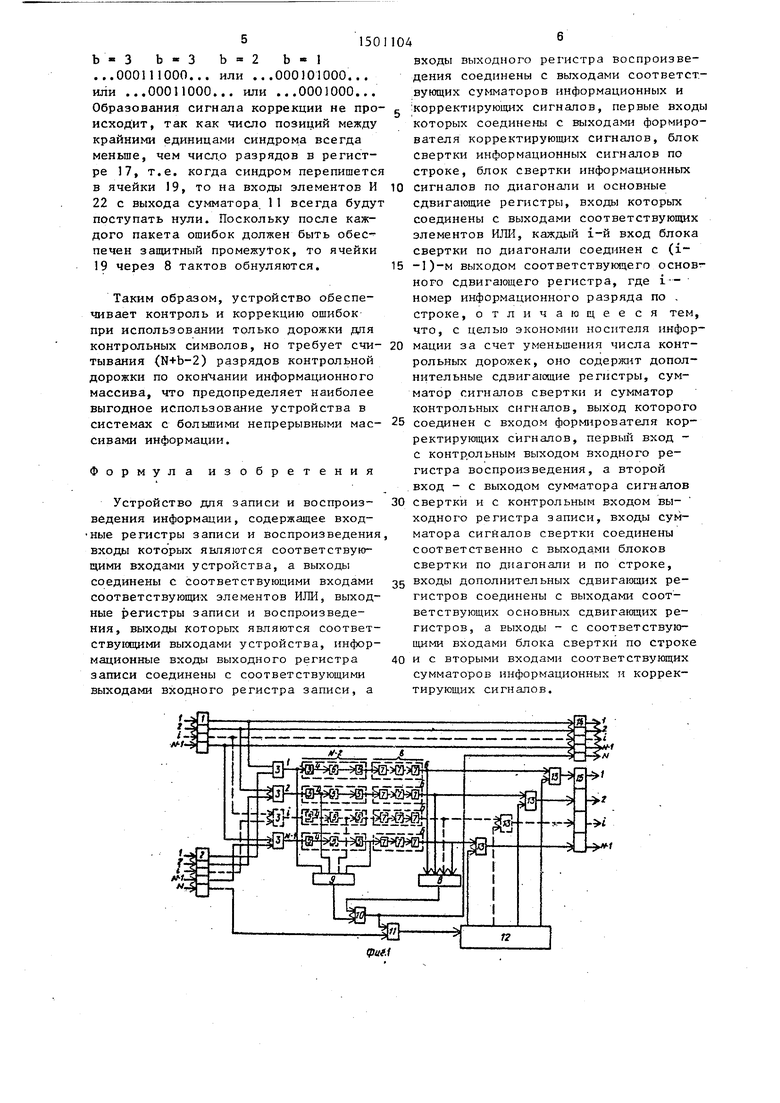

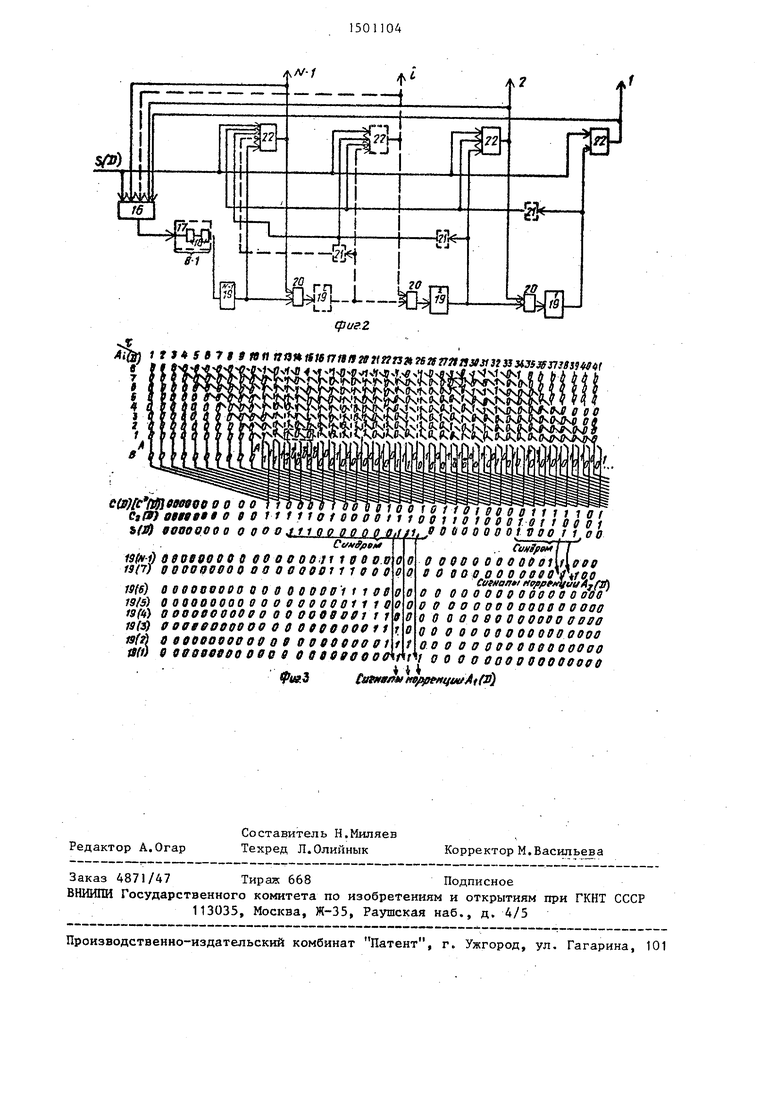

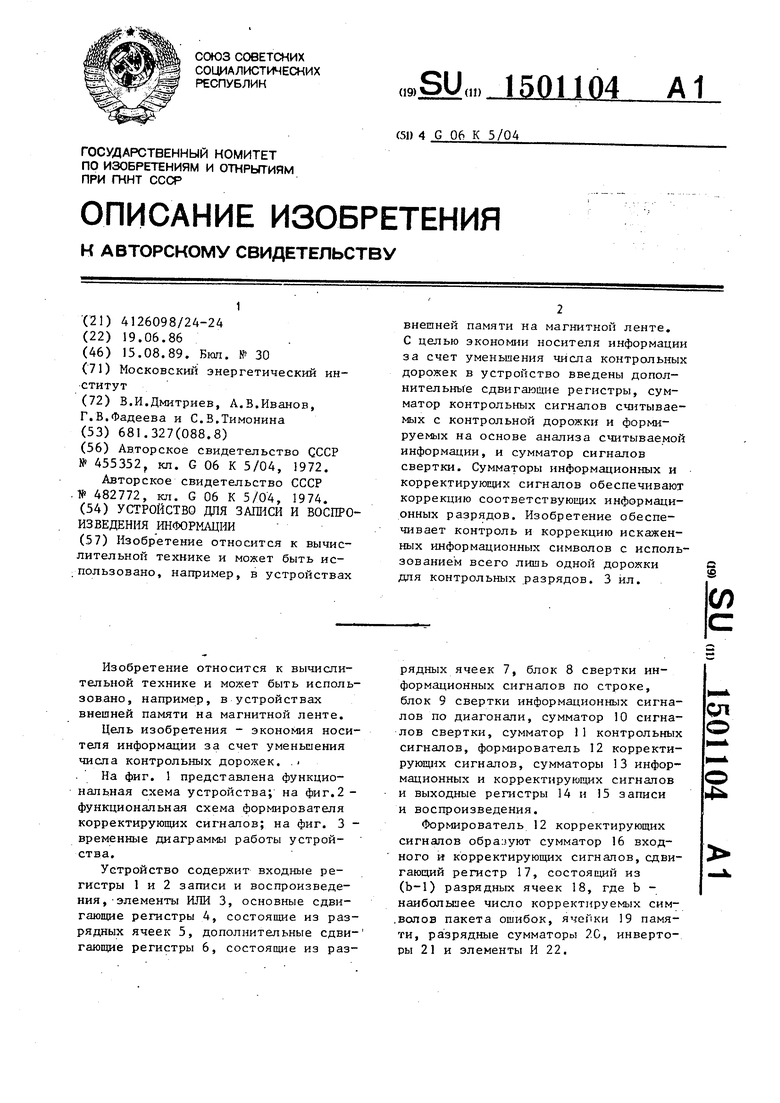

Цель изобретения - экономия носителя информации за счет уменьшения числа контрольных дорожек. . . На фиг. 1 представлена функциональная схема устройства; на фиг.2 - функциональная схема формирователя корректирующих сигналов; на фиг. 3 - временные диаграммы работы устройства.

Устройство содержит входные регистры 1 и 2 записи и воспроизведения, -элементы ИЛИ 3, основные сдвигающие регистры 4, состоящие из разрядных ячеек 5, дополнительные сдви- гающие регистры 6, состоящие из разрядных ячеек 7, блок 8 свертки информационных сигналов по строке, блок 9 свертки информационных сигналов по диагонали, сумматор 10 сигналов свертки, сумматор 11 контрольных сигналов, формирователь 12 корректирующих сигналов, сумматоры 13 информационных и корректирующих сигналов и выходные регистры 14 и 15 записи и воспроизведения.

Формирователь 12 корректирующих сигналов обра; уют сумматор 16 входного и корректирующих сигналов, сдвигающий регистр 17, состоящий из (Ь-1) разрядных ячеек 18, где b - наиболыиее число корректируемых сим- ,волов пакета ошибок, ячейки 19 памяти, разрядные сумматоры .С, инверторы 21 и элементы И 22.

сл

о

3150

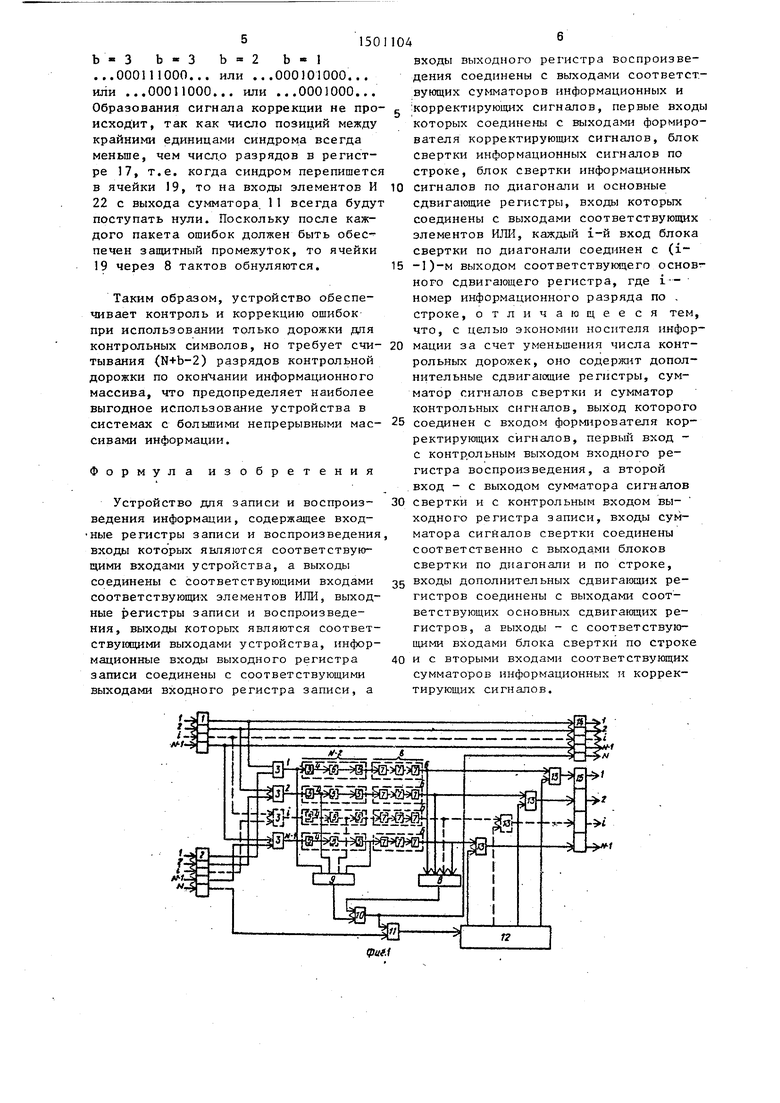

На фиг. 3 представлены временные диаграммы для случая восьмиразрядного входного информационного сигнала А;(В) в различные моменты 1-41 вре- мени.

Устройство работает следующим образом.

Работу устройства рассмотрим на примере исправления пакета ошибок

в девятидорожечном () накопителе на магнитной ленте, в котором 8 дорожек - информационные, а одна- контрольная. На фиг. 3 показано расположение информации на магнитной ленте в каждом такте З ; .

3 режиме код 1рования на каждом такте - на вход блока 1 поступает 8-разрядное слово. До прихода первого ненулевого слова все ячейки бло- ков 4 и 6 находятся в нулевом состо- янии. Рассмотрим образование символов контрольной последовательности, Символы В на выходе блока 8 получают сложением по модулю два всех разря- дов информационного слова. Символы на выходе блока свертки 9 получают сложением по модулю два всех разрядов диагонали. Символы на выходе блока 8 свертки по строке образуют последовательность, которая обозначена на фиг. 3 буквой В, а символы на выходе блока 9 свертки по диагонали образуют последовательность, обозначенную на фиг. 3 буквой А.

Если сдвинуть символы последовательности В на (N-2+b)10 тактов и сложить ее с последовательностью А, то получают контрольные символы С (D), подлежащие записи на девятую конт- рольную дорожку.

На фиг. 3 до прихода первого ненулевого слова последовательность C(D) состоит из одних нулей и, чтобы не загромождать рисунок, обрГазовани последовательности А показано с момента времени -},

В резкиме декодирования образование последовательности C(D) по принятым возможно с ошибками, симво- лам считанных слов производится так же, как и в режиме кодирования. Предположим, что пакеты ошибок возникли так, как показано на фиг. 3 (пакеты ошибок обведены пунктиром), В последовательностях А и В позиции отличающиеся от позиций для случая кодирования, отмечены звездочкой. В результате получают новую последовательность C(D), обозначенную на фиг. 3 C(D). Поскольку ошибки на контрольной дорожке отсутствуют, то контрольная последовательность C(D), считанная с девятой дорожки, совпадает с последовательностью C(D). После сложения по модулю два последовательностей C(D) и C(D) на выходе сумматора 11 получают последовательность синдромов ошибки S(D), которая поступает на вход блока 12.

Символы, соответствующие символам синдрома ошибки S(D), через сумматор 16 (по модулю два) синхронно с продвижением 8-разрядных слов по буферным регистрам 4 и 6 передвигаются по регистру 17 и далее вдоль ячеек 19 памяти. Число разрядов регистра 17 равно . Число ячеек 19 памяти (N- -1)8. На фиг, 3 показано продвижение символов синдрома вдоль 8-разрядного регистра, состоящего из ячеек 19i с учетом задержки в регистре 17.

Одновременно сигналы синдрома S(D) подаются на один из входов элементов И 22. Символы синдрома S(D), отличные от кгуля, достигают ячейки 19 первого разряда на 23-м такте, в котором на вход блока 12 поступает единичный символ синдрома S(D), воздействующий на элементы И 22. Однако сигнал коррекции возникает только на выходе элемента И 22, связанного с сумматором 13 коррекции первого разряда, так как сигнал на выходе ячейки 19 памяти первого разряда через инвертор 21 запрещает образование сигнала коррекции на выходах элементов И 22 других разрядов.

В момент времени 23 сигнал коррекции первого разряда в сумматоре 16 складывается с соответствующим сигналом единицы синдрома S(D), который далее в регистр 17 не поступает. Описанный процесс формирования сигналов коррекции повторяется для случая Ь 3 три раза. Так как после каждого формирования сигнала коррекции в регистр 17 поступают нули, то ячейки 19 также nocTerteHHO обнуляются.

Если возникает пакет ошибок Ъ-2 на седьмой дорожке, то сигнал коррекции формируется на выходе ячейки 19 седьмого разряда.

В случае возникновения ошибок на контрольной дорожке для случая могут возникнуть следующие конфигура- ,ции синдромов:

(puf.i

94 50

, У t

tfue.Z

71 9пп fffi isief7aatfft ffr3 f6ffi7aaiffjf3t333 3s 373 8s},( ------ .|1, 5,

l pvlfчl lKl 9 Ж(rvN.вчй

.t(.rчJNt Kffч %

J.((

..1мкКЛчК(

о в XNtkiN fsev Ms sMf

IK((

cfff fc fiaSJffi eff 0000

. {0, 01 III IQf

Caff) 09П9 0 в ff 1 1 t 1 1 0 t DO 0 0 t 1 1 0 0 1 I 0 f 0 00 to { i 0 0 el

в 0 00 0 Q 0 Ot VJOt1ob CoMf/ffftl I

0 00000 0 0 ooonAgoo s 0 00в 000 ffoea fo,o

Coenarr neppftt)tuuAt

л

00000000000 0 000 0 о 0 00 0 OOOO 0 0OOO

a te/fn m/3f HtfoitAtfS}

000 0 0 00 0 0 0 0 O I/ Q 0 0 0 00

. {0, 01 III IQf

0 t 1 1 0 0 1 I 0 f 0 00 to { i 0 0 el

Coenarr neppftt)tuuAt

л

3f HtfoitAtfS}

00000000000 0 000 0 о 0 00 0 OOOO 0 0OOO

0 a 0 во 000000ooso

000 0 0 0 00000 0000 00 0 0 0 0 OO 0 OOOOOOOO I/ Q 0 0 0 000 0 QQOOOOOO

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Устройство для обнаружения и коррекции ошибок памяти | 1986 |

|

SU1377918A1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1989 |

|

SU1649615A1 |

Изобретение относится к вычислительной технике и может быть использовано, например, в устройствах внешней памяти на магнитной ленте. С целью экономики носителя информации за счет уменьшения числа контрольных дорожек в устройство введены дополнительные сдвигаеющие регистры, сумматор контрольных сигналов, считываемых с контрольной дорожки и формируемых на основе анализа считываемой информации, и сумматор сигналов свертки. Сумматоры информационных и корректирующих сигналов обеспечивают коррекцию соответствующих информационных разрядов. Изобретение обеспечивает контроль и коррекцию искаженных информационных символов с использованием всего лишь одной дорожки для контрольных разрядов. 3 ил.

| Устройство для исправления ошибок при параллельном считывании двоичной информации | 1972 |

|

SU455352A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для записи и воспроизведения информации | 1974 |

|

SU482772A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1986-06-19—Подача