1

Устройство для исправления ошибок ири иараллельном считывании двоичной информации .относится к области вычнслительиои техншсн и может быть использовано в устройствах записи - восиропзведенкя двончиой ниформацнн.

Известиое устройство для исиравлення оиш.бок при параллельном считьшапии двопчиой ииформацни по авт. св. 292175 позволяет исправлять искаженные символы, расположен.пые на несколькнх дорожках иоснтеля, путем .добавлепня контрольных снмволов но строке П диагонали.

Однако ири некоторых вариантах расиоложення нскаженных символов оно может осу.ществлять ложиые «иснравлення иеискажен.ных символов.

Цель изобретения - новышенне эффективиости коррекнии .

Это достигается тем, что в устройство введены схемы «НЕ, входы которых подключены к выходам ячеек памяти, а выходы - к соответствующнм входам схем «И.

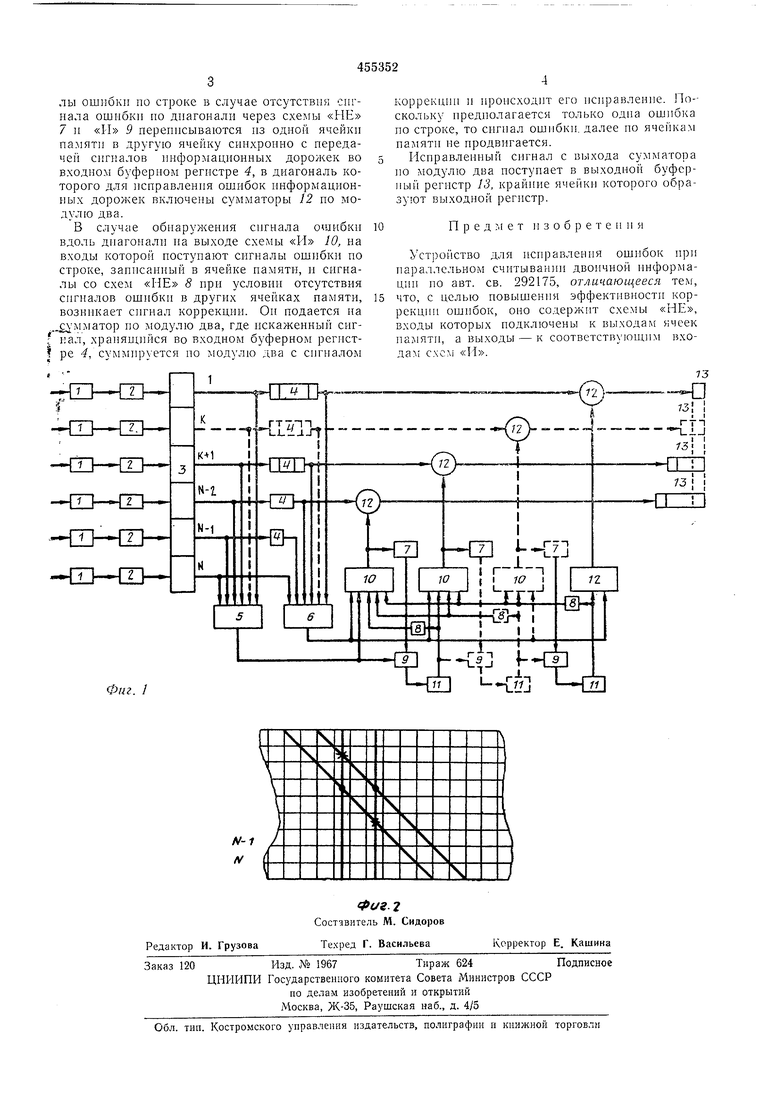

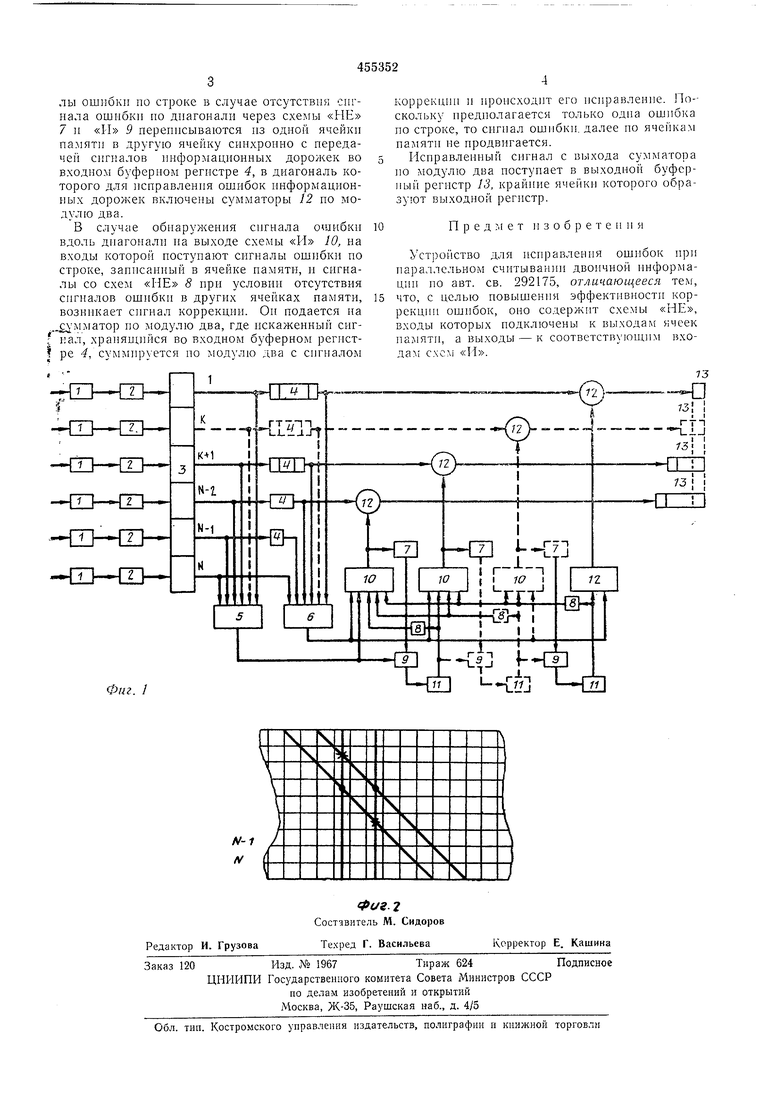

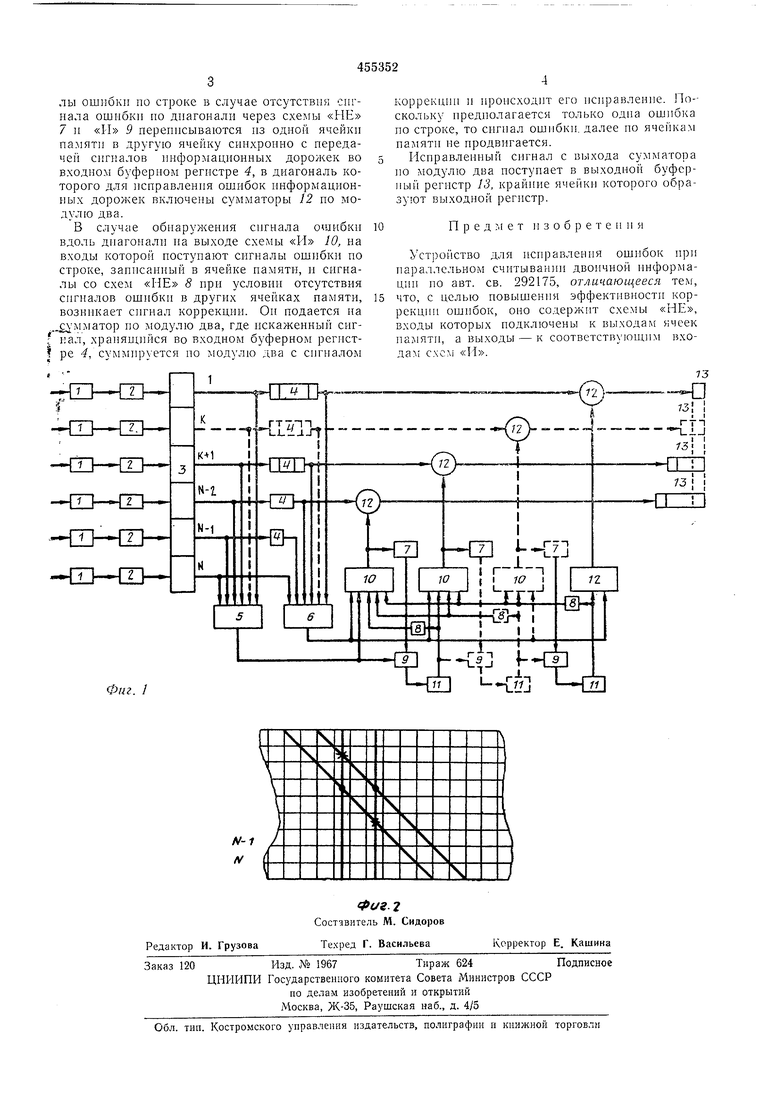

На фиг. 1 представлена функциональная схема иредлагаемого устройства для исправ.ления ошибок при параллельном считывании двоичной информации; на фнг. 2 - одти. из возможных вариантов расиоложепня неискаженных символов, нриводяианй к ошибочному 11злгепеи1ио неискаженных символов при коррекции в известном устройстве (жирными точками указаны искаженные символы, а крестиками - неискаженные, которые изменяются по результатам проверки па четность по cтpoкa ; и диагоналям).

Устройство (фиг. 1) содержит считывающие головки 1, усилители 2 восироизведения, входной регистр 3, входной буферный регистр 4. схему 5 свертки по модулю два по строке, схел:у 6 свертки по модулю два по диагонали, схемы «НЕ 7 и 8, схемы «И 9 п 10, ячейки 11 памяти, сумматоры 12 по модулю два, выходиой буферный регистр 13.

Выходы ячеек И иамяти подключены к входам схем «НЕ 5, выходы каждой из которых соединены с входами схем «И 10 данного разряда н более старших разрядов.

Устройство работает следуюшнм образом.

Снгналы, воснринятые считываюш,нми головками / с информационных (1-N-2) п доиолнительиых (.V-1, Л ) дорожек носителя через усилители 2 воспропзведення заппсываются во входной регистр 3. С поступлением каждой новой строкп спгналы ннформацноппых дорожек предыдущпх строк переппсыва10ТСЯ в ячейки входного буферного регистра -. О.аи.овременно проводится контроль по модул о два спгнала вдоль строкн (включая спгпал с дорожки по диагонали) с иомощью схемы 5 I вдоль диагонали благодаря схеме 6. Сигналы ошиоки по строке в случае отсутствия сигнала ошибки ио диагонали через схемы «НЕ 7 и «И 9 иереписываются из одной ячейки памяти в другую ячейку сиихроино с иередачей сигналов ииформациоиных дорожек во входном буфериом регистре 4, в диагональ которого для исправления ошибок информационных дорожек включены сумматоры 12 но модулю два.

В случае обиаружения сигнала ошибки вдоль диагонали на выходе схемы «И 10, на входы которой ностуиают сигналы ошибки ио строке, заннсаиный в ячейке намятн, и сигналы со схем «НЕ 8 при условии отсутствия сигналов ошибки в других ячейках памяти, возникает сигнал коррекции. Ои подается иа мматор но модулю два, где искаженный сигнал, храияищйся во входном буферном регистре 4, суммируется ио модулю два с сигиалом

коррекции и ироисходит его исиравление. Поскольку нреднолагается только одна ошибка ио строке, то сигнал ошнбкн. далее ио ячейкам памяти не иродвигается.

Нсправленный сигнал с выхода сумматора ио модулю два иостуиает в выходной буферный регистр 13, крайние ячейки которого образуют выходиой регистр.

Н р е д м е т и з о б р е т е и и я

Устройство для исиравлення ошибок при параллельном считывании двоичной ниформацнн по авт. св. 292175, отличающееся тем, что, с целью повышения эффективности коррекции ошибок, оно содержит схемы «Ht, входы которых подключены к выходам ячеек памяти, а выходы - к соответствуюнд.им входам схем «И.

Авторы

Даты

1974-12-30—Публикация

1972-06-18—Подача