nf

to ю

3 . 150 Изобретение относится к телемеханике и может использоваться в телеметрических системах.

Целью изобретения является расширение функциональных возможностей устройства за счет организации предварительного выбора адресов временных каналов.

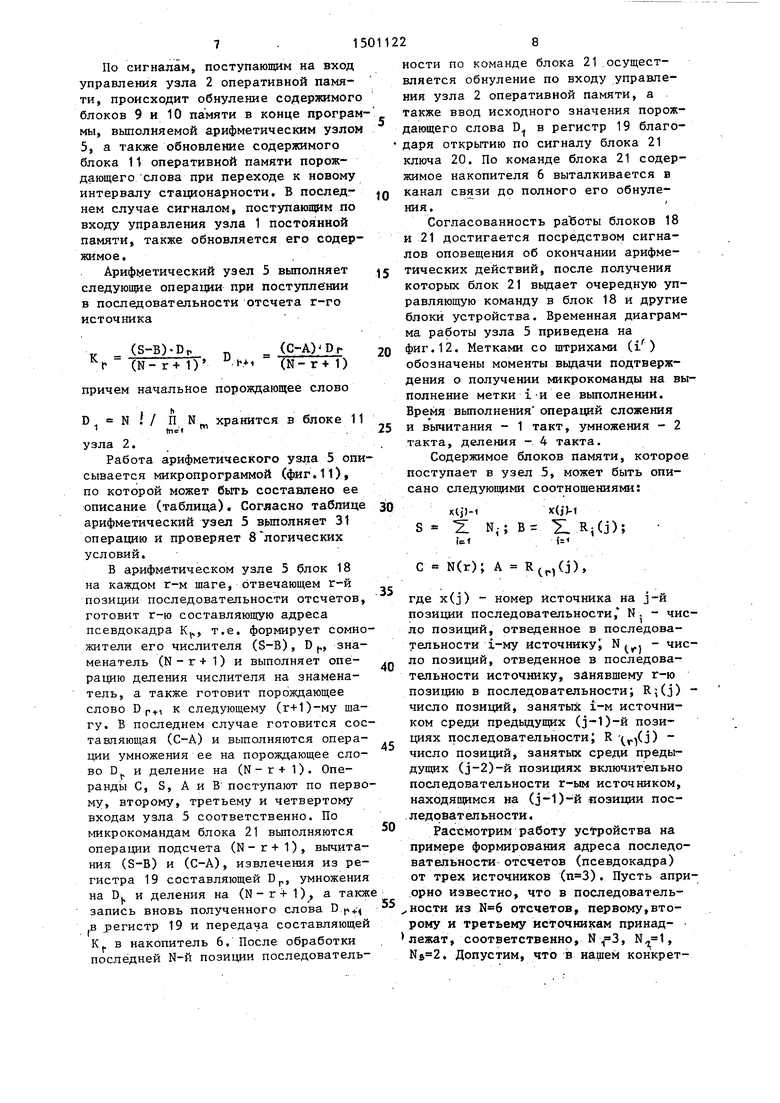

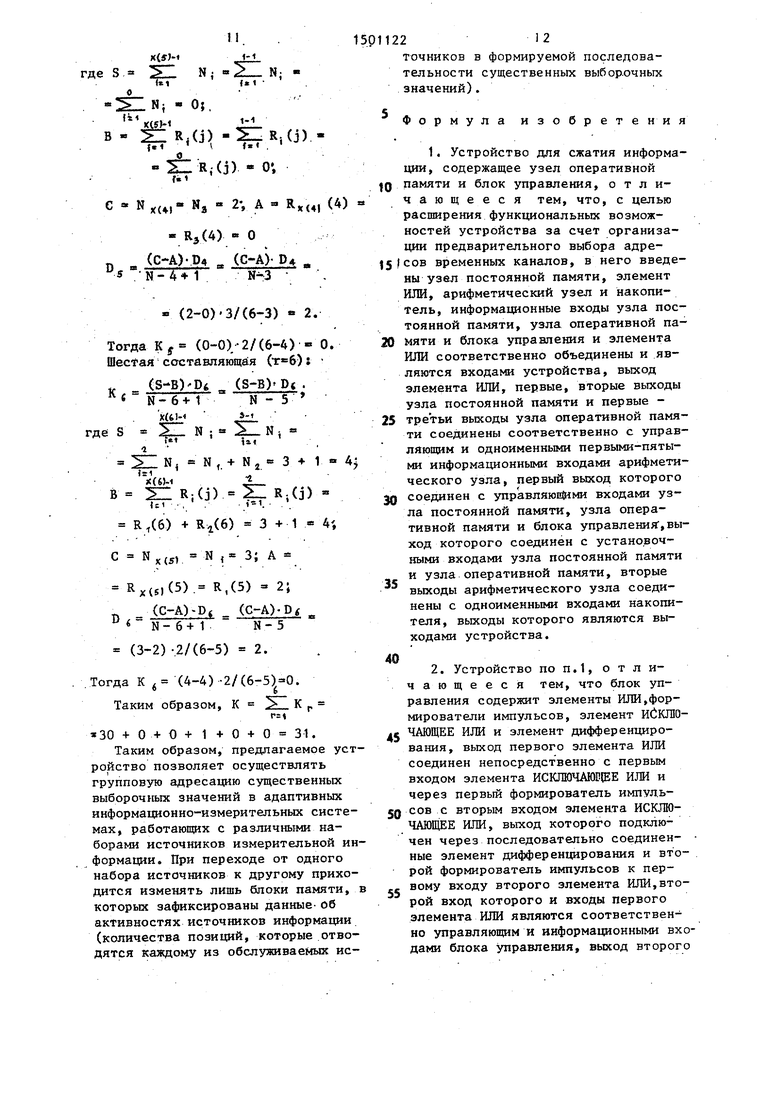

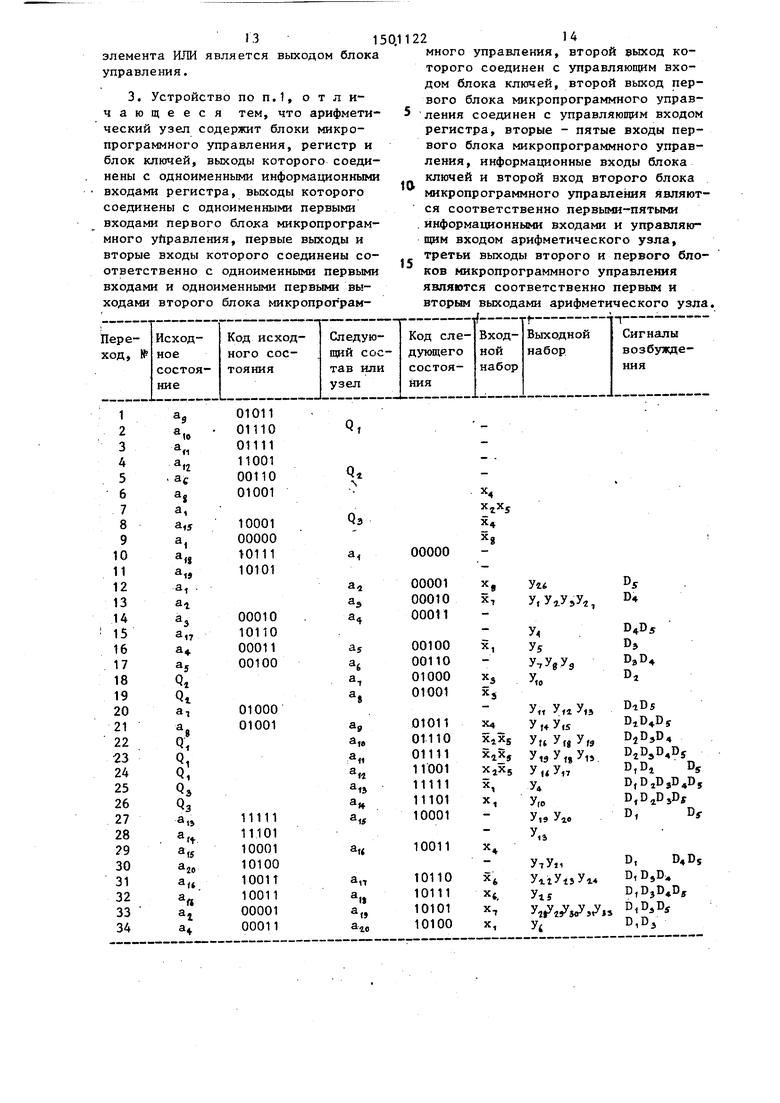

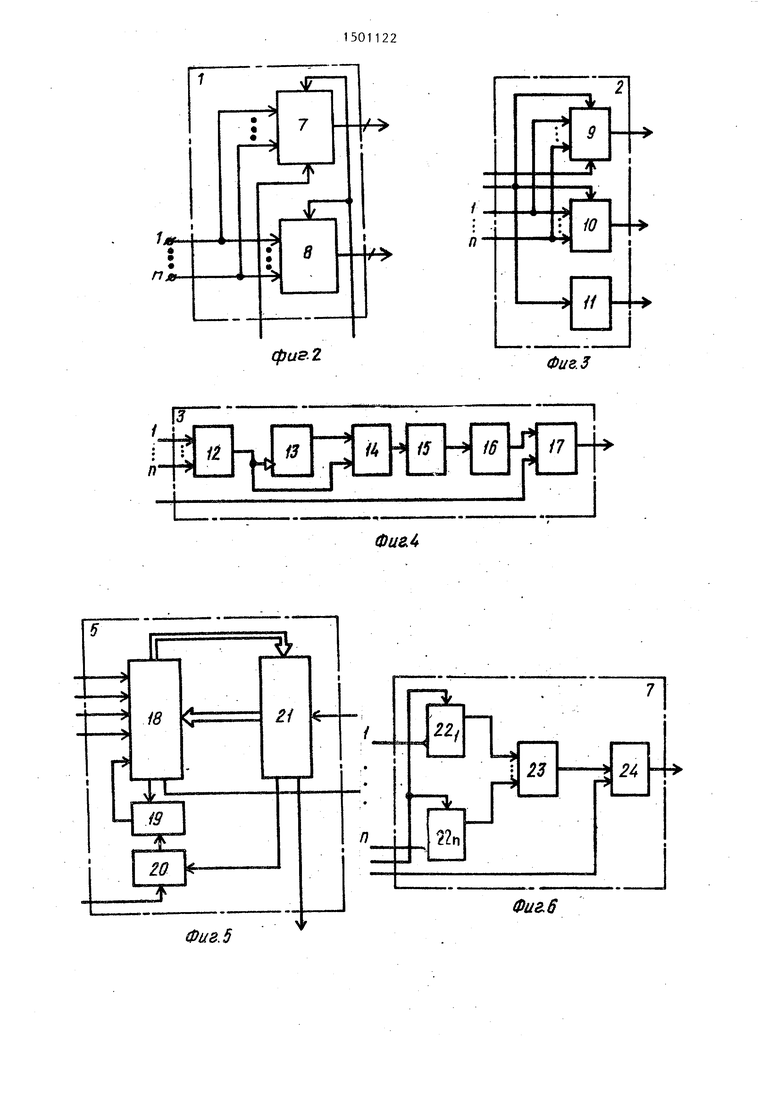

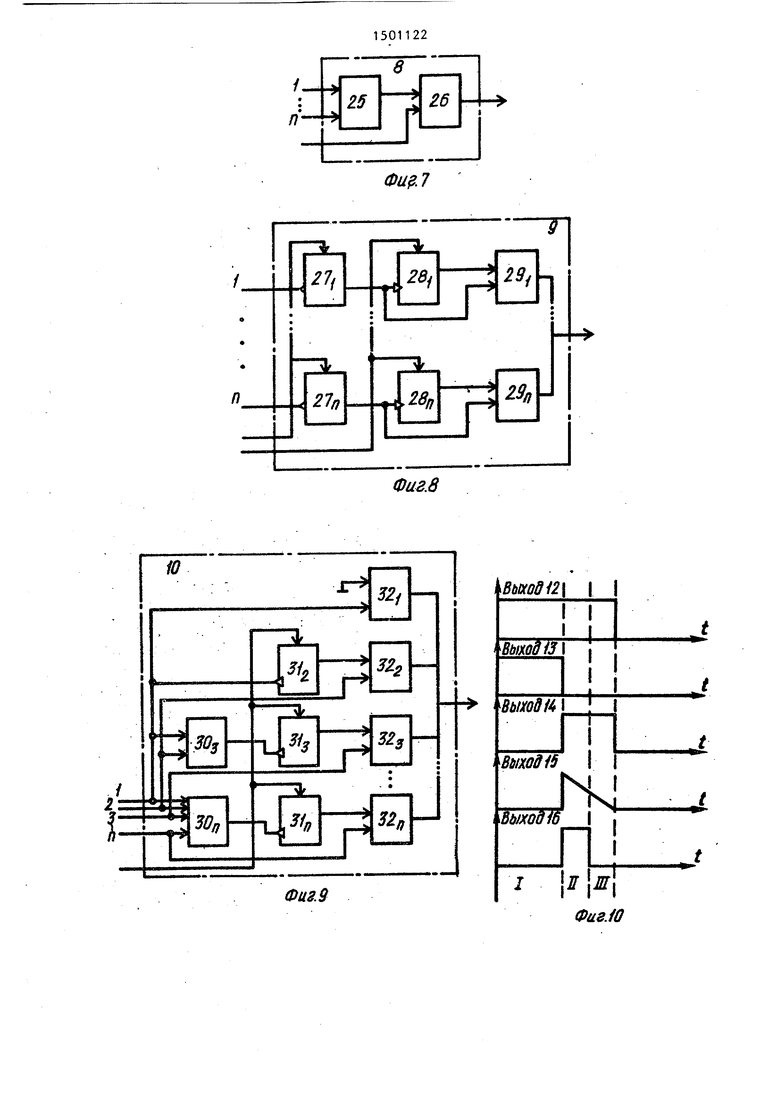

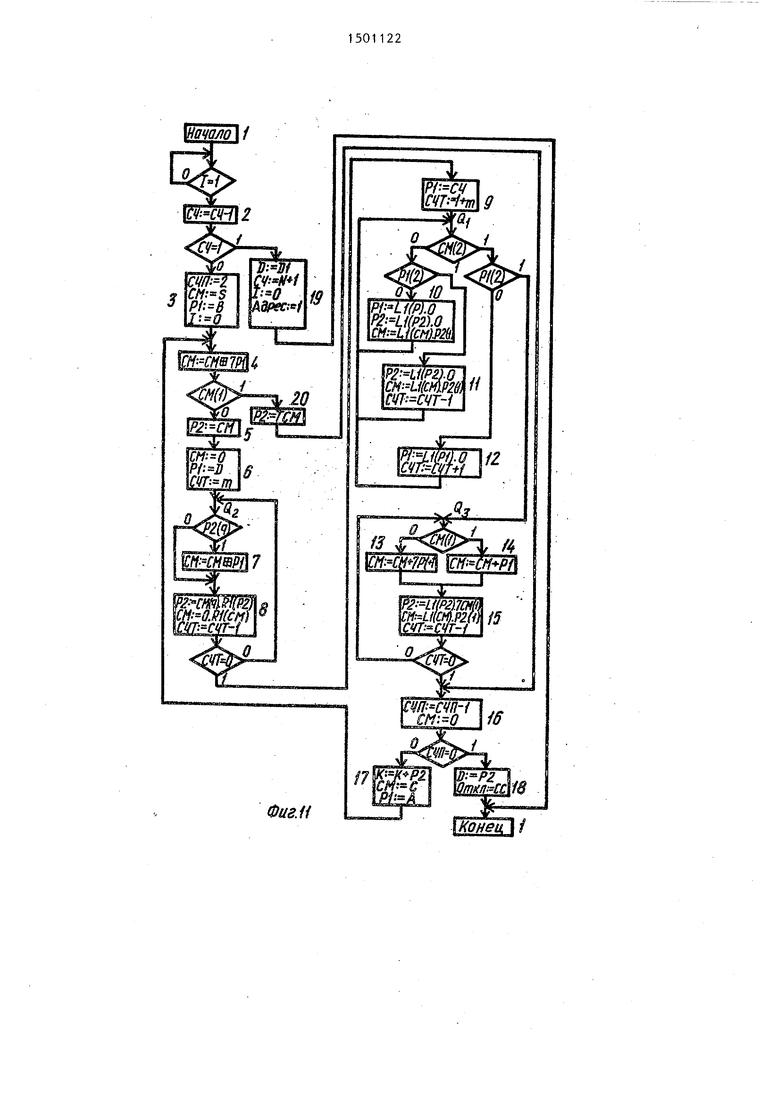

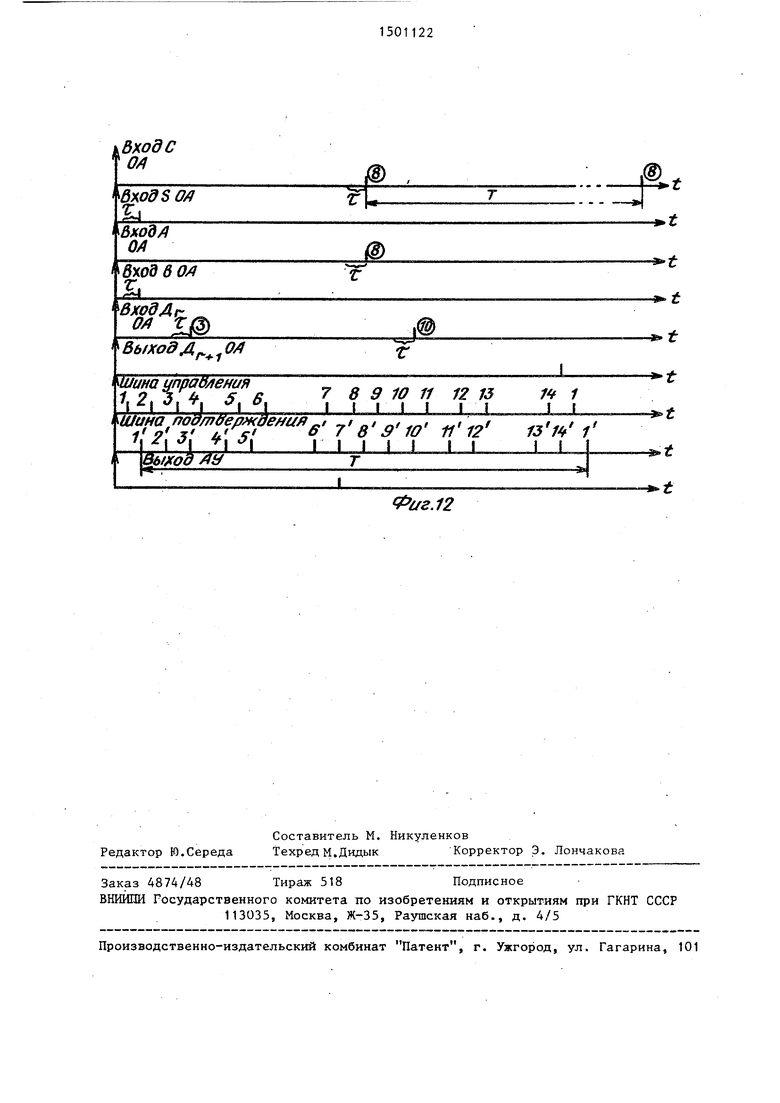

На фиг.1 представлена структурная схема предлагаемого устройстваj на фиг.2 - функциональная схема узла постоянной памяти; на фиг.З - функциональная схема узла оперативной памяти; на фиг.4 - функциональная схема блока управления , на фиг ..5 - функциональная схема арифметического узла; на фиг. 6 и 7 - функциональные схемы блоков постоянной памяти ; на фиг. 8 и 9 - функциональные схемы блоков оперативной памяти, на фиг.10 - временные диаграммы работы блока управления; на фиг. t1 и 12 - блок-схема микропрограммы, временные диаграммы работы арифметическо- го узла.

Устройство содержит (фиг.1) узел 1 постоянной памяти, узел 2 оперативной памяти, блок 3 управления, элемент ИЛИ 4, арифметический узел 5 и накопитель 6. Узел 1 постоянной памяти (фиг.2) вьшолнен на блоках 7 и 8 постоянной памяти. Узел 2 one- |ративной памяти (фиг.З) выполнен на блоках 9-11 оперативной памяти.Блок 3 управления (фиг.4) вьшолнен на первом элементе ИЛИ 12, первом формирователе 13 импульсов, элементе ИСКЛЮЧАЮВЩЕ .ИЛИ 14, элементе 15 дифференцирования, втором формировател 16 импульсов и втором элементе ИЛИ 17. Арифметический узел 5-(фиг.5) выполнен на первом .блоке 18 микропрограммного управления, регистре 19 памяти, блоке 20 ключей и втором блоке 21 микропрограммного управления. Блок 7 постоянной памяти (фиг.6 выполнен на триггерах 22 -22 „, шифраторе 23 и элементе 24 постоянной памяти. Блок 8 постоянной памяти (фиг.7) выполнен на шифраторе 25 и элементе 26 постоянной памяти. Блок 9 оперативной памяти (фиг.8) вьшолнен на триггерах 27 ,-27, счетчиках 28,-28 импульсов и регистрах 29 ,- 29 памяти. Блок 10. оперативной па- мяти (фиг.9) вьшолнен на элементах ИЛИ 30,-30, счетчиках 31-1-31 ь импульсов и регистрах 32,-32„ памяти

5 0 5

О Q , 0

5

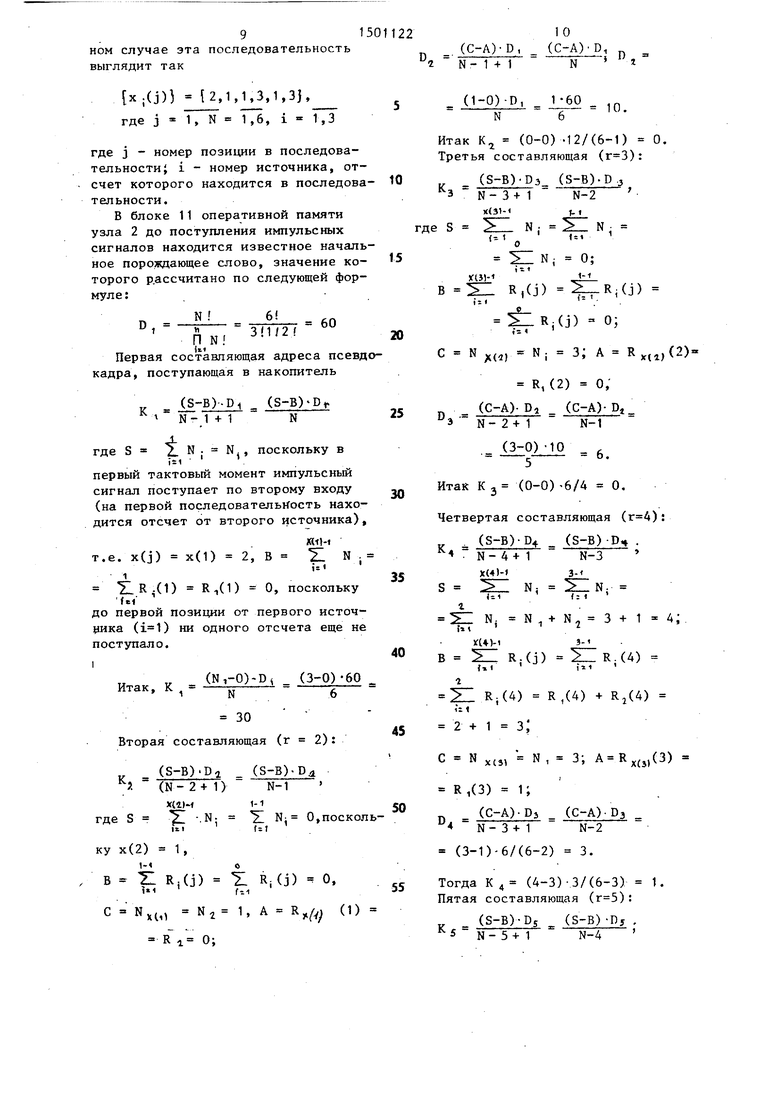

На фиг.12 приняты следующие обозначения: Т - цикл вь1числений (отрезок времени между двумя последовательными идентичными метками i) , f- время задержки между появлением сигналов на входах блока 18 относительно сигналов блока 21 их вызывающих. Кроме того, приняты следующие обозначения меток: 1 - ввод S и В; 2 - вычисление (S-B), 3 - ввод D, 4 - вычисление (S-B) D.., 5 - подсчет I

(N-r+1); 6 - подсчет К 7 - ввод К в накопитель; 8 - ввод Си А; 9 - вьиисление (С - А), 10 - ввод Dpj 11 - вычисление (С - A) 12 - ввод (N-r+1); 13 - подсчет Dp, (C-A)(N-г+ 1); 14 - ввод D в регистр 19 порождающего слова.

В таблице представлено описание микропрограммы работы арифметического узла 5.

Устройство работает следующим образом.

В каждый тактовый момент на один из входов (1,2,...,п) устройства,соответствующий каналу, отсчет которого передается в данный тактовый момент, поступает импульс к узлу 1. постоянной памяти, узлу 2 оперативной памяти, блоку 3 управления и через элемент ИЛИ 4 на арифметический узел 5 в качестве сигнала запуска. В течение тактового интервала арифметический узел 5 вычисляет очередное слагаемое группового адреса, текущее значение которого хранится в накопителе 6. При этом в соответствующие микротакты узел 5 вводит из узла 1 и узла 2 необходимые для вычислений операнды. По окончании вычислений узел 5 добавляет значение полученного слагаемого адреса к содержимому накопителя 6. Предполагается, что последовательности отсчетов длины N на интервале стационарности содержат фиксированное число отсчетов каждого из источников .сообщений, соответственно N ,, N,j, ...,N , которые могут быть расположены в последовательности отсчетов в произвольном порядке. В блоках 7 и 8 постоянной памяти записаны константы N,, N,..., (операнд С)

П-1

и О, N , N, + N,,... 1 N.(onekti

51

ранд S). Импульс, поступивший в i-й тактовый момент на k-й вход устройства вводит по первым и вторым входам арифметического узла 5 констанir

ты NI, и 4- N ; соответственно. По

jrl J

сигналу, 11оступающему на вход управления узла 1, происходит смена констант, хранимых в узле 1 при переходе к новому интервалу стационарности.

В блоке 9 оперативной памяти узл 2 хранятся текущие значения количества отсчетов каждого из источников, поступивших за время с начала последовательности до текущего мо

мента: N

(т(

N

(т)

,...,N J (операнд А), а в блоке 10 памяти хранятся костанта О и переменные N , N 7 +

(операнд В). Пр

+ N

(Т)

(Т)

1(

/

2 ,..., I N

kri

поступлении в блок 3 управления отсчета по k-му каналу (,n) через элемент ИЛИ 12 запускается формирователь 13, вырабатывающий импульс длительностью, меньший, чем у импульса, поступившего по k-му каналу при этом на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 - нуль, по заднему фронту импульса с выхода формирователя 13 на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ U устанавливается 1, по которой элемент 15 дифференцирования и формирователь 16 формируют импульс, задний фронт которого оканчивается раньше, чем задний фронт импульса, поступившего по k-му каналу, и который подается на первый вход элемента ИЛИ 17, а через него - на выход блока 3 управления. В блоке 7 постоянной памяти до начала работы все триггеры 22 находятся в нулевом состоянии. При поступлении первого отсчета по k-му каналу он записывается в триггер 22) по заднему фронту. При поступлении следующего отсчета по 1-му каналу на выходе блока 7 памяти сохраняется содержимое k-ой ячейки элемента 24 постоянной йамяти, т.е. N х- При появлении на выходе элемента ИЛИ 17 блока 3 управления импульса обнуления (фиг. 10.Jj триггер 22j, обнуляется, а по заднему фронту 1-й отсчет записывается в триггер 22, т.е. при поступлении следующего отсчета по т-му каналу на выходе блока 7 памяти сохраняется число N.j, и так далее.

5

0

5

0

5

0

5

0

5

0

226

В блоке 8 памяти при поступлении отсчета до k-му каналу на выходе блока 8 появляется содержимое k-й ячейки элемента 26 постоянной памяти, т.е. число N + ... + N,, а если отсчет пришел по первому каналу - то число О и так далее.

В блоке 9 оперативной памяти до начала работы все триггеры 27 и счетчики 28 находятся в нулевом состоянии. При поступлении первого отсчета по k-му каналу он записывается в триггер 27j. по заднему фронту. При поступлении следующего отсчета по 1-му каналу на выходе блока 9 памяти нулевой код, так как в счетчиках 28 записаны нули. При появлении импульса на выходе блока 3 управления триггер 27г обнуляется, а содержимое счетчика 28| увеличивается на единицу, по заднему фронту отсчет записывается в Триггер 27р. При поступлении третьего отсчета по т-му каналу на выходе блока 9 нулевой код, триггер 27 обнуляется, содержимое счетчика 280 увеличивается на единицу, а отсчет т-го канала записывается в триггер 27. При повторном поступлении следующего отсчета по mr-му каналу триггер 27m обнуляется, содержимое счетчика 28 х увеличивается на единицу, а отсчет по заднему фронту вновь записывается в триггер 27. При поступлении следующего отсчета по т-му каналу только в триггере будет записана единица, поэтому поскольку

в счетчике 28 записано число

1, на

5

выходе блока 9 памяти также число 1, то при обнулении триггера 27 содержимое счетчика 28 „, увеличивается на единицу, а в триггер 27гп вновь записывается единица, т.е. блок 9 памяти содержит и т.д.

В блоке 10 оперативной памяти до начала работы все счетчики 31 нахо- . дятся в нулевом состоянии. При пос. туплении отсчета по k-му каналу по заднему фронту он увеличивает содержимое счетчиков 31 J, на единицу, поскольку в счетчиках 31..-31„ записаны числа 1, то при поступлении отсчета по 1-му каналу через регистр 32 р на выход блока 10 выво- ., дится содержимое счетчика 31, далее содержимое счетчиков 31, -31 f,, увеличивается на единицу, т.е. блок 10

л- памяти содержит число 2- N

7 . 15

По сигналам, поступающим на вход управления узла 2 оперативной памяти, происходит обнуление содержимого блоков 9 и 10 памяти в конце программы, вьшолняемой арифметическим узлом 5, а также обновление содержимого блока 1t оперативной памяти порождающего слова при переходе к новому интервалу стационарности. В послед- нем случае сигналом, поступающим по входу управления узла 1 постоянной памяти, также обновляется его содержимое.

Арифметический узел 5 выполняет следующие операции при поступлении в последовательности отсчета г-го источника

(S-B)-Dt (N-r+1)

(С-А) D f.

Т) л 20 (N-r+1)

причем начальное порождающее слово

. ь D N / П N хранится в блоке 11

узла 2.

Работа арифметического узла 5 описывается микропрограммой (фиг.11), по которой может быть составлено ее описание (таблица). Согласно таблице арифметический узел 5 вьшолняет 31 операцию и проверяет 8 логических условий.

в арифметическом узле 5 блок 18 на каждом г-м шаге, отвечающем г-й позиции последовательности отсчетов, готовит г-ю составляющую адреса псевдокадра К,,, т.е. формирует сомножители его числителя (S-B), D, знаменатель (N - г+ 1) и выполняет операцию деления числителя на знаменатель, а также готовит порождающее слово Dp, к следующему (г+1)-му шагу. В последнем случае готовится составляющая (С-А) и вьшолняются операции умножения ее на порождающее слово D, и деление на (N-r+ 1). Операнды С, S, А и В поступают по первому, второму, третьему и четвертому входам узла 5 соответственно. По микрокомандам блока 21 выполняются операции подсчета (N - г + 1), вычитания (S-B) и (С-А), извлечения из регистра 19 составляющей Dp, умножения на D. и деления на (N-r+1), а также запись вновь полученного слова Dp+r в регистр 19 и передача составляющей К., в накопитель 6. После обработки последней N-й позиции последователь

28

ности по команде блока 21.осуществляется обнуление по входу управления узла 2 оперативной памяти, а также ввод исходного значения порождающего слова D в регистр 19 благо- даря открытию по сигналу блока 21 ключа 20. По команде блока 21 содержимое накопителя 6 выталкивается в канал связи до полного его обнуления.

Согласованность раТботы блоков 18 и 21 достигается посредством сигналов оповещения об окончании арифметических действий, после получения которых блок 21 вьщает очередную управляющую команду в блок 18 и другие блоки устройства. Временная диаграмма работы узла 5 приведена на фиг.12. Метками со штрихами () обозначены моменты выдачи подтверждения о получении микрокоманды на выполнение метки i-и ее выполнении. Время вьтолнения операций сложения и вычитания - 1 такт, умножения - 2 такта, деления -. 4 такта.

Содержимое блоков памяти, которое поступает в узел 5, может быть описано следующими соотнощениями:

xtj -i x( S - Z N.; B Ri(j);

id

(

О

5

0

С N(r); A R,(j),

где x(j) - номер источника на j-й позиции последовательности, N. - число позиций, отведенное в последовательности i-му источнику - число позиций, отведенное в последовательности источнику, занявшему г-ю повидаю в последовательности; R;(j) - число позиций, занятых i-м источником среди предыдущих (л-1)-й позициях последовательности; R-(j) - число позиций, занятых среди предыдущих (j-2)-й позициях включительно последовательности г-ым источником, находящимся на (3-1)-й нозиции пос- .ледовательности,

Рассмотрим работу устройства на примере формирования адреса последовательности отсчетов (псевдокадра) от трех источников (). Пусть априорно известно, что в последователь ности из отсчетов, первому,второму и третьему источникам принад лежат, соответственно, N ,3, , , Допустим, что is нашем кон крет9

ном случае эта последовательность выглядит так

txj(j))

где j 1, N 1,6, i 1,3

где j - номер позиции в последовательности J i - номер источника, отсчет которого находится в последовательности.

В блоке 11 оперативной памяти узла 2 до поступления импульсных сигналов находится известное начальное порождающее слово, значение которого рассчитано по следующей формуле:

N 6

D,

60

ъ П N

1ч

Первая составляющая адреса псевдокадра, поступающая в накопитель К

(S-B)-D (S-B) Dt. N- 1 + 1 N

где S X N I N,, поскольку в

первый тактовый момент импульсный сигнал поступает по второму входу (на первой последовательность находится отсчет от второго источника),

«tbi т.е. x(j) х(1) 2, В 11 N .

1 И R-(1) Ri(1) О, поскольку

f.i

до первой позиции от первого источника () ни одного отсчета еще не поступало.

Итак, К

(N,-0)-D (3-0)-60

N

30

Вторая составляющая (г 2): К,

(S-B)-Da (S-B)-Dd (N- 2+1)N-1

JtdlM1-1

где S -.N- N 0,посUl

КУ x(2) 1, i-

fit

В Г Ri(j) H Rj(j) . 0.

U1f-1

Ni 1, A 0;

R,

(1)

10

n (C-A)-D. (C-A) D, D N- 1+ 1N

(V-o)-. l::6o 10

N6

Итак K, (0-0) .12/(6-1) 0. Третья составляющая ():

(5-В)-Рз (S-B).D.3 3 N- 3+ 1N-2

X(

где S N i N ,

f-- f-- V

)f(J)-i

В

С N д(.г, N i

N; 0;

I . 1

R,(j) ,(j)

Rj(j) 0;

3; A R,i,(2). R, (2) 0,

5

0

5

n XC-A)- D7 (C-A)- Dt 3- N-2+1N-1

(3-0)-10 , 5- -

Итак К 3 (0-0) -6/4 0,

Четвертая составляющая ();

V - (S-B)-D4 (З-В)-РЧ . - N - 4 +1

N-3 3S

г

fit

X(4l-

Nj N , + N,, 3 + 1

N, N,

4;

3-1

R:(4)

)ft4)-i

B R,(j)

0

ZI Ri(4) R,(4) -b Rj(4) I j 1

С N

хся

N, 3; A R,,,.(3)

- Ri(3) 1;

D

(c-A)-Di (С-А)-РЗ

- N- 3 + 1N-2

(3-1)-6/(6-2) 3.

55

Тогда К 4 (4-3)-3/(6-3) 1. Пятая составляющая ():

1. (S-B)-DS (s-B)-nj .

N-5+ 1

N-4

м

де S,Jt4

х(ы

,Ni .

Ni 0;,

f:

i«i

1-1

N: f;X(J)

- i:R,-(j) « o;

f«

R-,(j) N

XUI

N,

2-, А

Х(4|

(4)

ал 4)

(С- А)-р4

N-4+1

(С-А)- D4 „

N-3

« (2-0) 3/(6-3) 2.

Тогда К у « (0-0) -2/(6-4) - 0. Шестая составляющая ()i

К

де S «

(5 -В)-Рб N- 6+ 1

XUM

«5

-«

Х(.1

В SI

N,.+

(S-B) D . N - 5

5-t .

SlN, - Ui

Nj 3 +

s

Ri(j)

R ,(6) + Ri(6)

i.

R-.Cj)

N

X(5

N

3 + 1 « 4, 3; A

R

(5).

x(s). R,(5)

(C-A)-Dt N- 6+ 1

2;

(C-A)-D N-5

(3-2) -.2/(6-5) 2.

.Тогда К (4-4) 2/(6-5)0.

Таким образом, К

5lK,

«30 + 0 + 0 + 1 +0 + 0 31.

Таким образом, предлагаемое устройство позволяет осуществлять групповую адресацию существенных выборочных значений в адаптивных информационно-измерительных системах, работающих с различными наборами источников измерительной информации. При переходе от одного набора источников к другому приходится изменять лишь блоки памяти, в которых зафиксированы данные-об активностях источников информации (количества позиций, которые отводятся каждому из обслуживаемых ис150112212

ТОЧНИКОВ в формируемой последовательности существенных выборочных значений).

Формула изобретени

5

0

0

1.Устройство для сжатия информации, содержащее узел оперативной памяти и блок управления, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет организации предварительного выбора адресов временных каналов, в него введены узел постоянной памяти, элемент ИЛИ, арифметический узел и накопитель, информационные входы узла постоянной памяти, узла оперативной памяти и блока управления и элемента ИЛИ соответственно объединены и являются входами устройства, вьпсод элемента ИЛИ, первые, вторые выходы узла постоянной памяти и первые 5 третьи выходы узла оперативной памяти соединены соответственно с управляющим и одноименными первыми-пятыми информационными входами арифметического узла, первый выход которого соединен с управляю1ф1ми входами узла постоянной памяти, узла оперативной памяти и блока управления, выход которого соединен с установочными входами узла постоянной памяти и узла оперативной памяти, вторые выходы арифметического узла соединены с одноименными входами накопителя, выходы которого являются выходами устройства.

0

2.Устройство по п.1, о т л ичающееся тем, что блок управления содержит элементы ИЛИ,формирователи импульсов, элемент ИСКШОе ЧАЮЩЕЕ ИЛИ и элемент дифференцирования, выход первого элемента ИЛИ соединен непосредственно с первым входом элемента ИСКЛЮЧАЮБ1ЕЕ ИЛИ и через первый формирователь импуль0 сов с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен через последовательно соединен- ные элемент дифференцирования и второй формирователь импульсов к пер, вому входу второго элемента ИЛИ,второй вход которого и входы первого элемента ИЛИ являются соответственно управляющим и информационными входами блока Управления, выход второго

5

элемента ИЛИ управления.

13150.1

является выходом блока

3. Устройство по П.1, отличающееся тем, что арифметический узел содержит блоки микропрограммного управления, регистр и блок ключей, выходы которого соединены с одноименными информационными входами регистра, выходы которого соединены с одноименными первыми входами первого блока микропрограммного управления, первые выходы и вторые входы которого соединены соответственно с одноименными первыми входами и одноименными первыми выходами второго блока микропрог рам

a

5

2214

много управления, второй эыход которого соединен с управляющим входом блока ключей, второй выход первого блока микропрограммного управления соединен с управляющим входом регистра, вторые - пятые входы первого блока микропрограммного управления, информационные входы блока ключей и второй вход второго блока микропрограммного управления являются соответственно первыми-пятыми информационными входами и управляющим входом арифметического узла, третьи выходы второго и первого блоков микропрограммного управления являются соответственно первым и вторым выходами арифметического узла.

Фив. 5

ЛI

f

Л

26

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для обработки массивов данных | 1985 |

|

SU1293737A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство для формирования широкополосного случайного процесса | 1986 |

|

SU1432514A1 |

| Вычислительное устройство для ранговой фильтрации | 1989 |

|

SU1656554A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для анализа распределений случайных процессов | 1986 |

|

SU1517040A1 |

Изобретение относится к телемеханике и может использоваться в телеметрических системах. Изобретение позволяет расширить функциональные возможности устройства за счет организации предварительного выбора адресов временных каналов. Устройство осуществляет кодирование адреса равномерным блочным кодом в реальном масштабе времени, причем длина двоичного слова определяется априорно известным для данного интервала кусочной стационарности распределением активностей совокупности обслуживаемых источников. Устройство содержит узел 1 постоянной памяти, узел 2 оперативной памяти, блок 3 управления, элемент ИЛИ 4, арифметический узел 5 и накопитель 6. 2 з.п.ф-лы, 12 ил.

Фиг.8

ашо 1

IS

Ш-чмшт

а

К - СтЩЩ,

CH: OMCMi

m-sMii

Фиг.а

..,

CM-UfCM)P26l

(P2).0

Ci/T CVr4

//

j

n-5iL/M

1шш

fmG

(

Щ.

. ЖШ(Щ 15

W- ,.-.

Конец /

Фиг.12

| Бородин Н.И | |||

| Импульсные устройства на морском транспорте | |||

| М.: Транспорт, 1987, с | |||

| Аппарат для нагревания окружающей его воды | 1920 |

|

SU257A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Устройство для сжатия информации | 1981 |

|

SU959125A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1989-08-15—Публикация

1988-01-18—Подача