Изобретение относится к автомати-: ке и вычислительной технике и может быть использовано в устройствах управления очередностью обслуживания.

Цель изобретения - повьшение до- стоверности работы устройства за счет исключения потери запросов с длительностью, меньшей длительности цикла чтения устройства,

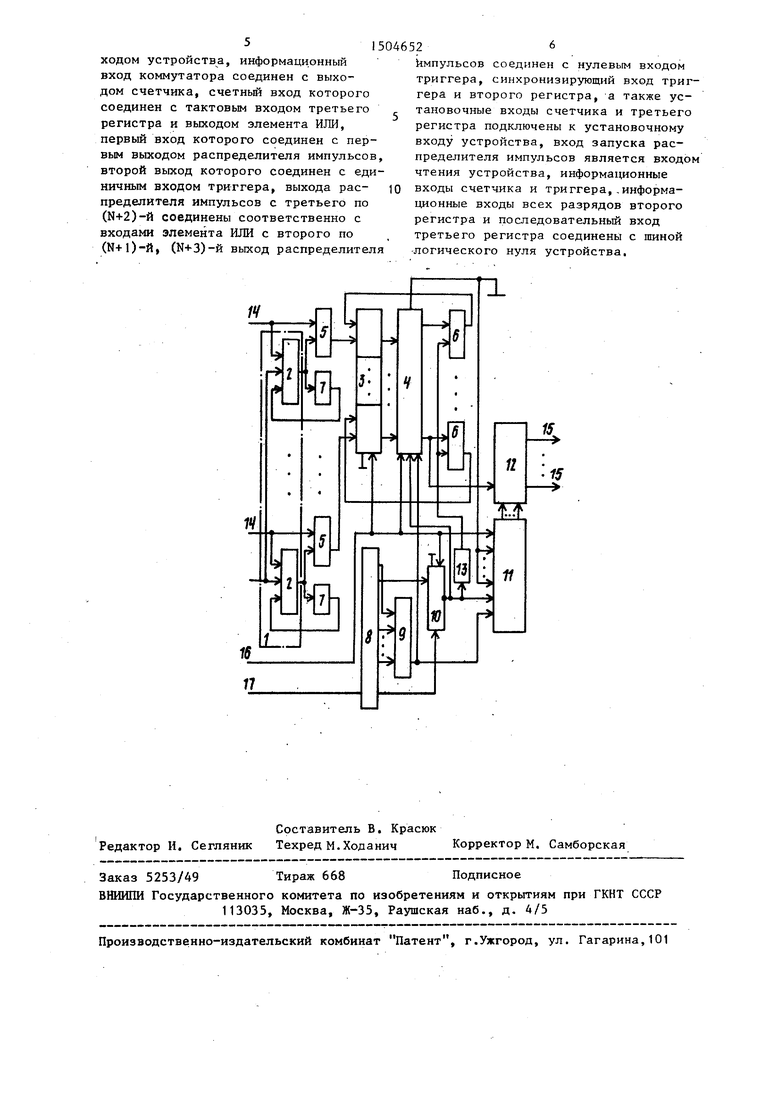

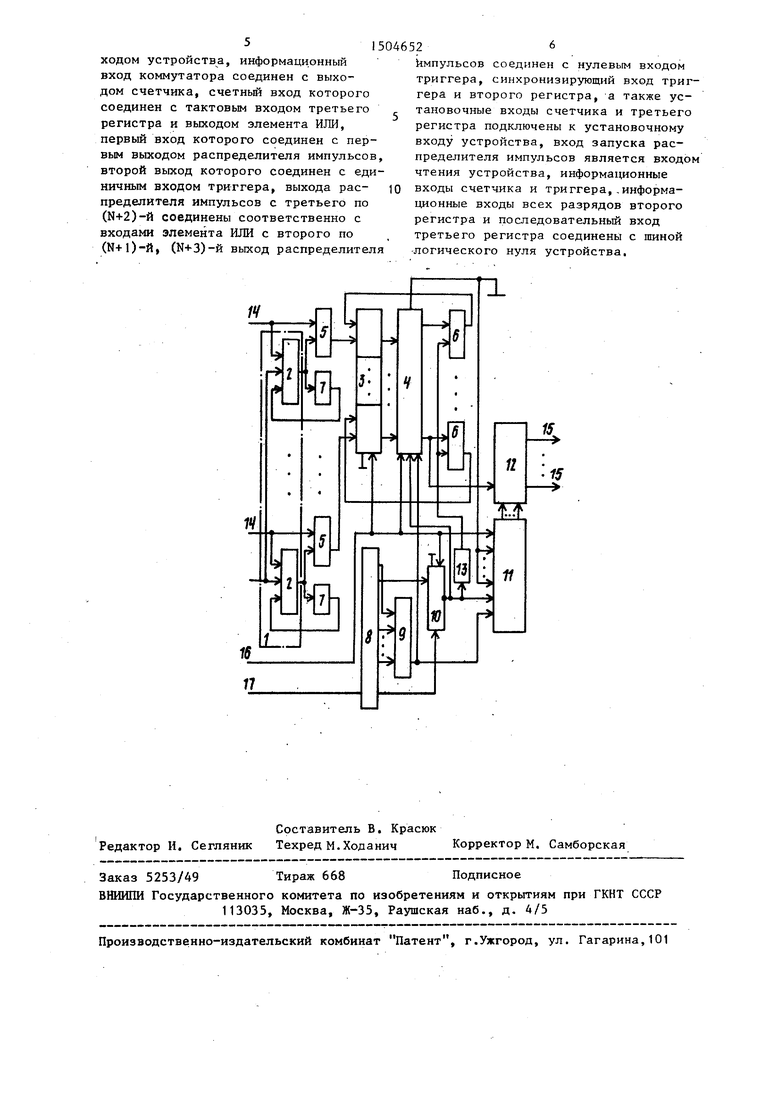

На чертеже представлена схема устройства.

Устройство содержит первый регистр 1,с триггерами 2, второй и третий регистры 3 и 4, первую группу элементов И 5, вторую группу элементов И 6, элементы задержки 7, распределитель импульсов 8, элемент ИЛИ 9, триггер 10, счетчик П, коммутатор 12, формирователь импульсов 13, группу запросных входов 14 устройст- а, группу информационных выходов 15 устройства, установочный вход 16 устройства и вход 17 чтения устройства.

Устройство работает следующим образом,

В исходном состоянии регистры 3 и 4, триггер 10 и счетчик Л1 обнулены. Обнуление производится единичным импульсом по входу 16 устройства. Разряды регистра I обнуляются автоматически через элементы задержки 7. Засд

9

сл

fO

3.150

просы на обслуживание поступают по входам 14 устройства, фиксируются в триггерах 2 регистра 1 и через элементы И 5 устанавливают в единицу соответствующие разряды регистра 3, Приоритет запросов возрастает с возрастанием порядкового номера запроса. Элементы И 5 предотвращают срабатывание регистра 3 при появлении на входах 14 кратковременной единичной помехи, Помехой считается сигнал длительность Которого меньше времени срабатывания триггера 2, Помеха установит в единицу один из триггеров 2, но через время, определяющееся величиной элемента задержки, триггер 2 возвратится в исходное состояние, Так как триггер 10 обнулен, то регистр 4 и счетчик 11 находятся в ре- жиме ожидания параллельного приема информации, заданном единицей с инверсного выхода триггера 10. По тактовому входу 17 устройства поступают импульсы чтения. Рассмотрим один такт чтения устройства. По переднему фронту импульса чтения запускается распределитель импульсов 8. Импульс с его первого выхода через элемент ИЛИ 9 поступает на тактовые входы регистра 4 и счетчика 11, По переднему фронту этого импульса содержимое регистра 3 переписывается в регистр 4, а в счетчик 11 заносится нулевое значение. Если в регистр 4 записался запрос наивысшего приоритета, то единица с N-ro выхода регистра 4 открывает коммутатор 12 и на выходы 15 устройства из счетчика 11 вьдается код наивысшего приоритета, Затем импульсом со второго выхода распределителя импульсов 8 устанавливается в единицу триггер 10, сигнал с инверсного выхода которого переводит регистр 4 в режим сдвига инфор мации,. а счетчик II - в режим счета. Кроме того, формирователь 13 вырабатывает единичный импульс, которьй проходит через элементы И 6 и сбрасывает только те разряды регистра 3, из которых в регистр 4 переписалась единица. Следующие N импульсов, поступающие через элемент ИЛИ 9 с выходов распределителя импульсов 8, последовательно сдвигают информацию в регистре 4 и прибавляют единицу к содержимому счетчика 11. Если в i-M разряде регистра 4 была единица, то на выходы 15 устройства из счетчика 11 через коммутатор 12 будет выдан код i-ro запроса. Регистр 4 после окончания каждого цикла чтения будет обнулен, (N+3)-M импульсом с выхода распределителя импульсов 8 триггер 10 устанавливается в нуль.

Следующие циклы чтения происходят аналогично.

Формула изобретения

Устройство для организации очереди, содержащее первый регистр, первую группу из N элементов И (где N - число запросных входов устройства, первый элемент задержки, распределитель импульсов, элемент ИЛИ и счетчик, причем первый вход каждого i-ro элемента И первой группы (i 1,N) соединен с i-м запросным входом устройства, второй вход i-ro элемента И первой группы соединен с выходом i-ro разряда первого регистра, отличающееся тем, что, с целью повьшения достоверности работы устройства за счет исключения потери запросов с длительностью, меньшей длительности цикла чтения.уст- ройства, в него введены N-1 элементов задержки, второй и третий регистры, вторая группа из N элементов И, триггер,,формирователь, импульсов и коммутатор, причем i-й синхронизирующий вход первого регистра соединен с i-M запросным входом устройства, i-й информационный вход первого регистра соединен с шиной питания устройства, i-й нулевой вход через i-й элемент задержки подключен к выходу i-ro разряда первого регистра, выход i-ro элемента И первой группы соединен с единичным входом i-ro разряда второго регистра, нулевой вход i-ro разряда которого соединен с выходом i-ro элемента И второй группы, выход i-ro разряда второго регистра соединен с i-M информационным входом третьего регистра, выход i-ro разряда которого соединен с первым входом i-ro элемента И второй группы, выход N-ro разряда третьего регистра соединен с управляющим входом коммутатора, вторые входы всех элементов И второй группы объединены и соединены с выходом формирователя импульсов, вход которого соединен с инверсным выходом триггера и входами управления записью третьего регистра и счетчика, выход коммутатора является выходом устройства, информационный вход коммутатора соединен с выходом счетчика, счетньй вход которого соединен с тактовым входом третьего регистра и выходом элемента ИЛИ, первый вход которого соединен с первым выходом распределителя импульсов, второй выход которого соединен с единичным входом триггера, выхода рас- пределителя импульсов с третьего по (Н+2)-й соединены соответственно с входами элемента ИЛИ с второго по (Н+1)-й (Ы+3)-й выход распределителя

46526

импульсов соединен с нулевым входом триггера, синхронизирующий вход триггера и второго регистра, а также ус- тановочные входы счетчика и третьего регистра подключены к установочному входу устройства, вход запуска распределителя импульсов является входом чтения устройства, информационные входы счетчика и триггера,.информационные входы всех разрядов второго регистра и последовательный вход третьего регистра соединены с шиной логического нуля устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритета | 1987 |

|

SU1439587A1 |

| Устройство для обслуживания запросов | 1986 |

|

SU1341639A1 |

| Асинхронное приоритетное устройство | 1986 |

|

SU1336002A1 |

| Устройство для обработки запросов | 1989 |

|

SU1688248A1 |

| Многоканальное устройство для обслуживания запросов в вычислительной системе | 1983 |

|

SU1140122A1 |

| Устройство управления прерываниями | 1982 |

|

SU1242948A1 |

| Многоканальное устройство для обслуживания запросов | 1986 |

|

SU1319034A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1986 |

|

SU1388863A1 |

| Устройство для контроля мультиплексоров | 1987 |

|

SU1511749A1 |

| Устройство для распределения заданий между ЭВМ | 1991 |

|

SU1777138A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах управления очередностью обслуживания. Целью изобретения является повышение достоверности работы устройства за счет исключения потери запросов с длительностью, меньшей длительности цикла чтения устройства. Устройство для организации очереди содержит два регистра хранения информации и сдвиговый регистр, две группы элементов И, группу элементов задержки, распределитель импульсов, триггер, элемент ИЛИ, формирователь импульсов, счетчик и коммутатор. В устройстве благодаря использованию сдвигового регистра для управления коммутатором осуществляется выдача на выходы устройства требуемого кода приоритета со счетчика, а применение группы элементов задержки и соединение синхровходов триггеров с входами устройства позволяет обрабатывать запросы любой длительности, причем исключено срабатывание устройства от кратковременных единичных помех. 1 ил.

| Устройство для управления очеред-НОСТью ОбСлужиВАНия зАпРОСОВ | 1979 |

|

SU851409A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для организации очередности приема информации | 1983 |

|

SU1128255A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-30—Публикация

1988-01-18—Подача