гг

.

Z532 да

Фиг

1508199

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных цифровых вычислительных системах, в част- ности в системах конвейерной обработки сигналов, предназначенных для зондирования окружающей среды.

Цель изобретения - расширение области применения за счет возможное- ю ти формирования функций с переменным шагом дискретности.

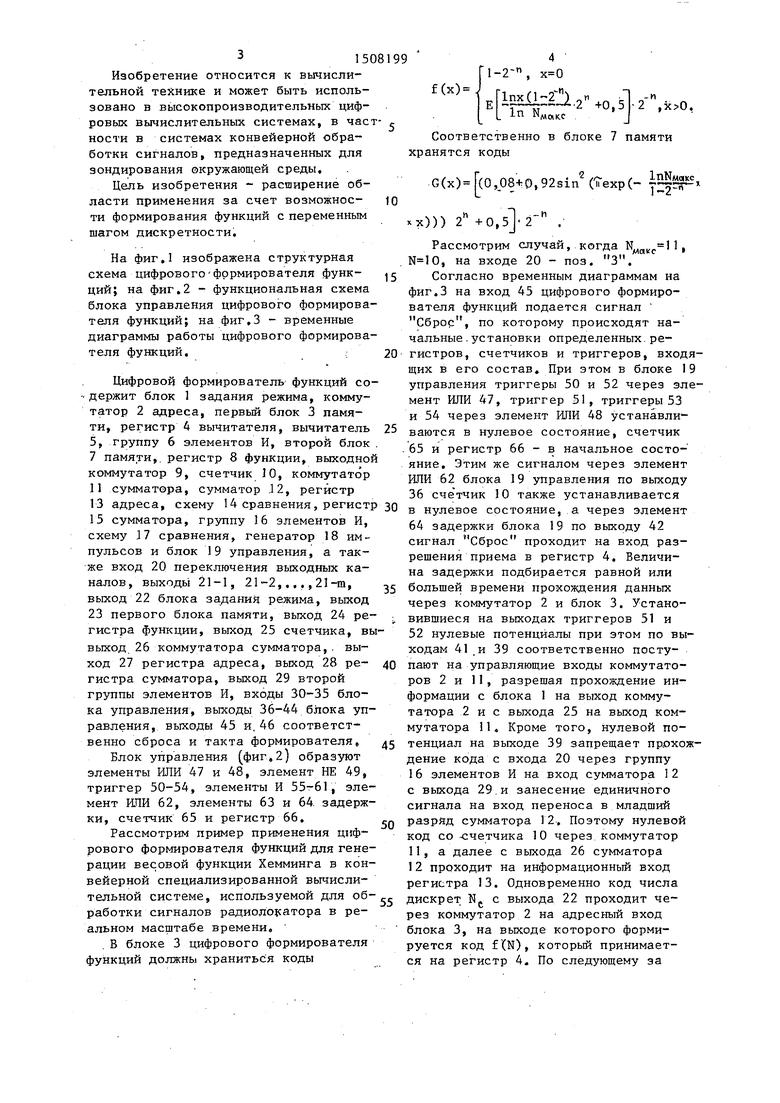

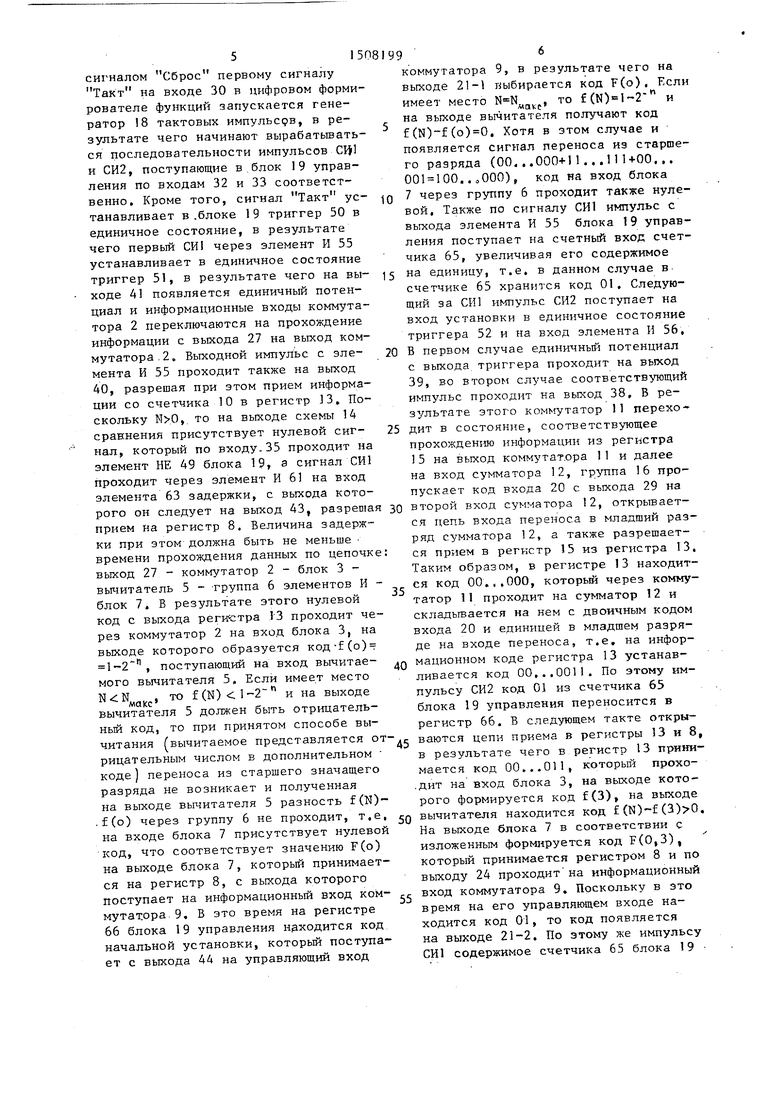

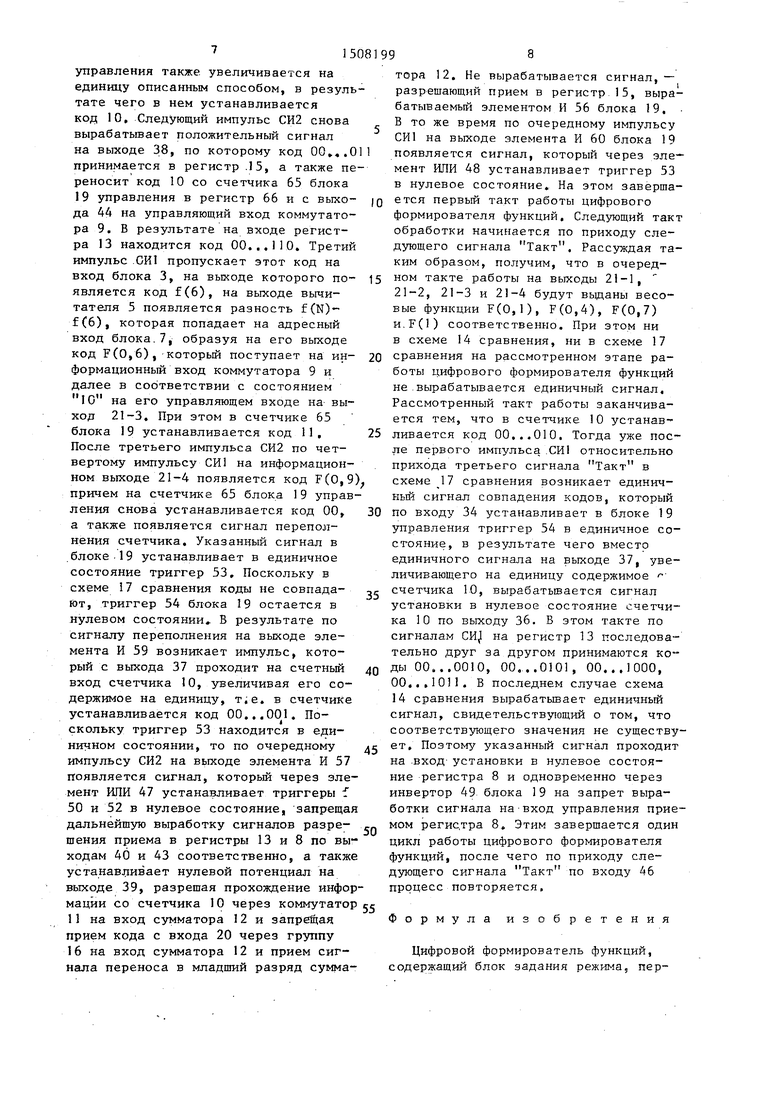

На фиг,I изображена структурная схема цифрового формирователя функ- ций; на фиг.2 - функциональная схема блока управления цифрового формирователя функций; на фиг.З - временные диаграммы работы цифрового формирователя функций.;

Цифровой формирователь функций со держит блок 1 задания режима, коммутатор 2 адреса, первый блок 3 памяти, регистр 4 вычитателя, вычитатель 5, группу 6 элементов И, второй блок 7 памяти,, регистр 8 функции, выходной коммутатор 9, счетчик 10, коммутатор 11 сумматора, сумматор J2, регистр 13 адреса, схему 14 сравнения, регистр 15 сумматора, группу 16 элементов И, схему J7 сравнения, генератор 18 импульсов и блок 19 управления, а также вход 20 переключения выходньпс каналов , выходы 21-1, 21-2,...,21-т, выход 22 блока задания режима, вьпсод 23 первого блока памяти, выход 24 регистра функции, выход 25 счетчика, вы выход 26 коммутатора сумматора,, выход 27 регистра адреса, выход 28 регистра сумматора, вькод 29 второй группы элементов И, входы 30-35 блока управления, выходы 36-44 блока управления, выходы 45 и,46 соответственно сброса и такта формирователя,

Блок управления (фиг,2) образуют элементы ИЛИ 47 и 48, элемент НЕ 49, триггер 50-54, элементы И 55-61, элемент ИЛИ 62, элементы 63 и 64. задержки, счетчик 65 и регистр 66.

Рассмотрим пример применения цифрового формирователя функций для генерации весовой функции Хемминга в конвейерной специализированной вычисли

тельной системе, используемой для об- дискрет N с выхода 22 проходит чеработки сигналов радиоло сатора в реальном масштабе времени,

В блоке 3 цифрового формирователя функций должны храниться коды

рез коммутатор 2 на адресный вход блока 3, на выходе которого формируется код fitN), который принимается на регистр 4. По следующему за

I-2-,

..2

L li N„(,,(0

+0,5|-2,,

Соответственно в хранятся коды

блоке 7 памяти

G(x)(0,),92siп(1rexp(- у 0.5.2-V

макс.

х))) 2 +

20

25 зо д

35

40

0

Рассмотрим случай, когда , на входе 20 - поз. 3.

Согласно временным диаграммам на фиг.З на вход 45 цифрового формирователя функций подается сигнал Сброс, по которому происходят начальные - установки определенных.регистров, счетчиков и триггеров, входящих в его состав. При этом в блоке 19 управления триггеры 50 и 52 через элемент ИЛИ 47, триггер 51, триггеры 53 и 54 через элемент ИЛИ 48 устанавливаются в нулевое состояние, счетчик .65 и регистр 66 - в начальное состояние. Этим же сигналом через элемент ИЛИ 62 блока 19 управления по выходу 36 сче тчик 10 также устанавливается в нулевое состояние, а через элемент 64 задержки блока 19 по выходу 42 сигнал Сброс проходит на вход разрешения приема в регистр 4. Величина задержки подбирается равной или большей времени прохождения данных через коммутатор 2 и блок 3. Установившиеся на выходах триггеров 51 и 52 нулевые потенциалы при этом по выходам 41 и 39 соответственно поступают на управляющие входы коммутаторов 2 и 11, разрешая прохождение информации с блока 1 на выход коммутатора 2 и с выхода 25 на выход коммутатора 11. Кроме того, нулевой потенциал на выходе 39 запрещает прохождение кода с входа 20 через группу 16 элементов И на вход сумматора 12 с выхода 29.и занесение единичного сигнала на вход переноса в младший разрйд сумматора 12, Поэтому нулевой код со -счетчика 10 через коммутатор 11, а далее с выхода 26 сумматора 12 проходит на информационный вход регистра 13. Одновременно код числа

дискрет N с выхода 22 проходит чедискрет N с выхода 22 проходит через коммутатор 2 на адресный вход блока 3, на выходе которого формируется код fitN), который принимается на регистр 4. По следующему за

сигналом Сброс первому сигналу Такт на входе 30 в цифровом формирователе функций запускается генератор 18 тактовых импульсрв, в результате чего начинают вырабатьшать- ся последовательности импульсов С1}1 и СИ2, поступающие в блок 19 управления по входам 32 и 33 соответственно. Кроме того, сигнал Такт устанавливает в .блоке 19 триггер 50 в единичное состояние, в результате чего первый СИ через элемент И 55 устанавливает в единичное состояние триггер 51, в результате чего на выходе 41 появляется единичный потенциал и информационные входы коммутатора 2 переключаются на прохождение информации с выхода 27 на выход коммутатора, 2. Выходной импульс с элемента И 55 проходит также на выход 40, разрешая при этом прием информации со счетчика 10 в регистр 13. Поскольку ,, то на выходе схемы 14 сравнения присутствует нулевой сигнал, который по входу.35 проходит на элемент НЕ 49 блока 19, а сигнал СИ1 проходит через элемент И 61 на вход элемента 63 задержки, с выхода котоМП ь с

на выходе вычнтателя получают код f(N)-f(o)0, Хотя в этом случае и появляется сигнал переноса из старшего разряда (00,..OOO+l1...111+00.,. ..оООО), код на вход блока

JQ 7 через группу 6 проходит также нулевой. Также по сигналу СИ1 импульс с выхода элемента И 55 блока 19 управления поступает на счетный вход счетчика 65, увеличивая его содержимое

15 на единицу, т.е. в данном случае в- счетчике 65 хранится код 01. Следующий за СИ1 импульс СИ2 поступает на вход установки в единичное состояние триггера 52 и на вход элемента И 56.

20 В первом случае единичный потенциал с выхода триггера проходит на выход 39, во втором случае соответствующий импульс проходит на выход 38. В результате этого коммутатор 11 перехо25 дит в состояние, соответствующее прохождению информации из регистра 15 на выход коммутат.ора 1 1 и далее на вход сумматора 12, группа 16 пропускает код входа 20 с выхода 29 на рого он следует на выход 43, разрешая зо второй вход сумматора 12, открывает- прием на регистр 8, Величина задерж- ся цепь входа переноса в младший разки при этом должна быть не меньше времени прохождения данных по цепочке выход 27 - коммутатор 2 - блок 3 - вьиитатель 5 труппа 6 элементов И - блок 7. В результате этого нулевой код с выхода регистра 13 проходит через коммутатор 2 на вход блока 3, на выходе которого образуется код-(о) 1-2, поступающий на вход вьшитае- мого вычитателя 5. Если имеет место ....... то f(N)l -235

40

макс

и на выходе

вычитателя 5 должен быть отрицатель- ньм код, то при принятом способе вычитания (вычитаемое представляется отрицательным числом в дополнительном коде) переноса из старшего значащего разряда не возникает и полученная на выходе вычитателя 5 разность f(N) .f(o) через группу 6 не проходит, т.е. на входе блока 7 присутствует нулевой код, что соответствует значению F(o) на выходе блока 7, который принимается на регистр 8, с выхода которого

45

50

ряд сумматора 12, а также разрешается прием в регистр 15 из регистра 13. Таким образом, в регистре 13 находится код 00,,.000, который через коммутатор 11 проходит на cy мaтop 12 и складывается на нем с двоичным кодом входа 20 и единицей в младшем разряде на входе переноса, т.е. на информационном коде регистра 13 устанавливается код 00...0011. По этому импульсу СИ2 код 01 из счетчика 65 блока 19 управления переносится в регистр 66. В следующем такте открываются цепи приема в регистры 13 и 8, в результате чего в регистр 13 принимается код 00...011, которьш проходит на вход блока 3, на выходе которого формируется код f(3), на выходе вычитателя находится код f (N)--f (3)0. На выходе блока 7 в соответствии с изложенным формируется код Р(0,3), который принимается регистром 8 и по выходу 24 проходит на информационный

поступает на информационньй вход ком-,5 вход коммутатора 9. Поскольку в это мутат.ора 9, В это время на регистре время на его управляющем входе на- 66 блока 19 управления находится код ходится код 01, то код появляется начальной установки, который поступа- на выходе 21-2. По этому же импульсу ет с выхода 44 на управляющий вход СИ1 содержимое счетчика 65 блока 19

81996

коммутатора 9, в результате чего на выходе 21-1 выбирается код F(o), Если имеет место ..,, , то (N) l-2 и

МП ь с

на выходе вычнтателя получают код f(N)-f(o)0, Хотя в этом случае и появляется сигнал переноса из старшего разряда (00,..OOO+l1...111+00.,. ..оООО), код на вход блока

JQ 7 через группу 6 проходит также нулевой. Также по сигналу СИ1 импульс с выхода элемента И 55 блока 19 управления поступает на счетный вход счетчика 65, увеличивая его содержимое

15 на единицу, т.е. в данном случае в- счетчике 65 хранится код 01. Следующий за СИ1 импульс СИ2 поступает на вход установки в единичное состояние триггера 52 и на вход элемента И 56.

20 В первом случае единичный потенциал с выхода триггера проходит на выход 39, во втором случае соответствующий импульс проходит на выход 38. В результате этого коммутатор 11 перехо25 дит в состояние, соответствующее прохождению информации из регистра 15 на выход коммутат.ора 1 1 и далее на вход сумматора 12, группа 16 пропускает код входа 20 с выхода 29 на о второй вход сумматора 12, открывает- ся цепь входа переноса в младший раз5

0

5

0

ряд сумматора 12, а также разрешается прием в регистр 15 из регистра 13. Таким образом, в регистре 13 находится код 00,,.000, который через коммутатор 11 проходит на cy мaтop 12 и складывается на нем с двоичным кодом входа 20 и единицей в младшем разряде на входе переноса, т.е. на информационном коде регистра 13 устанавливается код 00...0011. По этому импульсу СИ2 код 01 из счетчика 65 блока 19 управления переносится в регистр 66. В следующем такте открываются цепи приема в регистры 13 и 8, в результате чего в регистр 13 принимается код 00...011, которьш проходит на вход блока 3, на выходе которого формируется код f(3), на выходе вычитателя находится код f (N)--f (3)0. На выходе блока 7 в соответствии с изложенным формируется код Р(0,3), который принимается регистром 8 и по выходу 24 проходит на информационный

управления также увеличивается на единицу описанным способом, в результате чего в нем устанавливается код 10, Следующий импульс СИ2 снова вырабатьшает положительный сигнал на выходе 38, по которому код 00,.0 принимается в регистр.15, а также переносит код 10 со счетчика 65 блока 19 управления в регистр 66 и с выхода 44 на управляющий вход коммутатора 9, В результате на входе регистра 13 находится код 00...110. Третий импульс .СИ1 пропускает этот код на вход блока 3, на выходе которого появляется код f(6), на выходе вычи- тателя 5 появляется разность f(N)- f(6), которая попадает на адресный вход блока.7, образуя на его выходе код F(0,6), который поступает на ин- формационньй вход коммутатора 9 и далее в соответствии с состоянием Ю на его управляющем входе на выход 21-3. При этом в счетчике 65 блока 19 устанавливается код 11, После третьего импульса СИ2 по четвертому импульсу СИ1 на информационном выходе 21-4 появляется код F(0,9 причем на счетчике 65 блока 19 управления снова устанавливается код 00, а также появляется сигнал переполнения счетчика. Указанный сигнал в блок8.19 устанавливает в единичное состояние триггер 53, Поскольку в схеме 17 сравнения коды не совпадают, триггер 54 блока 19 остается в нулевом состоянии В результате по сигналу переполнения на выходе элемента И 59 возникает импульс, который с выхода 37 проходит на счетньй вход счетчика 10, увеличивая его содержимое на единицу, т;е. в счетчике устанавливается код 00...001. Поскольку триггер 53 находится в единичном состоянии, то по очередному импульсу СИ2 на выходе элемента И 57 появляется сигнал, который через элемент ИЛИ 47 устанавливает триггеры f 50 и 52 в нулевое состояние, запрещая дальнейшую выработку сигналов разре- шения приема в регистры 13 и 8 по выходам 40 и 43 соответственно, а также устанавливает нулевой потенциал на выходе 39, разрешая прохождение информации со счетчика 10 через коммутатор 11 на вход сумматора 12 и запрещая прием кода с входа 20 через грзшпу 16 на вход сумматора 12 и прием сигнала переноса в младший разряд сумма

0

5

0

5

0

п

5

0

5

тора 12. Не вырабатывается сигнал,- разрешающий прием в регистр 15, вырабатываемый элементом И 56 блока 19. . В то же время по очередному импульсу СИ1 на выходе элемента И 60 блока 19 появляется сигнал, который через элемент ИЛИ 48 устанавливает триггер 53 в нулевое состояние На этом завершается первый такт работы цифрового формирователя функций. Следующий такт обработки начинается по приходу следующего сигнала Такт. Рассуждая таким образом, получим, что в очередном такте работы на выходы 21-1, 21-2, 21-3 и 21-4 будут выданы весовые функции F(0,l), F(0,4), F(0,7) H.F() соответственно. При этом ни в схеме 14 сравнения, ни в схеме 17 сравнения на рассмотренном этапе работы цифрового формирователя функций не.вырабатывается единичный сигнал. Рассмотренный такт работы заканчивается тем, что в счетчике 10 устанавливается код 00...010. Тогда уже после первого импульса .СИ1 относительно прихода третьего сигнала Такт в схеме 17 сравнения возникает единичный сигнал совпадения кодов, который по входу 34 устанавливает в блоке 19 управления триггер 54 в единичное состояние, в результате чего вместо единичного сигнала на выходе 37, увеличивающего на единицу содержимое счетчика 10, вырабатывается сигнал установки в нулевое состояние счетчика 10 по выходу 36. В этом такте по сигналам СИ на регистр 13 последовательно друг за другом принимаются коды 00...0010, 00...0101, 00...1000, 00..,1011. в последнем случае схема 14 сравнения вырабатьюает единичный сигнал, свидетельствующий о том, что соответствующего значения не существует. Поэтому указанный сигнал проходит на .ВХОД установки в нулев ое состояние регистра 8 и одновременно через инвертор 49 блока 19 на запрет выработки сигнала на-вход управления приемом регистра 8. Этим завершается один цикл работы цифрового формирователя функций, после чего по приходу следующего сигнала Такт по входу 46 процесс повторяется.

Формула изобретения

Цифровой формирователь функций, содержащий блок задания режима, пер

вый блок памяти, второй блок памя- THi. регистр функции, выходной коммутатор, счетчик, сумматор, регистр адреса, генератор импульсов и блок управления, причем выход регистра функции соединен с информационным входом выходного коммутатора, выходы которого соединены с выходом формирователя, отличающийся тем, что, с целью расширения области применения за счет формирования функций с произвольным шагом дискретности, в него введены коммутатор адреса, регистр вычитателя, вьгчитатель, две группы элементов И, коммутатор сумматора, две схемы сравнения, регистр сумматора, причем выход блока задания режима соединен с первым входом перво схемы сравнения и первым информацион- ным входом коммутатора адреса, второй информационный вход которого соединен с выходом регистра адреса, вторым входом первой схемы сравнения, первым входом второй схемы сравнения и информационным входом регистра сумматора, выход коммутатора адреса соединен с адресным входом нервного блока памяти, выход которого соединен с входом вычитаемого вычитателя и информационным входом регистра вычитателя, выход которого соединен с входом уменьшаемого вычитателя, выходы разрядов кода и переноса которого соединены соответственно с первыми входами соответствующих элементов И и вторыми входами элементов И первой группы, выходы которых соединены с адресным входом второго блока памяти, выход которого соединен с информационным входом регистра функции, выход счетчика соединен с первым информационным входом коммутатора сум матора, второй вход которого соединен с выходом регистра сумматора.

10

1520 -

819910

выход коммутатора сумматора соединен с входом первого слагаемого сумматора, выход которого соединен с информационным входом регистра адреса, вход переключения каналов формирователя соединен поразрядно с первыми входами соответствующих элементов И второй группы и вторым входом второй схемы сравнения, вход второго слагаемого сумматора поразрядно соединен с выходами элементов И второй группы, тактовый вход формирователя соединен с первым входом блока управления, второй вход которого соединен с входом сброса формирователя, выходы первой и второй тактовых последовательностей соединены соответственно с третьим и четвертым входами блока управле

ния, выход второй схемы сравнения соединен с пятым входом блока управления, шестой вход которого соединен с выходом первой схемы сравнения и входом установки регистра функции, первый выход блока управления соединен с входом установки в О счетчика, счетный вход которого соединен с вторым выходом блока управления, третий выход которого соединен с входом синхронизации регистра сумматора, четвертый выход блока управления соединен с входом переноса сумматора, управляющим входом коммутатора сумматора и вторыми входами элементов И второй группы, вход синхронизации регистра адреса соединен с пятым выходом блока управления, шестой, седьмой, восьмой и девятый выходы блока управления соединены соответственно с управляющим входом коммутатора адреса, входом синхронизации регистра вычитателя, входом синхронизации регистра функции и управляющим входом выходного коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления ленточным перфоратором | 1985 |

|

SU1310860A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для локального выравнивания гистограмм | 1986 |

|

SU1312614A1 |

| Устройство для управления ленточным перфоратором | 1982 |

|

SU1049934A1 |

| Микропрограммное устройство управления /его варианты/ | 1984 |

|

SU1242943A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Измерительный преобразователь длительности временных интервалов | 1985 |

|

SU1357913A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вывода информации | 1984 |

|

SU1238090A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных цифровых вычислительных системах , в частности, в системах конвейерной обработки сигналов РЛС , предназначенных для зондирования окружающей среды. Целью изобретения является расширение области применения. Это достигается тем, что в состав формирователя, включающего блок задания режима, два регистра, генератор импульсов, счетчик, блок управления, два блока памяти со специально занесенной в них информацией, сумматор и выходной коммутатор, введены вычитатель, два коммутатора, два регистра, две схемы сравнения 14 и 17, две группы 6 и 16 двухвходовых элементов И и определенные связи между указанными элементами. По сравнению с известными формирователями изобретение позволяет сделать его схемотехническое решение унифицированным, не зависящим от числа заданных для данного устройства шагов дискретности аргументов, причем эффективность подобного упрощения растет с увеличением числа шагов дискретности аргумента заданной функции. 3 ил.

| Функциональный генератор | 1984 |

|

SU1267395A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Формирователь сложной функции | 1985 |

|

SU1287135A1 |

Авторы

Даты

1989-09-15—Публикация

1988-01-18—Подача